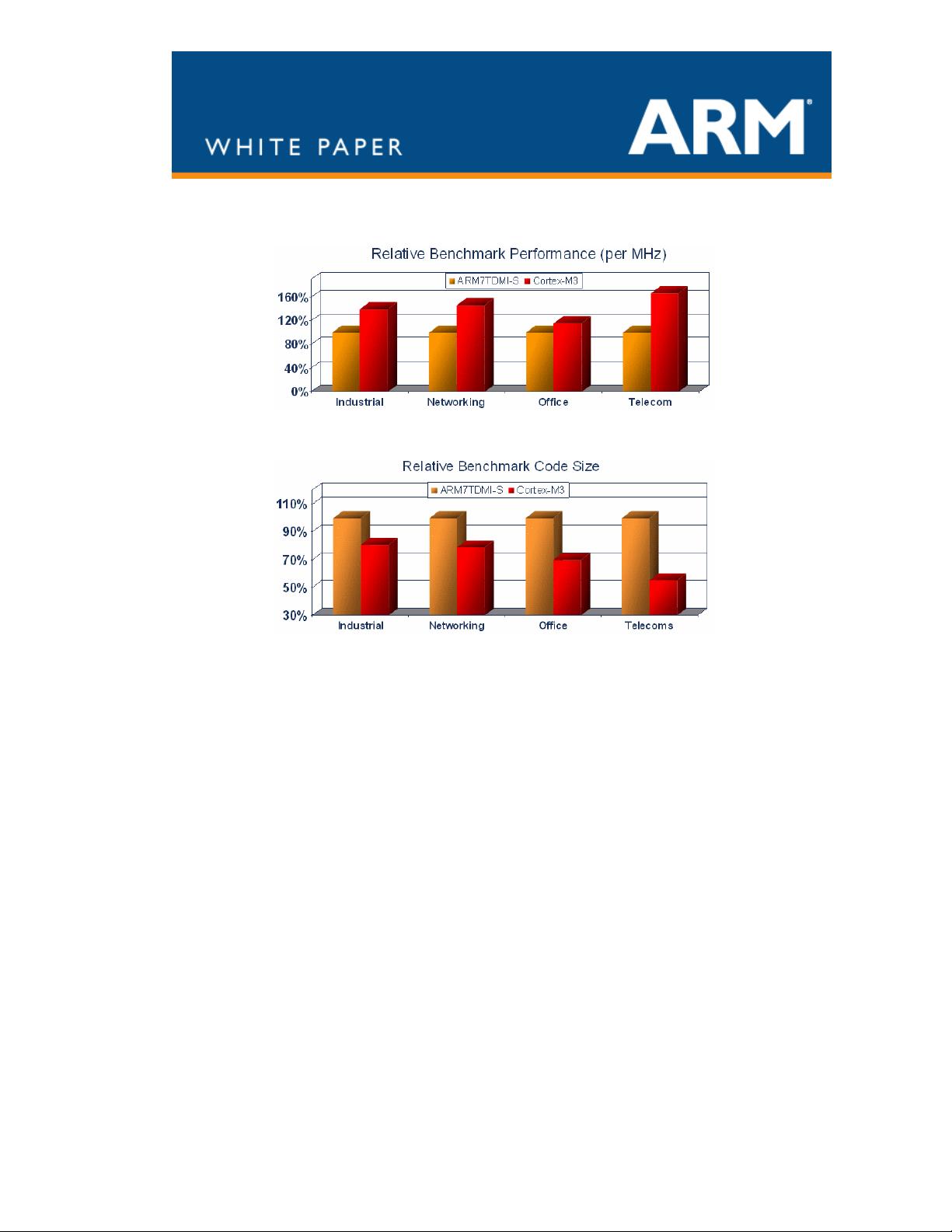

### 关于ARM Cortex-M3处理器的介绍 #### 一、引言 ARM Cortex-M3处理器是基于ARMv7-M架构的第一款处理器,旨在为多种嵌入式应用提供高性能且低功耗的解决方案。该处理器主要面向微控制器市场,但也适用于汽车车身系统、工业控制系统和无线网络等领域。 #### 二、ARM Cortex-M3处理器概述 ARM Cortex系列处理器根据其针对的应用场景不同分为三个主要的配置文件:A、R和M。其中,A配置文件针对的是运行复杂操作系统的高级应用;R配置文件针对实时系统;而M配置文件则专门优化用于成本敏感型和微控制器应用。Cortex-M3作为M配置文件的一部分,专注于实现高系统性能的同时保持较低的成本和功耗。 #### 三、通过提高效率实现更高性能 为了提高性能,处理器可以通过两种方式:一种是“努力工作”,即提高时钟频率;另一种是“聪明工作”,即在较低的时钟速度下提高计算效率。前者虽然可以增加性能,但同时也会带来更高的功耗和设计复杂度。相比之下,后者可以在不影响性能的情况下降低功耗和简化设计。 Cortex-M3处理器的核心采用了先进的三级流水线结构,并且基于哈佛架构设计。此外,它还包含了许多创新特性,如分支预测、单周期乘法和硬件除法等,这些特性共同使得处理器能够达到每兆赫兹1.25 DMIPS的Dhrystone基准性能。 #### 四、Thumb-2指令集架构 Cortex-M3处理器实现了新的Thumb-2指令集架构,这使得它在执行Thumb指令时比ARM7TDMI-S处理器高效70%,而在执行ARM指令时也比ARM7TDMI-S高效35%,针对Dhrystone基准测试而言。Thumb-2指令集不仅提供了更多的指令,还改进了编码效率,从而减少了代码大小,进一步降低了功耗。 #### 五、简化编程和快速高效的应用开发 Cortex-M3处理器的设计重点之一在于简化编程,以帮助开发者更快速地进行应用开发。这主要体现在以下几个方面: 1. **易于使用的开发工具**:ARM提供了丰富的开发工具链,包括编译器、调试器和仿真器等,这些工具支持高效的软件开发。 2. **集成开发环境**:ARM Keil MDK是一款广泛使用的集成开发环境,它支持Cortex-M3处理器,提供了强大的调试和分析功能。 3. **代码重用与移植性**:由于Cortex-M3处理器遵循ARMv7-M架构标准,因此与其他ARM处理器之间的代码重用性和移植性较好。 4. **社区支持**:ARM拥有庞大的开发者社区,提供了大量的技术文档、示例代码和技术支持资源。 #### 六、目标市场与应用场景 Cortex-M3处理器主要针对以下市场和应用场景: - **微控制器**:广泛应用于各种嵌入式设备中,如智能家居、消费电子等。 - **汽车电子**:例如车身控制系统、安全系统等。 - **工业自动化**:例如机器人控制、传感器网络等。 - **无线通信**:如蓝牙模块、Wi-Fi设备等。 ARM Cortex-M3处理器以其卓越的性能、低功耗特性和易于使用的特性,在嵌入式系统领域占据了重要的位置。无论是对于专业开发者还是初学者来说,Cortex-M3都是一种理想的选择。

剩余16页未读,继续阅读

zsh74352014-08-25很好,可用。

zsh74352014-08-25很好,可用。

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- SourceTreeSetup-3.4.17

- 20241226幼儿园.pdf

- 清华大学AI自强项目课件以及代码下载,黑龙江大学机器学习小组学习历程 @清华大学数据院,感谢他们的课件以及源码.zip

- 基于优化特征提取和机器学习的人脸识别-Face Recognition Using Optimized Feature Extraction and ML

- 清华大学计算机辅修数据结构作业(2015春季学期).zip

- COMSOL【电磁-流-热耦合】仿真 comsol平台下的变压器二维模型的电磁-流-热耦合仿真,仿真效果如下所示 计算时间根据网格划分的粗细程度在1-3小时不等 简单易操作,保证到手可跑出

- 车对车(V2V)充电调度问题-matlab-Charge Scheduling Problems Vehicle-to-Vehicle (V2V)

- Ini文档读写,包含各种value

- 爬取BOSS直聘网站的招聘数据,用于后续的大数据处理分析, 爬虫招聘网站, pandas finebi.zip

- Inet-Download-Manager-6.38-Build-18最稳定无弹窗

- 正弦逆变器-Sine Inverter-matlab

- 交错无桥PFC整流器-Interleaved Bridgeless PFC Rectifier-matlab

- 电子书 区块链 多线程资料

- 前端分析-2023071100789

- 1.电力系统输电线路距离保护的建模与仿真matlab simulink仿真模型 2.方向阻抗继电器 (1)“0度接线”方向阻抗继电器的构造 (2)“相电压和具有K3I0补偿的相电流接线”的方向阻抗继电

- 用于将大量的数据进行分片分页分批处理的通用处理框架.zip

信息提交成功

信息提交成功