1

1

2

2

3

3

4

4

D D

C C

B B

A A

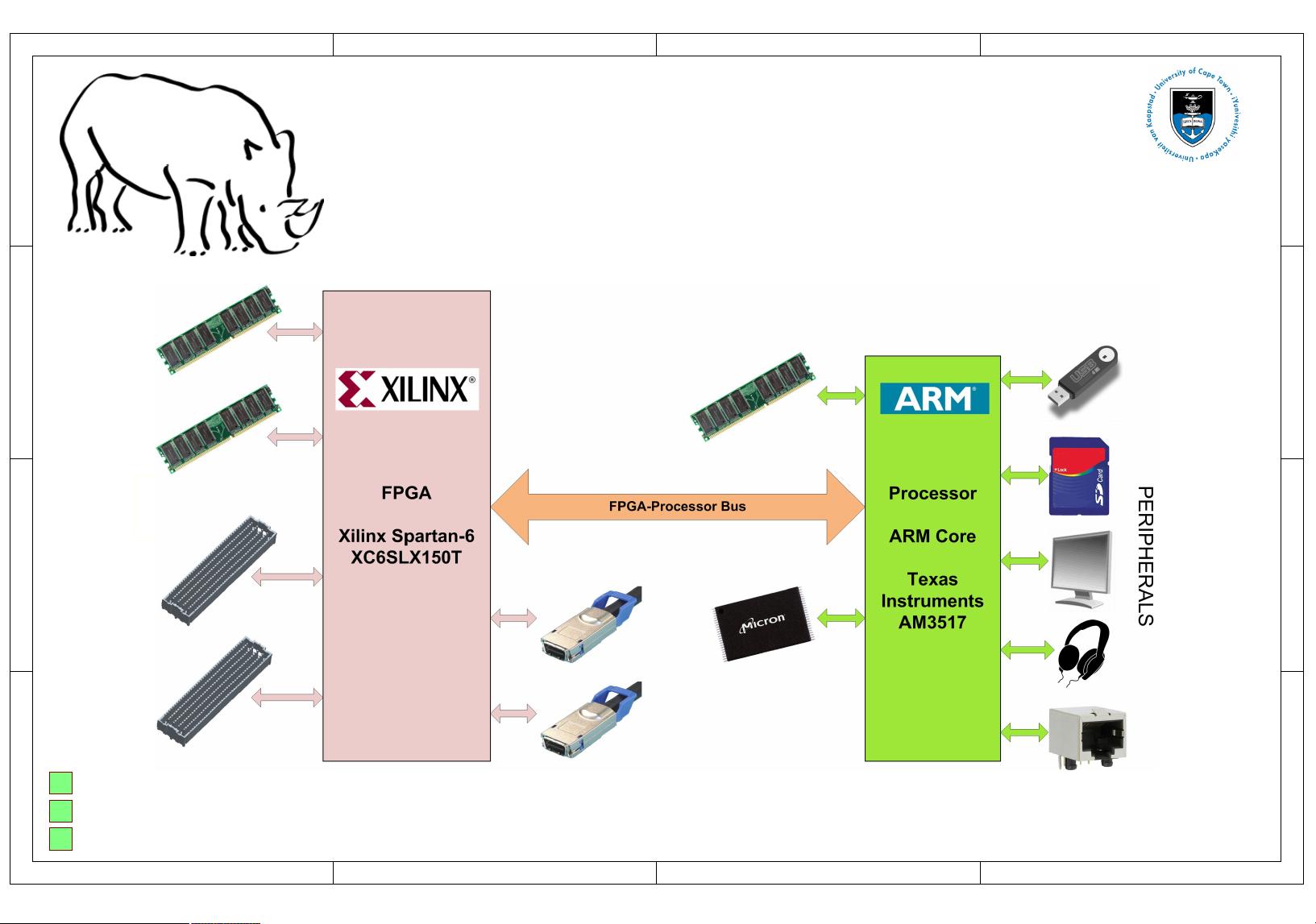

rhino_top_level

RHINO

Reconfigurable Hardware Interface for computatioN and radiO

Schematics

UCT SDR Research Group

Published: 19/09/2012

Revision: 1.2

(C) 2011 Alan Langman and Simon Scott

rhino_power_distrib

rhino_contents

1

1

2

2

3

3

4

4

D D

C C

B B

A A

Table of Contents

Page PageSchematic Schematic

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

Table of Contents

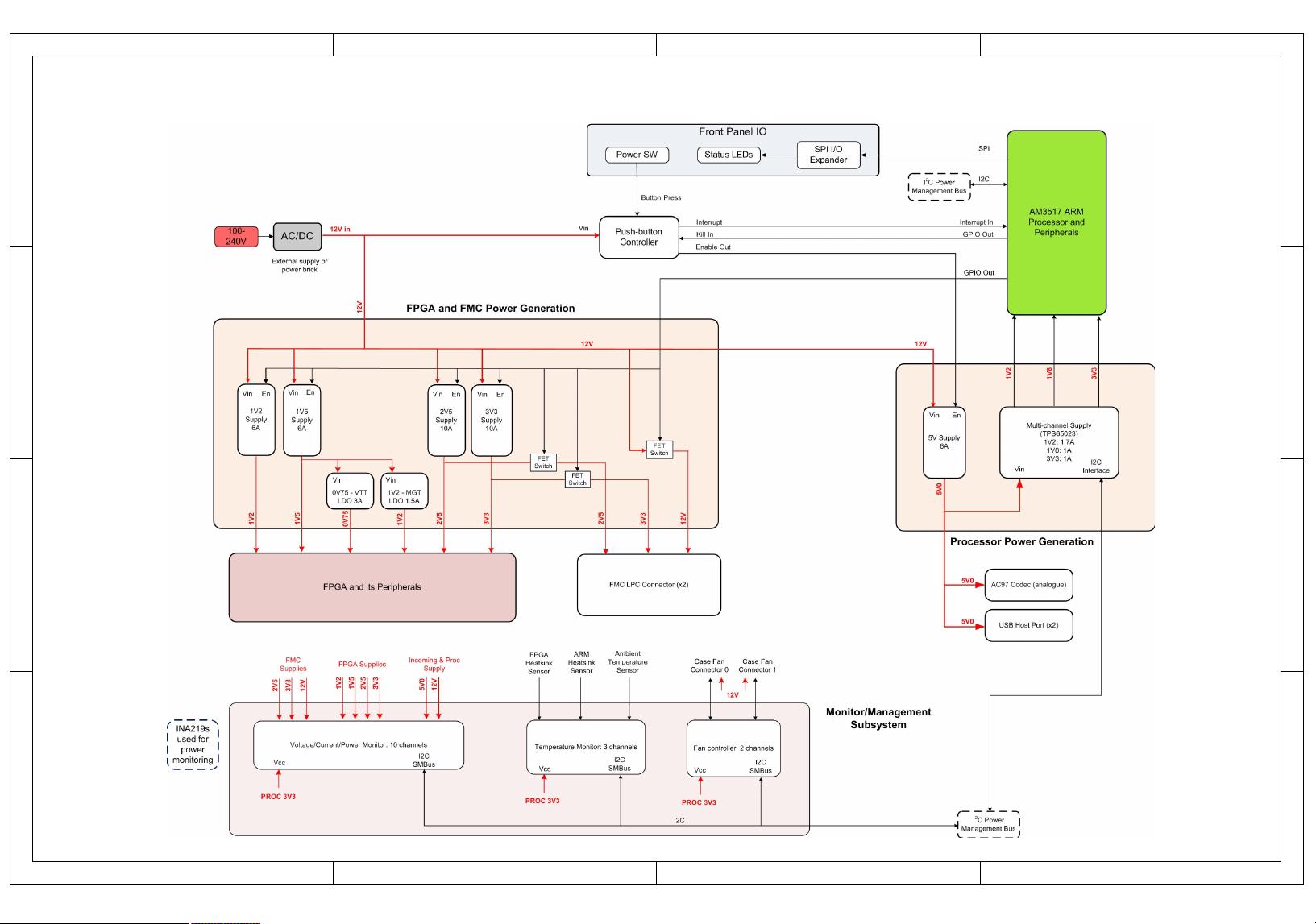

Rhino Power Distribution and Monitoring

Rhino Overview

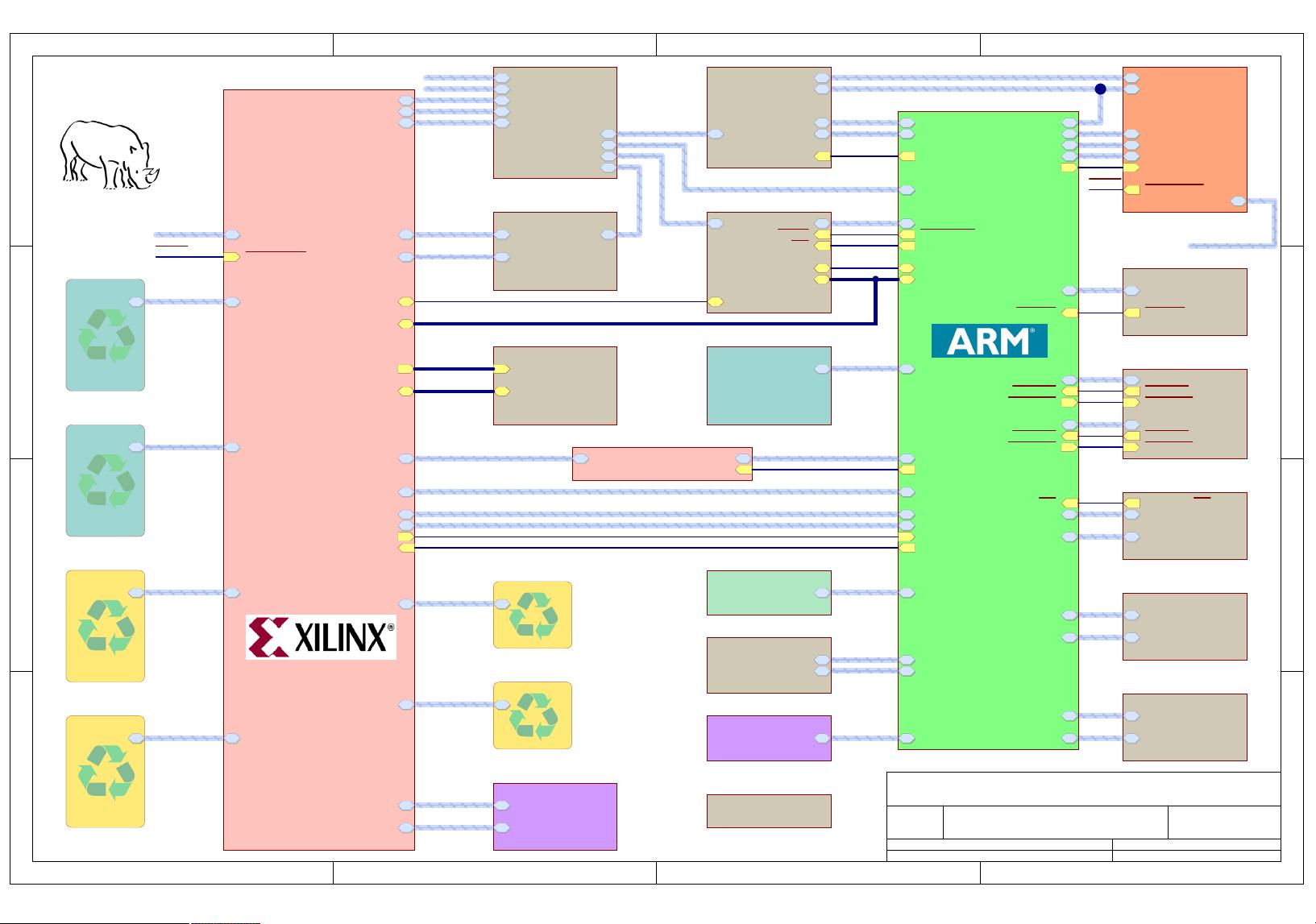

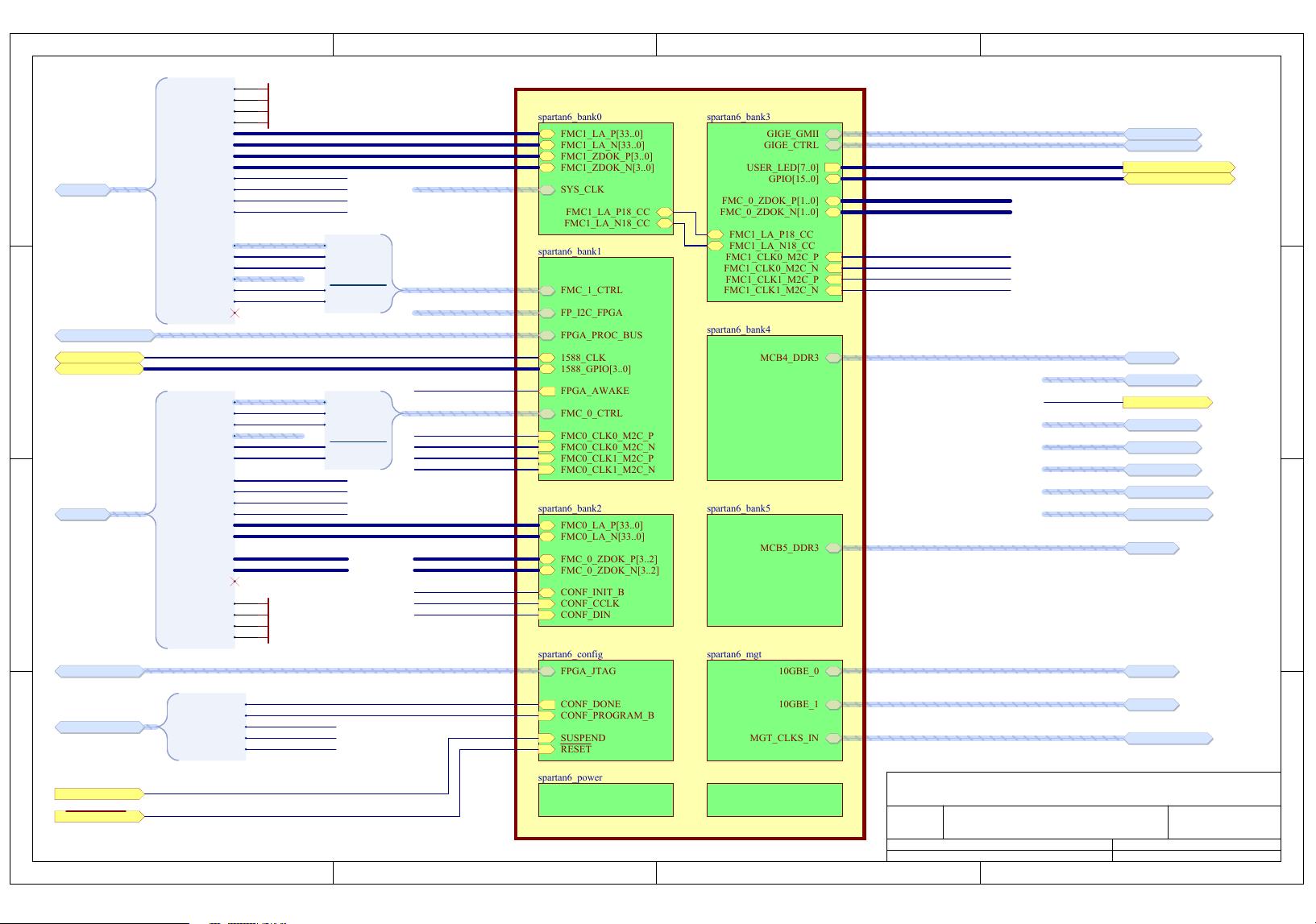

Spartan-6 (top level)

Spartan-6 Bank 0

Spartan-6 Bank 1

Dual LVDS Receiver 0

Spartan-6 Bank 2

Spartan-6 Bank 3

Dual LVDS Receiver 1

Spartan-6 Bank 4

Spartan-6 Bank 5

Spartan-6 Multi-Gigabit Transceivers

Spartan-6 Configuration

Spartan-6 Power

Spartan-6 Supply Decoupling Caps

DDR3 RAM 0

DDR3 RAM 1

FMC 0 HPC Connector (top-level)

FMC 1 HPC Connector (top-level)

FMC 0 HPC Connector (Rows A, B, C, D)

FMC 1 HPC Connector (Rows A, B, C, D)

FMC 0 HPC Connector (Rows E, F, G, H)

FMC 1 HPC Connector (Rows E, F, G, H)

FMC 0 HPC Connector (Rows J, K and Ground)

FMC 1 HPC Connector (Rows J, K and Ground)

CX4 10Gbps Ethernet Connector 0

CX4 10Gbps Ethernet Connector 1

1 Gbps Ethernet PHY

Spartan-6 GPIO Header and LEDs

Spartan-6 Clocks

AM3517 (top-level)

AM3517 Peripherals (Part A)

AM3517 Peripherals (Part B)

AM3517 Power

AM3517 Supply Decoupling Caps

AM3517 DDR2 RAM (top level)

DDR2 RAM 0

DDR2 RAM 1

NAND Flash

100Mbps Ethernet PHY

RS-232 Header for Peripherals

AM3517 Clocks

USB On-the-Go

USB Host Transceivers

SD Card and Real-time Clock

HDMI Video Transmitter

Audio

USB to JTAG/I2C/RS-232

JTAG Chain

Configuration Interface Level Translator

Power Supply Management

Spartan-6 Power Supplies

Spartan-6 LDO Power Supplies

FMC Power Supply Switches

Si6463BDQ FET Load Switch 0

Si6463BDQ FET Load Switch 1

Si6463BDQ FET Load Switch 2

Si6463BDQ FET Load Switch 3

AM3517 Power Supply

Power Monitor

Temperature Monitor and Fan Controller

Power LEDs

Mounting Holes and Fiducials

1

1

2

2

3

3

4

4

D D

C C

B B

A A

Rhino Power Distribution and Monitoring

1

1

2

2

3

3

4

4

D D

C C

B B

A A

Title

Number RevisionSize

A4

Date: 19/09/2012 Sheet of

File: D:\Work\..\rhino_top_level.SchDoc Drawn By:

Rhino Overview

4 65

Simon Scott

1.0

Licensed under the TAPR Open

Hardware License

(www.tapr.org/OHL)

Project

RHINO

DDR3_BUS

ram_ddr3_0

DDR3_BUS

ram_ddr3_1

FMC_BUS

fmc_0

FMC_BUS

fmc_1

CX4_BUS

cx4_0

CX4_BUS

cx4_1

JTAGGMII

CTRL

1gbps_ethernet

USER_LED[7..0]

GPIO[15..0]

spartan6_gpio

DDR3_0

DDR3_1

FMC_0

FMC_1

CX4_0

CX4_1

FPGA_PROC_BUS

MGT_CLKS_IN

FPGA_CONFIG

FMC_0_CTRL

FMC_1_CTRL

SYS_CLK

FPGA_AWAKE

FPGA_JTAG

FMC_0_JTAG

FMC_1_JTAG

1588_CLK

1588_GPIO[3..0]

SUSPEND

GIGE_GMII

GIGE_CTRL

USER_LED[7..0]

GPIO[15..0]

FP_I2C_FPGA

FPGA_RESET

spartan6

DDR2

NAND

FPGA_PROC_BUS

SUPPLY_EN

PWR_KILL

I2C_PWR_MAN

PWR_WARNS

CLKS_IN

FPGA_CONFIG

INIT_B_DIR

ETH_RMII

ETH_RESET

ETH_PWRDWN

1588_CLK

1588_GPIO[3..0]

DBG_UART0

DBG_UART1

PROC_JTAG

USB_I2C_EN

FMC_0_CTRL

FMC_1_CTRL

FPGA_AWAKE

FPGA_SUSPEND

USB_OTG

HS_USB1

HS_USB2

DVI

DDC_I2C

OTG_OC

USB1_RST

USB2_RST

AUDIO_DATA

AUDIO_CTRL

SD_BUS

RTC_SPI

RTC_SQW/INT

RS232_DATA

RS232_CTRL

FP_SPI_PROC

USB1_OC

USB2_OC

am3517

PROC_DDR2_BUS

am3517_ram

JTAG RMII

RESET

PWRDWN/INT

1588_GPIO[3..0]

1588_CLK1

1588_CLK2

100mbps_ethernet

HS_USB1

HS_USB2

USB1_RST

USB2_RST

USB1_OC

USB2_OC

usb_host

DVI

DDC_I2C

video

AUDIO_CTRL

AUDIO_DATA

audio

SD_BUS

RTC_SPI

RTC_SQW/INT

sd_card_and_rtc

NAND_BUS

nand_flash

UART0

UART1

I2C

I2C_EN

FPGA_SUPPLY_EN

JTAG

usb_to_jtag_rs232

I2C_PWR_MAN

SUPPLY_EN

PWR_KILL

WARN_OUT

FP_SPI_PROC

FP_I2C_FPGA

FTDI_SUPPLY_EN

OVER_TEMP

pwr_supply_management

PROC_CLKS

am3517_clocks

MGT_CLKS

FPGA_SYS_CLK

spartan6_clocks

CONFIG_2V5 CONFIG_3V3

INIT_B_DIR

config_lvl_xlator

USB_OTG

OTG_OC

usb_otg

RS232_DATA

RS232_CTRL

periph_rs232

FP_I2C_FPGA

FP_I2C_FPGA

DDR3_0

DDR3_1

FMC_0

FMC_1

DDR2

FPGA_CONFIG_3V3FPGA_CONFIG_2V5

RHINO

Reconfigurable Hardware Interface

for computatioN and radiO

(C) 2011 Alan Langman and Simon Scott

FPGA_JTAG

FMC_0_JTAG

FMC_1_JTAG

PROC_JTAG

100M_JTAG

1G_JTAG

JTAG_MASTER

FMC_0_CTRL

FMC_1_CTRL

jtag_chain

FMC_0_CTRL

FMC_1_CTRL

FMC_0_CTRL

FMC_1_CTRL

OVR_T

OVR_T

mounting_holes_fids

1

1

2

2

3

3

4

4

D D

C C

B B

A A

Title

Number RevisionSize

A4

Date: 19/09/2012 Sheet of

File: D:\Work\..\spartan6.SchDoc Drawn By:

Spartan-6 (top-level)

5 65

Simon Scott

1.0

Licensed under the TAPR Open

Hardware License

(www.tapr.org/OHL)

Project

RHINO

FMC1_LA_P[33..0]

FMC1_LA_N[33..0]

FMC1_ZDOK_P[3..0]

FMC1_ZDOK_N[3..0]

SYS_CLK

FMC1_LA_P18_CC

FMC1_LA_N18_CC

spartan6_bank0

FPGA_PROC_BUS

FMC_0_CTRL

FMC_1_CTRL

FPGA_AWAKE

1588_CLK

1588_GPIO[3..0]

FP_I2C_FPGA

FMC0_CLK0_M2C_N

FMC0_CLK1_M2C_N

FMC0_CLK0_M2C_P

FMC0_CLK1_M2C_P

spartan6_bank1

FMC0_LA_P[33..0]

FMC0_LA_N[33..0]

CONF_DIN

CONF_CCLK

CONF_INIT_B

FMC_0_ZDOK_N[3..2]

FMC_0_ZDOK_P[3..2]

spartan6_bank2

FMC_0_ZDOK_N[1..0]

FMC_0_ZDOK_P[1..0]

GIGE_GMII

GIGE_CTRL

GPIO[15..0]

USER_LED[7..0]

FMC1_CLK0_M2C_N

FMC1_CLK1_M2C_N

FMC1_CLK0_M2C_P

FMC1_CLK1_M2C_P

FMC1_LA_P18_CC

FMC1_LA_N18_CC

spartan6_bank3

MCB4_DDR3

spartan6_bank4

MCB5_DDR3

spartan6_bank5

10GBE_0

10GBE_1

MGT_CLKS_IN

spartan6_mgt

CONF_PROGRAM_B

CONF_DONE

FPGA_JTAG

SUSPEND

RESET

spartan6_config

spartan6_power

DDR3_0

DDR3_1

FMC_1

FMC_0

CX4_1

FPGA_PROC_BUS

CX4_0

spartan6_decoupling

MGT_CLKS_IN

LA_P[33..0]

LA_N[33..0]

ZDOK_P[3..0]

ZDOK_N[3..0]

CLK0_M2C_P

CLK0_M2C_N

CLK1_M2C_P

CLK1_M2C_N

I2C

GA0

GA1

JTAG

PRSNT_M2C_L

PG_C2M

VREF_A_M2C

VADJ

3P3VAUX

3P3V

12P0V

FMC_BUS

LA_P[33..0]

LA_N[33..0]

ZDOK_P[3..0]

ZDOK_N[3..0]

I2C

GA0

GA1

JTAG

PRSNT_M2C_L

PG_C2M

VREF_A_M2C

VADJ

3P3VAUX

3P3V

12P0V

CLK0_M2C_P

CLK0_M2C_N

CLK1_M2C_P

CLK1_M2C_N

FMC_BUS

VCC_AUX_FMC1

VCC_3V3_FMC1

VCC_12V_FMC1

VCC_2V5_FMC1

DONE

PROGRAM_B

INIT_B

CCLK

DIN

FPGA_CONFIG_BUS

FPGA_CONFIG

FMC_0_ZDOK_P[3..0]

FMC_0_ZDOK_N[3..0]

VCC_AUX_FMC0

VCC_3V3_FMC0

VCC_12V_FMC0

VCC_2V5_FMC0

CONF_INIT_B

CONF_CCLK

CONF_DIN

CONF_INIT_B

CONF_CCLK

CONF_DIN

I2C

GA0

GA1

PRSNT_M2C

PG_C2M

FMC_0_CTRL

I2C

GA0

GA1

PRSNT_M2C

PG_C2M

FMC_1_CTRL

SYS_CLK

SYS_CLK

SYS_CLK

FPGA_AWAKE

FPGA_AWAKE

FPGA_AWAKE

FMC_0_ZDOK_P[1..0]

FMC_0_ZDOK_N[1..0]

FPGA_JTAG

FMC_0_JTAG

FMC_1_JTAG

1588_CLK

1588_GPIO[3..0]

SUSPEND

GIGE_CTRL

GIGE_GMII

USER_LED[7..0]

GPIO[15..0]

FP_I2C_FPGA

FPGA_RESET

FMC_0_ZDOK_P[3..2]

FMC_0_ZDOK_N[3..2]

FMC0_CLK0_M2C_P

FMC0_CLK0_M2C_N

FMC0_CLK1_M2C_P

FMC0_CLK1_M2C_N

FMC0_CLK0_M2C_P

FMC0_CLK0_M2C_N

FMC0_CLK1_M2C_P

FMC0_CLK1_M2C_N

FMC1_CLK0_M2C_P

FMC1_CLK0_M2C_N

FMC1_CLK1_M2C_P

FMC1_CLK1_M2C_N

FMC1_CLK0_M2C_P

FMC1_CLK0_M2C_N

FMC1_CLK1_M2C_P

FMC1_CLK1_M2C_N

FMC_0_CTRL

FMC_1_CTRL

FMC_0_CTRL

FMC_1_CTRL

FMC_0_JTAG

FMC_1_JTAG

FMC_0_JTAG

FMC_1_JTAG

FP_I2C_FPGA

FP_I2C_FPGA

PINET0TIE101 PINET0TIE102

CONET0TIE1

PINET0TIE201 PINET0TIE202

CONET0TIE2

PINET0TIE301 PINET0TIE302

CONET0TIE3

PINET0TIE401 PINET0TIE402

CONET0TIE4

PINET0TIE501 PINET0TIE502

CONET0TIE5

PINET0TIE601 PINET0TIE602

CONET0TIE6

PINET0TIE701 PINET0TIE702

CONET0TIE7

PINET0TIE801 PINET0TIE802

CONET0TIE8

PO15880CLK

PO15880GPIO0PO15880GPIO1PO15880GPIO2PO15880GPIO3

PO15880GPIO030000

POCX400

POCX4000RX00NPOCX4000RX00PPOCX4000RX10NPOCX4000RX10PPOCX4000RX20NPOCX4000RX20PPOCX4000RX30NPOCX4000RX30PPOCX4000TX00NPOCX4000TX00PPOCX4000TX10NPOCX4000TX10PPOCX4000TX20NPOCX4000TX20PPOCX4000TX30NPOCX4000TX30P

POCX401

POCX4010RX00NPOCX4010RX00PPOCX4010RX10NPOCX4010RX10PPOCX4010RX20NPOCX4010RX20PPOCX4010RX30NPOCX4010RX30PPOCX4010TX00NPOCX4010TX00PPOCX4010TX10NPOCX4010TX10PPOCX4010TX20NPOCX4010TX20PPOCX4010TX30NPOCX4010TX30P

PODDR300

PODDR3000A0PODDR3000A1PODDR3000A2PODDR3000A3PODDR3000A4PODDR3000A5PODDR3000A6PODDR3000A7PODDR3000A8PODDR3000A9

PODDR3000A10PODDR3000A11PODDR3000A12PODDR3000A13

PODDR3000A0130000

PODDR3000BA0PODDR3000BA1PODDR3000BA2

PODDR3000BA020000

PODDR3000C\A\S\

PODDR3000CK0NPODDR3000CK0P

PODDR3000CKEPODDR3000DQ0PODDR3000DQ1PODDR3000DQ2PODDR3000DQ3PODDR3000DQ4PODDR3000DQ5PODDR3000DQ6PODDR3000DQ7PODDR3000DQ8PODDR3000DQ9

PODDR3000DQ10PODDR3000DQ11PODDR3000DQ12PODDR3000DQ13PODDR3000DQ14PODDR3000DQ15

PODDR3000DQ0150000

PODDR3000LDM

PODDR3000LDQS0NPODDR3000LDQS0P

PODDR3000ODT

PODDR3000R\A\S\

PODDR3000R\E\S\E\T\

PODDR3000UDM

PODDR3000UDQS0NPODDR3000UDQS0P

PODDR3000W\E\

PODDR301

PODDR3010A0PODDR3010A1PODDR3010A2PODDR3010A3PODDR3010A4PODDR3010A5PODDR3010A6PODDR3010A7PODDR3010A8PODDR3010A9

PODDR3010A10PODDR3010A11PODDR3010A12PODDR3010A13

PODDR3010A0130000

PODDR3010BA0PODDR3010BA1PODDR3010BA2

PODDR3010BA020000

PODDR3010C\A\S\

PODDR3010CK0NPODDR3010CK0P

PODDR3010CKEPODDR3010DQ0PODDR3010DQ1PODDR3010DQ2PODDR3010DQ3PODDR3010DQ4PODDR3010DQ5PODDR3010DQ6PODDR3010DQ7PODDR3010DQ8PODDR3010DQ9

PODDR3010DQ10PODDR3010DQ11PODDR3010DQ12PODDR3010DQ13PODDR3010DQ14PODDR3010DQ15

PODDR3010DQ0150000

PODDR3010LDM

PODDR3010LDQS0NPODDR3010LDQS0P

PODDR3010ODT

PODDR3010R\A\S\

PODDR3010R\E\S\E\T\

PODDR3010UDM

PODDR3010UDQS0NPODDR3010UDQS0P

PODDR3010W\E\

POF\P\G\A\0\R\E\S\E\T\

POFMC00

POFMC0003P3V

POFMC0003P3VAUX

POFMC00012P0V

POFMC000CLK00M2C0NPOFMC000CLK00M2C0PPOFMC000CLK10M2C0NPOFMC000CLK10M2C0P

POFMC000GA0POFMC000GA1POFMC000I2C

POFMC000I2C0SCLPOFMC000I2C0SDA

POFMC000JTAG

POFMC000JTAG0T\R\S\T\

POFMC000JTAG0TCKPOFMC000JTAG0TDIPOFMC000JTAG0TDOPOFMC000JTAG0TMS

POFMC000LA0N0POFMC000LA0N1POFMC000LA0N2POFMC000LA0N3POFMC000LA0N4POFMC000LA0N5POFMC000LA0N6POFMC000LA0N7POFMC000LA0N8POFMC000LA0N9

POFMC000LA0N10POFMC000LA0N11POFMC000LA0N12POFMC000LA0N13POFMC000LA0N14POFMC000LA0N15POFMC000LA0N16POFMC000LA0N17POFMC000LA0N18POFMC000LA0N19POFMC000LA0N20POFMC000LA0N21POFMC000LA0N22POFMC000LA0N23POFMC000LA0N24POFMC000LA0N25POFMC000LA0N26POFMC000LA0N27POFMC000LA0N28POFMC000LA0N29POFMC000LA0N30POFMC000LA0N31POFMC000LA0N32POFMC000LA0N33

POFMC000LA0N0330000

POFMC000LA0P0POFMC000LA0P1POFMC000LA0P2POFMC000LA0P3POFMC000LA0P4POFMC000LA0P5POFMC000LA0P6POFMC000LA0P7POFMC000LA0P8POFMC000LA0P9

POFMC000LA0P10POFMC000LA0P11POFMC000LA0P12POFMC000LA0P13POFMC000LA0P14POFMC000LA0P15POFMC000LA0P16POFMC000LA0P17POFMC000LA0P18POFMC000LA0P19POFMC000LA0P20POFMC000LA0P21POFMC000LA0P22POFMC000LA0P23POFMC000LA0P24POFMC000LA0P25POFMC000LA0P26POFMC000LA0P27POFMC000LA0P28POFMC000LA0P29POFMC000LA0P30POFMC000LA0P31POFMC000LA0P32POFMC000LA0P33

POFMC000LA0P0330000

POFMC000PG0C2M

POFMC000PRSNT0M2C0L

POFMC000VADJ

POFMC000VREF0A0M2C

POFMC000ZDOK0N0POFMC000ZDOK0N1POFMC000ZDOK0N2POFMC000ZDOK0N3

POFMC000ZDOK0N030000

POFMC000ZDOK0P0POFMC000ZDOK0P1POFMC000ZDOK0P2POFMC000ZDOK0P3

POFMC000ZDOK0P030000

POFMC000CTRL

POFMC000CTRL0GA0POFMC000CTRL0GA1

POFMC000CTRL0I2C0SCLPOFMC000CTRL0I2C0SDA

POFMC000CTRL0P\R\S\N\T\0\M\2\C\

POFMC000CTRL0PG0C2M

POFMC01

POFMC0103P3V

POFMC0103P3VAUX

POFMC01012P0V

POFMC010CLK00M2C0NPOFMC010CLK00M2C0PPOFMC010CLK10M2C0NPOFMC010CLK10M2C0P

POFMC010GA0POFMC010GA1POFMC010I2C

POFMC010I2C0SCLPOFMC010I2C0SDA

POFMC010JTAG

POFMC010JTAG0T\R\S\T\

POFMC010JTAG0TCKPOFMC010JTAG0TDIPOFMC010JTAG0TDOPOFMC010JTAG0TMS

POFMC010LA0N0POFMC010LA0N1POFMC010LA0N2POFMC010LA0N3POFMC010LA0N4POFMC010LA0N5POFMC010LA0N6POFMC010LA0N7POFMC010LA0N8POFMC010LA0N9

POFMC010LA0N10POFMC010LA0N11POFMC010LA0N12POFMC010LA0N13POFMC010LA0N14POFMC010LA0N15POFMC010LA0N16POFMC010LA0N17POFMC010LA0N18POFMC010LA0N19POFMC010LA0N20POFMC010LA0N21POFMC010LA0N22POFMC010LA0N23POFMC010LA0N24POFMC010LA0N25POFMC010LA0N26POFMC010LA0N27POFMC010LA0N28POFMC010LA0N29POFMC010LA0N30POFMC010LA0N31POFMC010LA0N32POFMC010LA0N33

POFMC010LA0N0330000

POFMC010LA0P0POFMC010LA0P1POFMC010LA0P2POFMC010LA0P3POFMC010LA0P4POFMC010LA0P5POFMC010LA0P6POFMC010LA0P7POFMC010LA0P8POFMC010LA0P9

POFMC010LA0P10POFMC010LA0P11POFMC010LA0P12POFMC010LA0P13POFMC010LA0P14POFMC010LA0P15POFMC010LA0P16POFMC010LA0P17POFMC010LA0P18POFMC010LA0P19POFMC010LA0P20POFMC010LA0P21POFMC010LA0P22POFMC010LA0P23POFMC010LA0P24POFMC010LA0P25POFMC010LA0P26POFMC010LA0P27POFMC010LA0P28POFMC010LA0P29POFMC010LA0P30POFMC010LA0P31POFMC010LA0P32POFMC010LA0P33

POFMC010LA0P0330000

POFMC010PG0C2M

POFMC010PRSNT0M2C0L

POFMC010VADJ

POFMC010VREF0A0M2C

POFMC010ZDOK0N0POFMC010ZDOK0N1POFMC010ZDOK0N2POFMC010ZDOK0N3

POFMC010ZDOK0N030000

POFMC010ZDOK0P0POFMC010ZDOK0P1POFMC010ZDOK0P2POFMC010ZDOK0P3

POFMC010ZDOK0P030000

POFMC010CTRL

POFMC010CTRL0GA0POFMC010CTRL0GA1

POFMC010CTRL0I2C0SCLPOFMC010CTRL0I2C0SDA

POFMC010CTRL0P\R\S\N\T\0\M\2\C\

POFMC010CTRL0PG0C2M

POFP0I2C0FPGA

POFP0I2C0FPGA0SCLPOFP0I2C0FPGA0SDA

POFPGA0AWAKE

POFPGA0CONFIG

POFPGA0CONFIG0CCLK

POFPGA0CONFIG0DIN

POFPGA0CONFIG0DONE

POFPGA0CONFIG0INIT0B

POFPGA0CONFIG0PROGRAM0B

POFPGA0JTAG

POFPGA0JTAG0T\R\S\T\

POFPGA0JTAG0TCKPOFPGA0JTAG0TDIPOFPGA0JTAG0TDOPOFPGA0JTAG0TMS

POFPGA0PROC0BUS

POFPGA0PROC0BUS0A1POFPGA0PROC0BUS0A2POFPGA0PROC0BUS0A3POFPGA0PROC0BUS0A4POFPGA0PROC0BUS0A5POFPGA0PROC0BUS0A6POFPGA0PROC0BUS0A7POFPGA0PROC0BUS0A8POFPGA0PROC0BUS0A9

POFPGA0PROC0BUS0A10

POFPGA0PROC0BUS0A0100010

POFPGA0PROC0BUS0A\D\V\0ALE

POFPGA0PROC0BUS0BUSY0POFPGA0PROC0BUS0BUSY1

POFPGA0PROC0BUS0C\S\0\POFPGA0PROC0BUS0C\S\1\

POFPGA0PROC0BUS0C\S\2\0D\M\A\R\E\Q\0\

POFPGA0PROC0BUS0C\S\3\

POFPGA0PROC0BUS0C\S\4\0D\M\A\R\E\Q\1\POFPGA0PROC0BUS0C\S\5\0D\M\A\R\E\Q\2\

POFPGA0PROC0BUS0C\S\6\0IODIR

POFPGA0PROC0BUS0CLK

POFPGA0PROC0BUS0D0POFPGA0PROC0BUS0D1POFPGA0PROC0BUS0D2POFPGA0PROC0BUS0D3POFPGA0PROC0BUS0D4POFPGA0PROC0BUS0D5POFPGA0PROC0BUS0D6POFPGA0PROC0BUS0D7POFPGA0PROC0BUS0D8POFPGA0PROC0BUS0D9

POFPGA0PROC0BUS0D10POFPGA0PROC0BUS0D11POFPGA0PROC0BUS0D12POFPGA0PROC0BUS0D13POFPGA0PROC0BUS0D14POFPGA0PROC0BUS0D15

POFPGA0PROC0BUS0D0150000

POFPGA0PROC0BUS0O\E\POFPGA0PROC0BUS0W\E\POFPGA0PROC0BUS0W\P\

POGIGE0CTRL

POGIGE0CTRL0COMA

POGIGE0CTRL0I\N\T\

POGIGE0CTRL0MDC

POGIGE0CTRL0MDIO

POGIGE0CTRL0R\E\S\E\T\

POGIGE0GMII

POGIGE0GMII0COLPOGIGE0GMII0CRS

POGIGE0GMII0GTX0CLK

POGIGE0GMII0RX0CLK

POGIGE0GMII0RX0DVPOGIGE0GMII0RX0ER

POGIGE0GMII0RXD0POGIGE0GMII0RXD1POGIGE0GMII0RXD2POGIGE0GMII0RXD3POGIGE0GMII0RXD4POGIGE0GMII0RXD5POGIGE0GMII0RXD6POGIGE0GMII0RXD7

POGIGE0GMII0TX0CLK

POGIGE0GMII0TX0ENPOGIGE0GMII0TX0ER

POGIGE0GMII0TXD0POGIGE0GMII0TXD1POGIGE0GMII0TXD2POGIGE0GMII0TXD3POGIGE0GMII0TXD4POGIGE0GMII0TXD5POGIGE0GMII0TXD6POGIGE0GMII0TXD7

POGPIO0POGPIO1POGPIO2POGPIO3POGPIO4POGPIO5POGPIO6POGPIO7POGPIO8POGPIO9

POGPIO10POGPIO11POGPIO12POGPIO13POGPIO14POGPIO15

POGPIO0150000

POMGT0CLKS0IN

POMGT0CLKS0IN0MGT0CLK00NPOMGT0CLKS0IN0MGT0CLK00PPOMGT0CLKS0IN0MGT0CLK10NPOMGT0CLKS0IN0MGT0CLK10P

POSUSPEND

POSYS0CLK

POSYS0CLK0SYS0CLK0NPOSYS0CLK0SYS0CLK0P

POUSER0LED0POUSER0LED1POUSER0LED2POUSER0LED3POUSER0LED4POUSER0LED5POUSER0LED6POUSER0LED7

POUSER0LED070000