没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

FPGA/CPLD 开发

简明教程

含

GW48-CK

型 EDA 实验开发系统使用说明

杭州康芯电子有限公司

0571-88212487

www.electron-rnd.com

- 1 -

目 录

第一章 GW48-CK 系统使用说明

第一节 GW48-CK 教学实验系统原理与

使用介绍

第二节 实验电路结构图

第三节 GW48 系统结构图信号名与芯片

引脚对照表

第二章 GWDVP 电子设计开发板

使用说明

第三章 ispLSI1032 结构介绍

第四章 EDA 软件安装

第五章 ABEL-HDL 基本元素与

语言结构

第一节 ABEL-HDL 基本元素

第二节 ABEL-HDL 基本语言结构

第三节 ABEL-HDL 基本语句用法

第四节 常用指示字

第五节 ABEL-HDL 程序设计技巧

第六章 ABEL-HDL 设计实例

6-1 四位双向三态缓冲器

6-2 四位加/减法可控计数器

6-3 四位比较器

6-4 七位序列检测器

6-5 五位可变模计数器

6-6 五功能逻辑笔

第七章 ispEXPERT/SYNARIO

编译控制方法

第一节 ABEL-HDL 属性设置控制方法

第二节 Synario 原理图逻辑属性设置

第三节 Synario 逻辑适配属性设置方法

第四节 ispLSI 优化设计向导

第五节 ABEL-HDL 设计的点扩展

第八章 在系统编程下载方式

第九章 ispEXPERT/SYNARIO 结构

概述

第十章 ispEXPERT 应用向导

第十一章 数字系统设计示例

11-1 英语字母显示电路

11-2 8 位加法器

11-3 8 位乘法器

11-4 序列检测器

11-5 正负脉宽数控调制信号发生器

第十二章 EDA/VHDL 实验

培训讲义

第十三章 GWDD6-C 型通用编

程下载器使用说明

第一章 GW48-CK 系统使用说明

第一节 GW48-CK 教学实验系统原理与使用介绍

一

GW48-CK 系统使用注意事项

a 闲置不用 GW48-CK EDA 系统时 关闭电源 拔下电源插头

b EDA 软件安装方法可参见光盘中相应目录中的中文 README.TXT 详细使用方法

可参阅本书或 VHDL 实用教程 中的相关章节

c 在实验中 当选中某种模式后 要按一下复位键 以使系统正式进入该模式工作

d 换目标芯片时要特别注意 不要插反或插错 也不要带电插拔 确信插对后才能开

电源 其它接插口都可带电插拔

e 若进行 DAC0832 接口实验 需自行提供-/+12V 电源 接入时 请特别注意极性

f 系统板上的空插座是为单片机 AT89C2051 准备的 除非进行单片机与 FPGA/CPLD 的接

口实验和开发 平时在此座上不允许插有任何器件 以免与系统上的其它电路发生冲突 单

片机与系统的连接情况可参阅以下的附图 2-13 该单片机和相应的编程器需自备或另购

g

对 CPLD 如 1032E/1048C 95108 或 7128S 等 下载时 最好将系统的电路 模式

切换到 b 以便使工作电压尽可能接近 5V

j:

最好通过对 PC 机的 CMOS 的设置 将打印机口的输入输出模式改成 EPP 模式

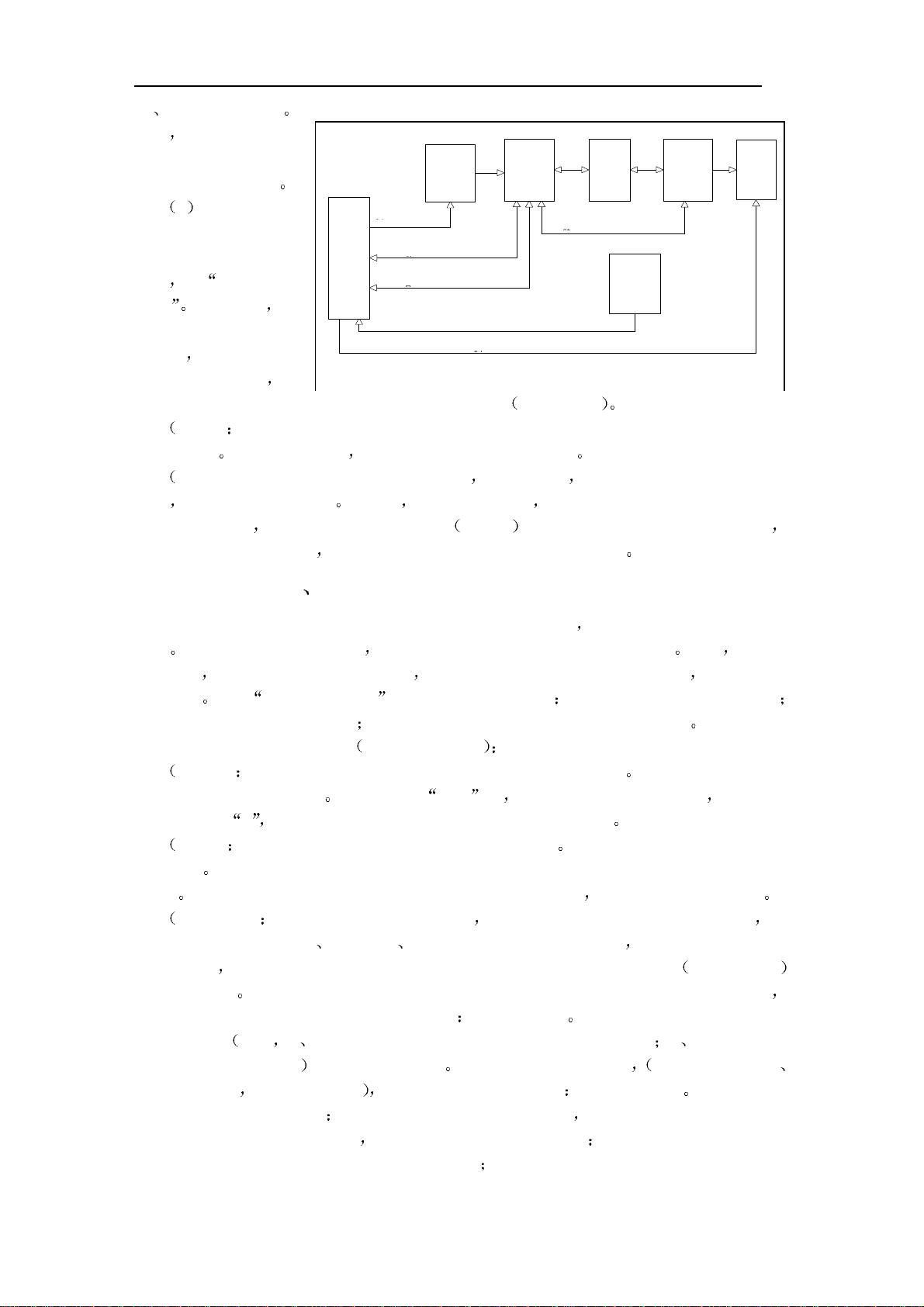

二 系统工作原理

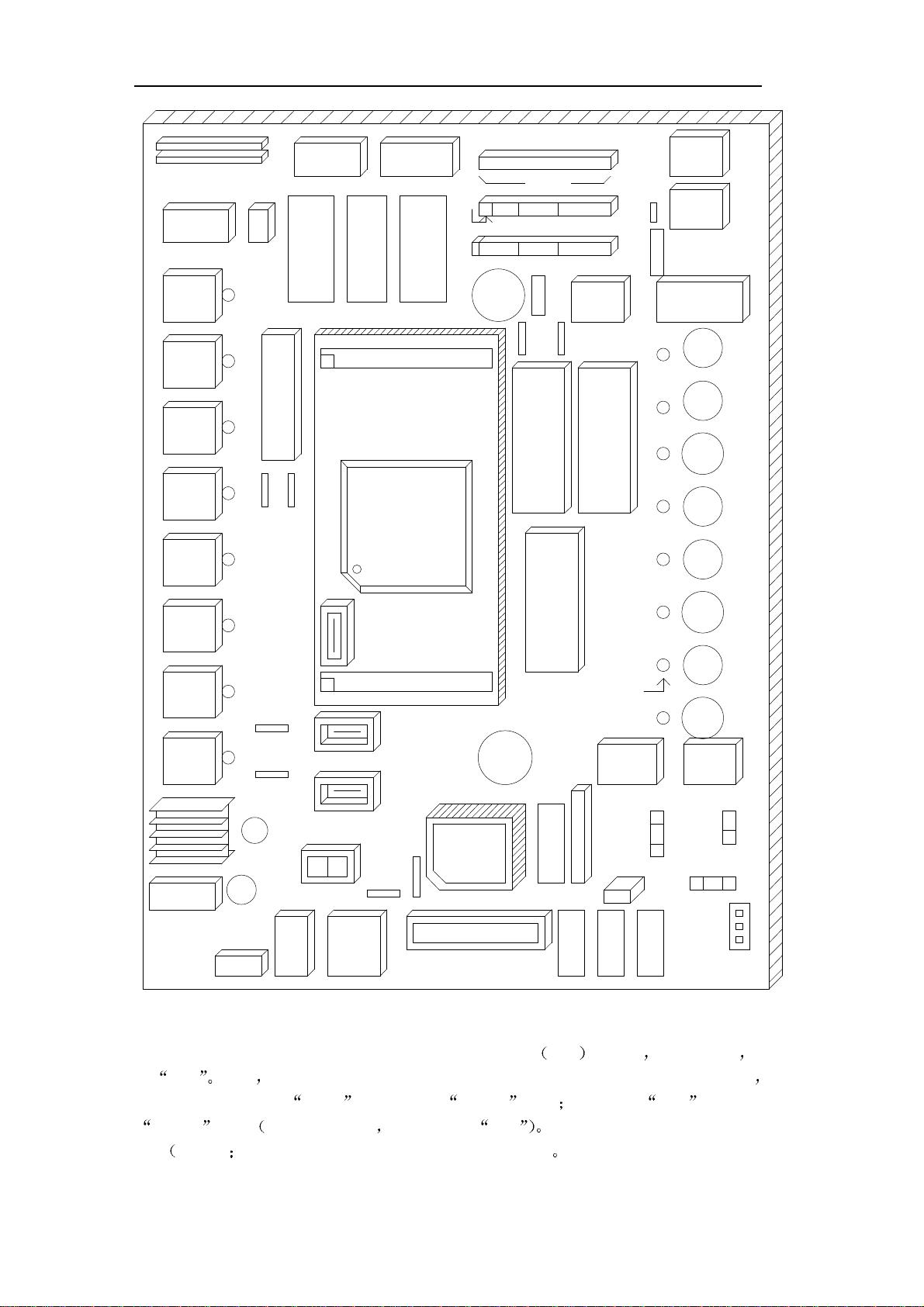

附图 1-1A 为 GW48-CK 型 EDA 实验开发系统的板面结构图 附图 1-2 为其功能结构模块

图 图中所示的各主要功能

模块对应于附图 1-1A 的器

件位置恰好处于目标芯片适

配座 B2 的下方 由一微控

制器担任 其各模块的功能

分述如下 这部分内容可选

看或不看

1) BL1 实验或开发

所需的各类基本信号发生模

块 其中包括最多至 8 通道

的单次脉冲信号发生器 高

低电平信号发生器 BCD 码

或 16 进制码 8421 码 信

号发生器 所有这些

信号的发生主要由

BL6 主控单元产生

并受控于系统板上的

8 个控制键

2) BL5

CPLD/FPGA 输出信息

显示模块 其中包括

直通非译码显示 BCD

七段译码显示 16 进制全码七段译码显示 两组 8 位发光管显示 16 进制输入信号显示指

附图 1-1B GW48 系统目标板插座引脚信号图

附表 1-1 在线编程坐各引脚与不同 PLD 公司器件编程下载接口说明

PLD 公司

LATTICE

ALTERA/ATMEL XILINX VANTIS

编程座

引脚

IspLSI CPLD FPGA CPLD FPGA CPLD

TCK (1) SCLK TCK DCLK TCK CCLK TCK

TDO (3) MODE

TDO

CONF_DONE TDO DONE TMS

TMS (5) ISPEN TMS nCONFIG TMS /PROGRAM ENABLE

nSTA (7) SDO nSTATUS TDO

TDI (9) SDI TDI DATA0 TDI DIN TDI

SEL0 GND VCC VCC GND GND VCC

SEL1 GND

VCC

VCC VC VCC GND

- 1 -

示 声响信号指示等

同样 所有这些显示形

式及形式的变换皆由

BL6 转换和独立控制

3 在 BL6 的监控

程序中安排了多达 12

种形式各异的信息矢量

分布 即 电路重构软

配置 由此可见 虽

然 GW48 系统从硬件结

构上看 是一个完全固

定下来的实验系统 但

其功能结构却等同于 12 套实验接口迥异的实验系统 参见第二节

4) BL3 此模块主要是由一目标芯片适配座以及上面的 CPLD/FPGA 目标芯片和编程下

载电路构成 通过更换目标板 就能对多种目标芯片进行实验

5) BL6 使 GW48 系统的应用结构灵活多变 实际应用中 该模块自动读取 BL7 的选择

信息 以确定信息矢量分布 实验前 可根据实验类型 以及所需的 CPLD/FPGA 目标芯片

的 I/O 接口位置 从 14 张实验电路结构图 第二节 中找到相适应的实验系统功能结构

并将该图的编号键入 BL7 系统即刻进入了所需要的接口和实验模式

三 GW48-CK 系统主板结构与使用方法

附图 1-1A 为 GW48-CK 型 EDA 实验开发系统的主板结构图 该系统的实验电路结构是可

控的 即可通过控制接口键 SW9 使之改变连接方式以适应不同的实验需要 因而 从物理

结构上看 实验板的电路结构是固定的 但其内部的信息流在主控器的控制下 电路结构将

发生变化 这种 电路重构软配置 设计方案的目的有 3 个 1.适应更多的实验与开发项目

2. 适应更多的 PLD 公司的器件 3. 适应更多的不同封装的 FPGA 和 CPLD 器件 系统板面主

要部件及其使用方法说明如下 请参看附图 1-1A

1)

SW9

按动该键能使实验板产生 12 种不同的实验电路结构 这些结构如第二节的

14 张实验电路结构图所示 例如选择了 NO.3 图 须按动系统板上的 SW9 键 直至数码

管 SWG9 显示 3 于是系统即进入了 NO.3 图所示的实验电路结构

2)

B2

这是一块插于主系统板上的目标芯片适配座 对于不同的目标芯片可配不同

的适配座 可用的目标芯片包括目前世界上最大的六家 FPGA/CPLD 厂商几乎所有 CPLD 和

FPGA 第三节的表中已列出多种芯片对系统板引脚的对应关系 以利在实验时经常查用

3)

J3B/J3A

如果仅是作为教学实验之用 系统板上的目标芯片适配座无须拔下 但

如果要进行应用系统开发 产品开发 电子设计竞赛等开发实践活动 在系统板上完成初步

仿真设计后 就有必要将连有目标芯片的适配座拔下插在自己的应用系统上 如 GWDVP 板

进行调试测试 为了避免由于需要更新设计程序和编程下载而反复插拔目标芯片适配座

GW48 系统设置了一对在线编程下载接口座 J3A 和 J3B 此接口插座可适用于不同的

FPGA/CPLD 注意 1 此接口仅适用于 5V 工作电源的 FPGA 和 CPLD 2 5V 工作电源

必须由被下载系统提供 的配置和编程下载 对于低压 FPGA/CPLD 如 EP1K30/50/100

EPF10K30E 等 都是 2.5V 器件 下载接口座必须是另一座 ByteBlasterMV

(4)

混合工作电压使用

对于低压 FPGA/CPLD 目标器件 在 GW48 系统上的设计方法

与使用方法完全与 5V 器件一致 只是要对主板的跳线作一选择

跳线 JV2 对芯核电压 2.5V 或 1.8V 作选择

接口方

式与接

口信息

矢量总

控制模

块

实验信号

源发生模

块

ispLSI

实验与接

口方式选

择器

接口信息

矢量转换

模块

ispLSI

输出显

示模块

接口信息

矢量转换

模块

信息矢量通

路

接口控制信

号

信号显示方式控

制

BL6

BL1

BL2 BL3 BL4 BL5

BL7

I/O

接口信息交换通

路

信号源选择控

制

- 2 -

跳线 JVCC 对芯片 I/O 电压 3.3V(VCCIO)或 5V VCC 作选择 对 5V 器件 必须

选 VCC 例如 若系统上插的目标器件是 EP1K30/50/100 或 EPF10K30E/50E 等 要

求将主板上的跳线座 JVCC 短路帽插向 VCCIO 一端 将跳线座 JV2 短路帽插向

+2.5V 一端 如果是 5V 器件 跳线应插向 VCC

5)

J2

此接口通过下载线与微机的打印机口相连 来自 PC 机的下载控制信号和

散热器

B2

适配座

目标芯片

J3B

在线下载口

模拟接口

接口电路切换座

数码

8

数码

7

数码

6

数码

5

数码

4

数码

3

数码

2

数码

1

在线下载通讯接口

单片机接口器件

电源输入

PS/2

接口

D/A

信号输出

A/D

信号输入

A/D

信号输入

超高速串行

A/D

座

高速串行

A/D

座

ADC0809

并行模数转换器件

DAC0832

AD1674/AD574

并行模数转换器件

并行数模转换器件

系统复位

时钟发生电路

接口电路

视频接口电路

串行

EEP ROM

接口

VGA

视频接口

RS-232

串行接口

频率计

0832

工作电源

ASIC

KONXIN

模式选择键

VR1

JMCU

J5

高频时钟源

50M

晶振

J4

FUSE

在线下载接口

JVCC

JS6

JS5

JV2

RS-232

J11

J10

串行

D/A

座

串行

A/D

座

JAV

8031

ADC08031 TLV1572

JTL

JSL

DACC

ADCC

TLC549 TLC5620

24CXX

93CXX

目标板插座

1

目标板插座

2

ByteBlasterMV

ByteBlaster

J7

J1

发光管

CON2

2

CON1

1

CPLD/FPGA

目标芯片

EDA

实验开发

键

1

D9

键

2

D10

键

3

D11

键

4

D12

键

8

D16

键

7

D15

键

6

D14

键

5

D13

扬声器

SWG9

模式指示

SW9

SW10

-12V

GND

+12V

时钟频率选择

S1

J2

J8

J6

K1

+5V

GND

电源输出

电源开关

C38

IN0

IN1

AOUT

AIN1

AIN0

JP1A JP1B JP1C

中频组高频组低频组

B8

B4

B3

VGA

Clock0

JP2

D8 D7 D6 D5 D4 D3 D1D2

附图 1-1A GW48-CK 实验开发系统的板面结构图

剩余71页未读,继续阅读

资源评论

hglikun

- 粉丝: 3

- 资源: 47

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功