LogiCORE IP

Virtex-6 FPGA

GTX Transceiver

Wizard v1.12

User Guide

UG516 (v1.12) January 18, 2012

Virtex-6 FPGA GTX Transceiver Wizard v1.12 www.xilinx.com UG516 (v1.12) January 18, 2012

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum

extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL

WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF

MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether

in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising

under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or

consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action

brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.

Xilinx assumes no obligation to correct any errors contained in the Materials, or to advise you of any corrections or update. You may not

reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and

conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm

; IP cores may be subject to warranty and

support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any

application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:

http://www.xilinx.com/warranty.htm#critapps

.

© Copyright 2009–2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included

herein are trademarks of Xilinx in the United States and other countries. CPRI is a trademark of Siemens AG. PCI, PCIe and PCI Express

are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

UG516 (v1.12) January 18, 2012 www.xilinx.com Virtex-6 FPGA GTX Transceiver Wizard v1.12

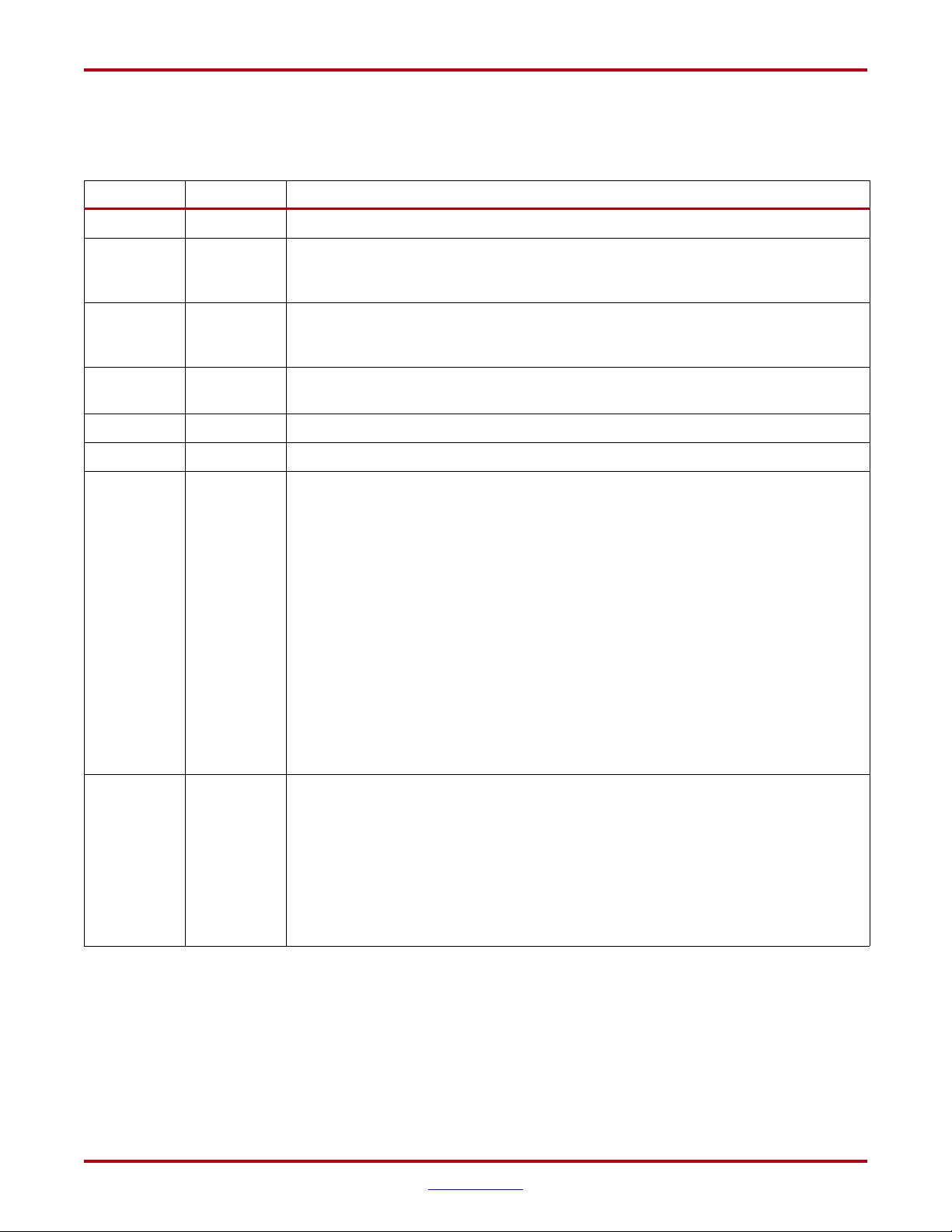

Revision History

The following table shows the revision history for this document.

Date Version Revision

06/24/09 1.2 Initial Xilinx release.

09/16/09 1.3

Tools and Wizard updates. Added support for the Virtex-6 HXT family. Added

Chapter 4, Quick Start Example Design and renumbered Chapter 5, Detailed Example

Design.

12/02/09 1.4

Tools and Wizard updates. Added support for Virtex-6 Lower Power family. Added

Recommended Design Experience in Chapter 1. Replaced Appendix A: References with

Related Xilinx Documents in Chapter 1. Updated Table 3-18.

04/19/10 1.5

Tools and Wizard updates. Added CXT support. Added REFCLK0/01 Q9 in Table 3-6,

updated TXUSRCLK and RXUSRCLK in Table 3-7, added scripts to Table 5-8.

07/23/10 1.6 Tools and Wizard updates.

09/21/10 1.7 Wizard v1.7 release.

12/14/10 1.8

Wizard v1.8 release.

Integrated the LogiCORE IP Virtex-6 FPGA GTX Transceiver Wizard Data Sheet (DS708)

and Getting Started Guide (UG516). The integrated document is named the LogiCORE IP

Virtex-6 FPGA GTX Transceiver Wizard v1.12 User Guide (UG516).

Modified the following chapters to incorporate the integration:

• Chapter 1, Introduction

• Chapter 2, Installing the Wizard

• Chapter 3, Running the Wizard

Other changes:

• Configuring and Generating the Wrapper in Chapter 3:

• Modified heading name to be more descriptive.

• Chapter 4, Quick Start Example Design:

•Rearranged the sections

• Renamed the simulation section to Functional Simulation of the Example Design

03/01/11 1.9

Wizard v1.9 release. Tools and Wizard versions updates. Removed the Conventions

section from the Preface. In Chapter 2, Installing the Wizard, changed section title from

Tested Design Tools to Design Tools and removed reference to service packs. In

Chapter 3, Running the Wizard, in Overview, added note about GUI screenshots used in

the guide. Changed title of “Wrapper Overview” section to Structure of the GTX

Transceiver Wrapper, Example Design, and Testbench and replaced its text, removed

component numbers from and renamed Figure 3-2. Changed title of “Example Design

Overview” section to Example Design—XAUI Configuration and renamed Figure 3-3. In

Chapter 5, Detailed Example Design, renamed Figure 5-1.

Virtex-6 FPGA GTX Transceiver Wizard v1.12 www.xilinx.com UG516 (v1.12) January 18, 2012

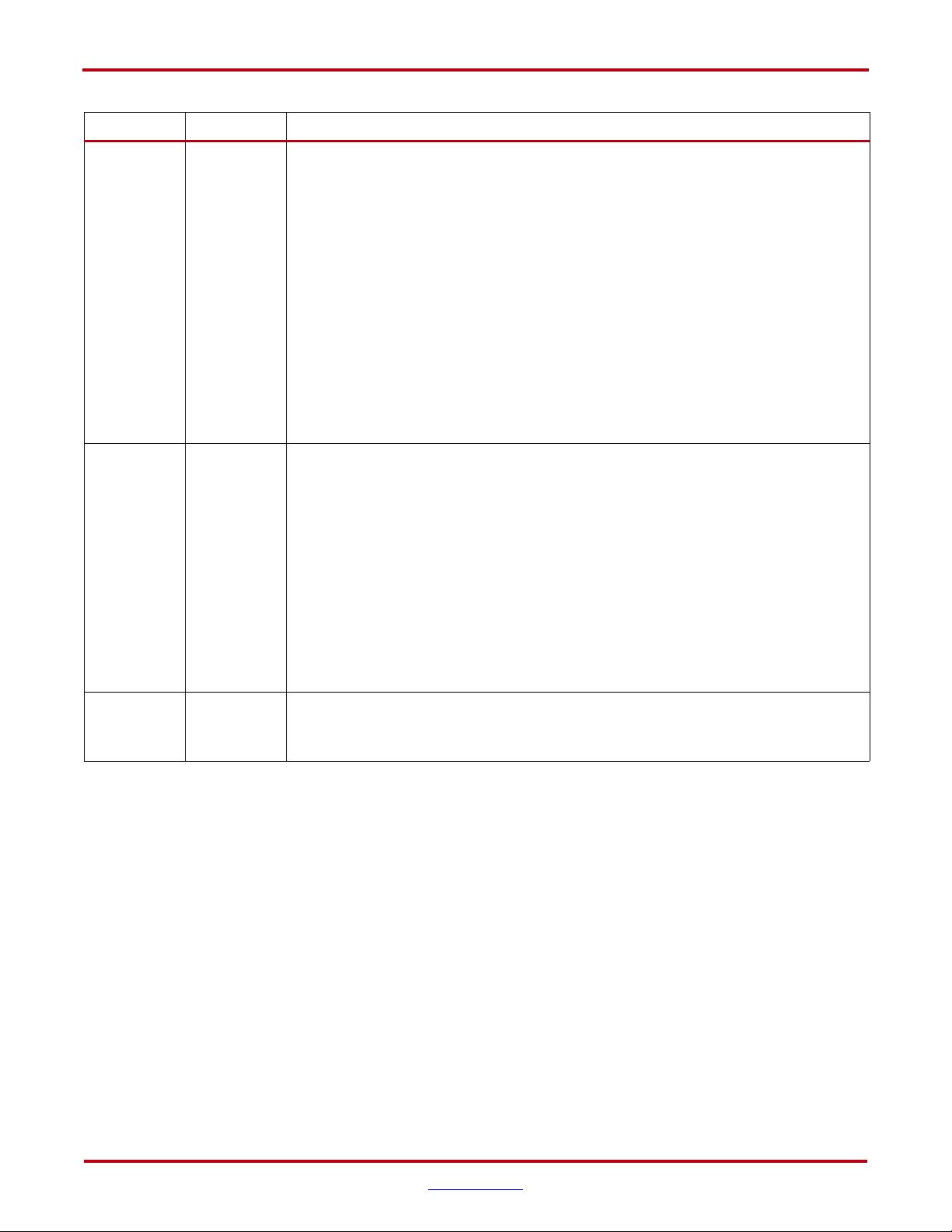

06/22/11 1.10

Wizard v1.10 release.

In Chapter 1, Introduction, revised About the Wizard, Features, Supported Devices,

Recommended Design Experience, and Related Xilinx Documents.

In Chapter 2, Installing the Wizard, revised Tools and System Requirements and

Installing the Wizard.

In Chapter 3, Running the Wizard, revised title and content of Structure of the GTX

Transceiver Wrapper, Example Design, and Testbench. Renamed Figure 3-2. Updated

Data Path Width descriptions and added four entries for 64B/66B_with_Ext_Seq_Ctr to

Encoding in Table 3-1. Updated Data Path Width descriptions and added two entries for

64B/66B to Decoding in Table 3-2. Added TXRATE, GTXTEST, and RXRATE to Table 3-8.

Update Comma Mask description in Table 3-9. Added instruction to paragraph

following Table 3-12.

In Chapter 4, Quick Start Example Design, revised Source Directories in Table 4-1.

In Chapter 5, Detailed Example Design, revised ChipScope Pro tools description and

added PlanAhead software support in Table 5-5.

10/19/11 1.11

Wizard v1.11 release.

Chapter 1: Revised About the Wizard. In Ordering Information, replaced 13.2 with 13.3.

Chapter 2: In Operating Systems, replaced 13.2 with 13.3.

Chapter 3: In Table 3-1, shaded all entries for Encoding, except for 8B/10B. In Table 3-2,

shaded all entries for Decoding, except for 8B/10B. In Table 3-6, renamed REFCLK0/01

to REFCLK0/1, and renumbered Q4 through Q9 as Q3 through Q8. Renamed Table 3-14.

In Table 3-17, removed shading from all rows except RXPRBSERR_LOOPBACK. In

Table 3-19, removed sentence about XAUI example using 7 from description of Sequence

2 Max Skew.

Chapter 4: Added Netlist Simulation of the Example Design.

Chapter 5: In Table 5-7

, added rows for sim_reset_mgt_model.vhd and

demo_tb_imp.v[hd]. Added simulation/netlist, containing Table 5-9.

01/18/12 1.12

Wizard v1.12 release. Replaced 13.3 with 13.4 throughout.

Chapter 3: Updated Table 3-1 and Table 3-2. Updated title of Table 3-15. Shaded all

entries in Table 3-15 and added table note. Unshaded last two rows of Table 3-18.

Date Version Revision

Virtex-6 FPGA GTX Transceiver Wizard v1.12 www.xilinx.com 5

UG516 (v1.12) January 18, 2012

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 1: Introduction

About the Wizard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Supported Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Provided with the Wizard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Recommended Design Experience. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Related Xilinx Documents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Technical Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Feedback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Wizard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Chapter 2: Installing the Wizard

Tools and System Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Operating Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Design Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Before You Begin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Installing the Wizard. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Verifying Your Installation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Chapter 3: Running the Wizard

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Structure of the GTX Transceiver Wrapper, Example Design, and Testbench. . . . . . 17

Example Design—XAUI Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Setting Up the Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Creating a Directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Setting the Project Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Configuring and Generating the Wrapper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Line Rates and Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

GTX Transceiver Placement and Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Synchronization and Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Preemphasis, Termination, and Equalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

PCI Express, SATA, OOB, PRBS, and RX Loss of Sync . . . . . . . . . . . . . . . . . . . . . . . . . 34

Channel Bonding Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table of Contents