没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

QuadSPI

Microcontrollers Division

Application Team

Introduction

02/07/

2015

19

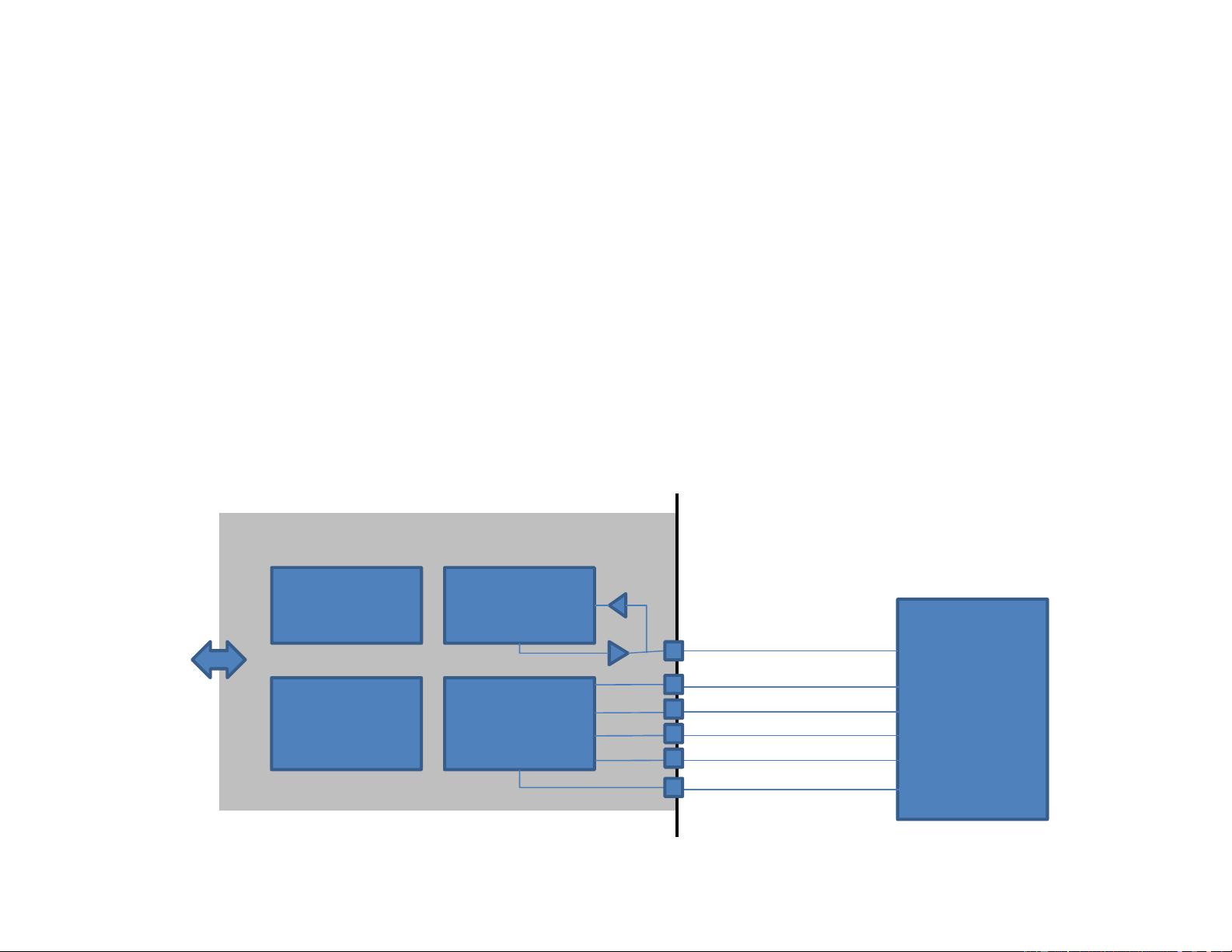

QUADSPI

Overview

• Communication interface for single/dual/quad SPI flash memories

• Three operating modes

– Indirect : all the operations are performed through registers (classical SPI)

– Status polling : periodical read of the flash status registers (interrrupt

generation)

– Memory mapped : External flash seen as internal for read operations

20

Registers /

Control

Clock

Management

Shift RegisterFIFO

QSPI Flash

CLK

BK1_IO0/SO

BK1_IO1/SI

BK1_IO2

BK1_IO3

BK1_nCS

AHB

CLK

Q0/SI

Q1/SO

Q2/nWP

Q3/nHOLD

nCS

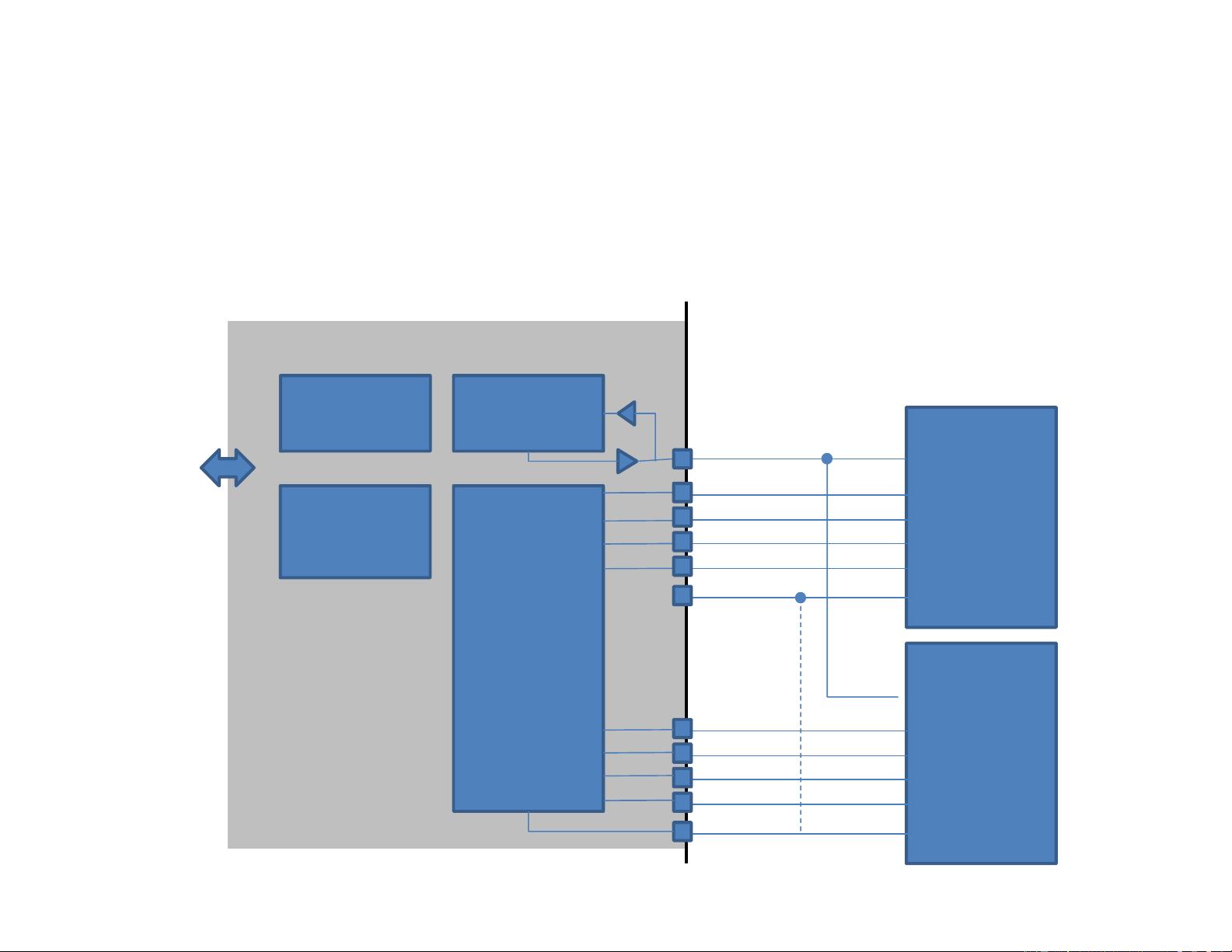

Dual-quad mode

• Access two flashes in parrallel with the same frame format

and the same instruction (8-bit par cycle)

21

QUADSPI

Registers /

Control

Clock

Management

Shift Register

FIFO

QSPI Flash

CLK

BK1_IO0/SO

BK1_IO1/SI

BK1_IO2

BK1_IO3

BK1_nCS

AHB

CLK

Q0/SI

Q1/SO

Q2/nWP

Q3/nHOLD

nCS

QSPI Flash

BK2_IO0/SO

BK2_IO1/SI

BK2_IO2

BK2_IO3

BK2_nCS

CLK

Q0/SI

Q1/SO

Q2/nWP

Q3/nHOLD

nCS

Main features

• Three functional modes:

– Indirect

– Status-polling

– Memory-mapped

• Optimized operations

– SDR and DDR support

• Fully programmable

– Opcode for both indirect and memory mapped mode

– Frame format for both indirect and memory mapped

mode

• Integrated FIFO for reception and transmission

– 8, 16, and 32-bit data accesses are allowed

– DMA channel for indirect mode operations

• Interrupt generation on FIFO threshold, timeout, operation complete, and access error

22

剩余23页未读,继续阅读

资源评论

Mr.Black1213

- 粉丝: 1

- 资源: 10

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功