目 录

216.6.3 排阻间的串扰 .........................................................

216.6.2 相邻贴片电阻间的串扰 ...................................................

206.6.1 相邻轴向电阻间的串扰 ...................................................

196.6 匹配电路的串扰 .............................................................

166.5.3 匹配电阻的电感 .........................................................

156.5.2 匹配电阻的功率消耗 .....................................................

156.5.1 匹配电阻的精确性 .......................................................

156.5 电阻阻值的选择 .............................................................

146.4.2 差分线的终端匹配 ........................................................

146.4.1 容性负载匹配的直流不平衡性 ..............................................

126.3 中间匹配 ...................................................................

126.2.6 始端匹配的功率消耗 .....................................................

126.2.5 始端匹配的其它拓扑形式 .................................................

116.2.4 始端匹配的输出驱动电流 .................................................

116.2.3 始端匹配较平坦的阶跃响应 ...............................................

116.2.2 始端匹配的上升时间 .....................................................

116.2.1 始端匹配的阻值 .........................................................

106.2 始端匹配 ...................................................................

106.1.4 终端匹配电路的功耗 .....................................................

86.1.3 其它拓扑形式的终端匹配 ..................................................

56.1.2 终端匹配的直流偏置 ......................................................

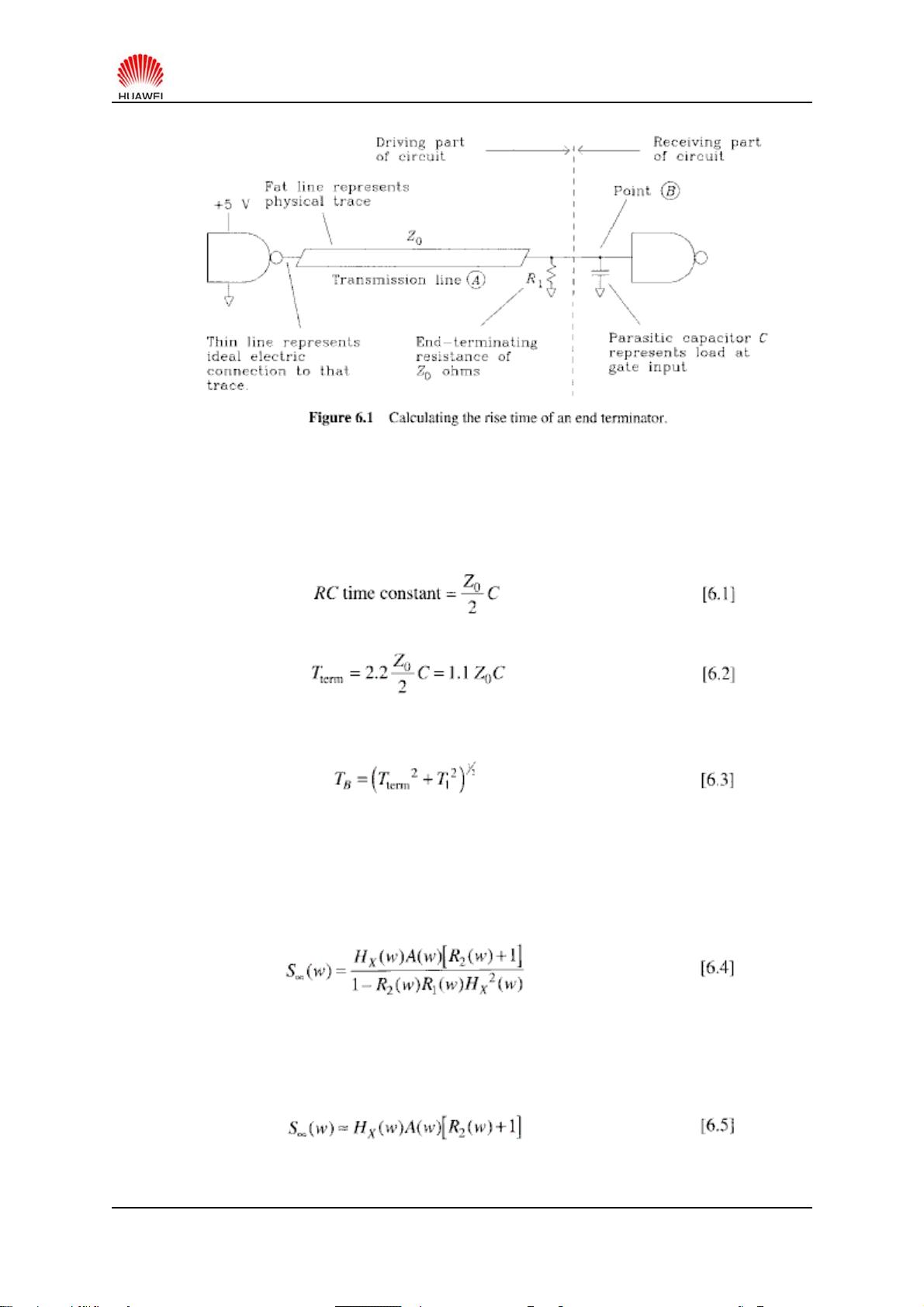

36.1.1 终端匹配的上升时间 ......................................................

36.1 终端匹配 ...................................................................

2第6章 传输线匹配 ................................................................

内部公开

高速数字电路设计

2001-08-16 版权所有,侵权必究 第2页,共22页