XAPP974 (v1.1.3) March 24, 2009 www.xilinx.com 1

© 2007–2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other

countries. All other trademarks are the property of their respective owners

’

Summary This document describes the hardware setup, file generation flow, and software flow for

programming an Numonyx M25Pxx SPI configuration PROM through the JTAG interface of a

Spartan®-3A FPGA using iMPACT 9.1.01i. The software flows, including PROM file

generation, are also covered.

Introduction Similar to the traditional configuration memories, SPI serial flash memories must be loaded

with the configuration data. SPI serial flash memories have a single interface for programming,

but there are multiple methods to deliver the data to this interface. Four primary delivery

methods exist to program an SPI serial flash through the SPI interface:

• Indirect in-system programming or ISP (iMPACT, JTAG tool vendor or custom solution)

• Direct in-system programming (SPI direct interface connect)

• Third-party programmers (off-board programming)

• Embedded processor (in-system programming)

Production programming is often accomplished via a third-party programmer or JTAG tool, and

many distributors offer mass production gang programming. For prototyping, the iMPACT software,

included in the ISE® development software tools, with a Xilinx® parallel cable or Platform Cable

USB can program select SPI serial flash memories directly (refer to [Ref 4] for more details).

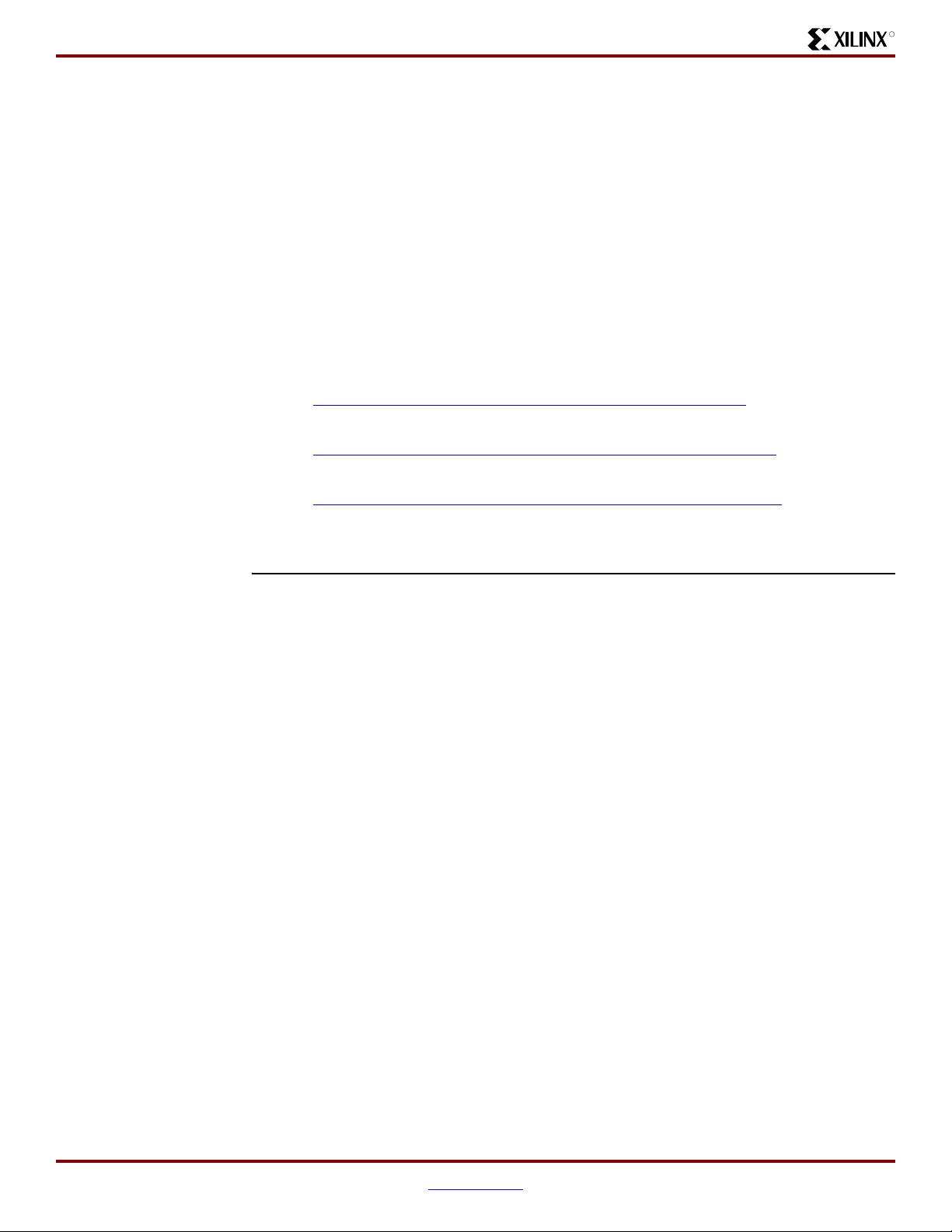

Unlike the Xilinx Platform Flash PROMs, which are in-system programmable through a

standard JTAG interface, SPI flash devices require extra logic for SPI indirect in-system

programming via JTAG with Xilinx software and cables. The extra logic is represented as a core

residing inside the FPGA, which the iMPACT software uses as a bridge between the FPGA

JTAG interface and the SPI PROM’s SPI interface.

The following sections discuss the hardware connections required for the indirect in-system

programming of SPI serial flash for prototype designs. The Xilinx software tool flows to generate

an SPI formatted file and for programming select SPI serial flash memories is also covered.

SPI Basics SPI serial flash memories use the Serial Peripheral Interface (SPI), a four-wire, synchronous

serial data bus. This serial data link was pioneered as a serial communication interface

between a microcontroller and its peripherals and is a popular interface in embedded and

consumer markets. This interface can now also be used to configure Xilinx FPGAs.

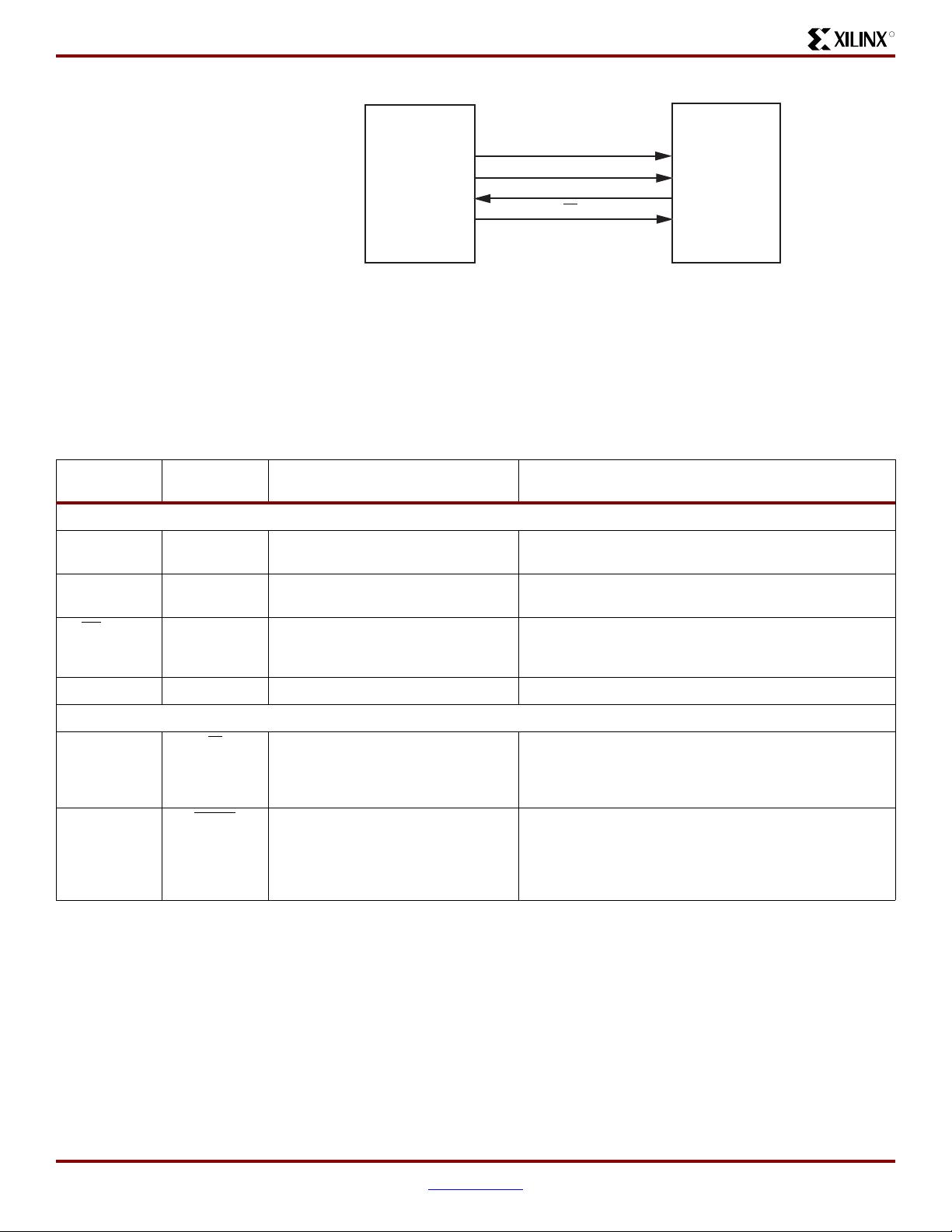

An SPI system typically consists of a master device and a slave device (Figure 1, page 2). When

using this four-signal interface to configure a Xilinx FPGA from an SPI serial flash, the FPGA is the

master device and the SPI serial flash is the slave device.

The master FPGA device controls the timing via the SCK clock signal. Data is clocked out of the

FPGA master and into the SPI serial flash slave on the MOSI signal after the select signal SS

goes Low. During the same clock cycle, data is clocked out of the SPI serial flash slave and into

the FPGA master using the MISO signal. Data is clocked out of each device on one edge and

clocked into each device on the next opposite edge in the period.

Application Note: Spartan-3A FPGAs

XAPP974 (v1.1.3) March 24, 2009

Indirect Programming of SPI Serial Flash

PROMs with Spartan-3A FPGAs

Author: Jameel Hussein

R

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功