MQ-3酒精传感器模块资料技术手册+软件测试工程源码.zip

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

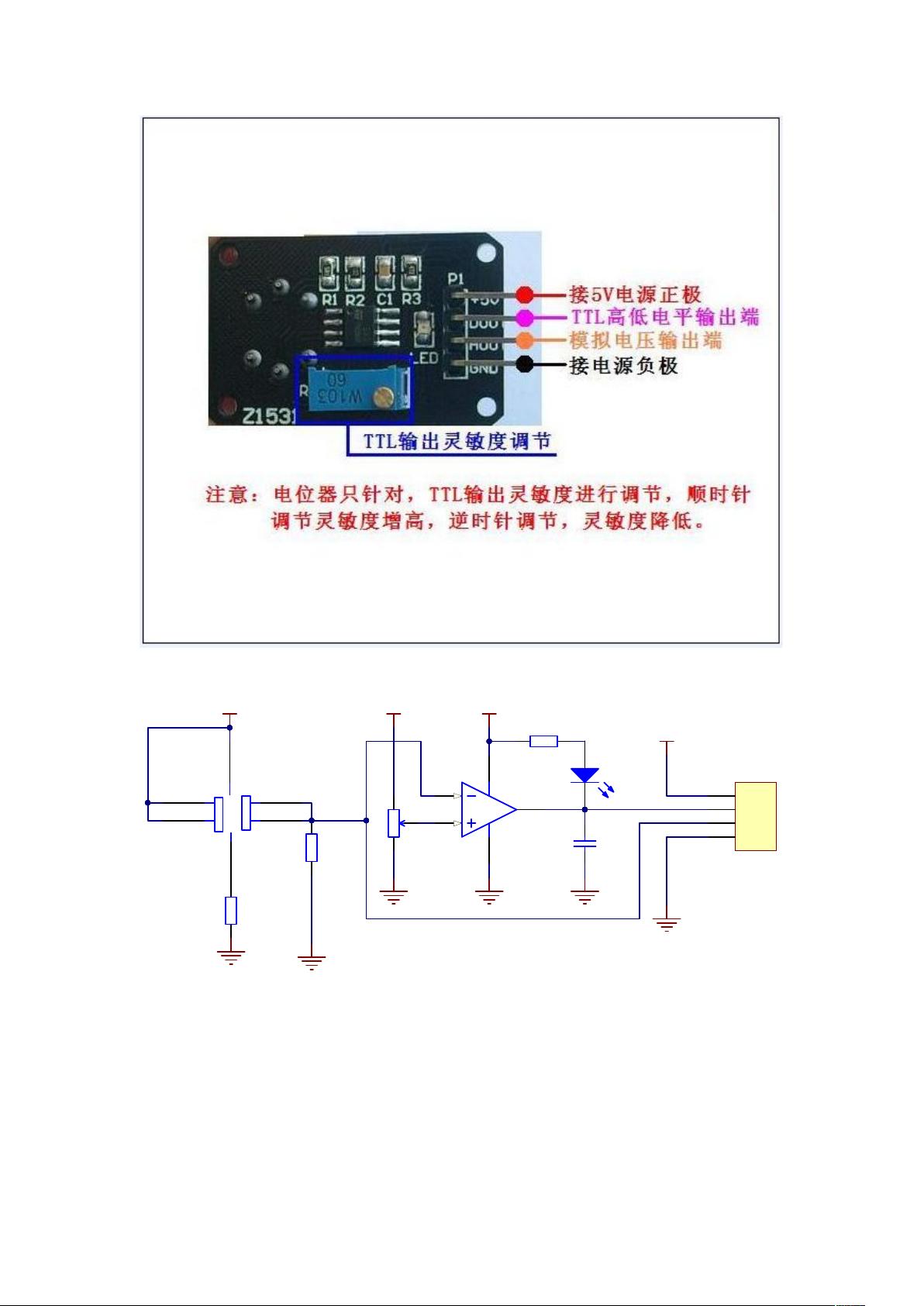

MQ-3酒精传感器模块是一种广泛应用于气体检测领域的电子设备,主要设计用于检测环境中酒精的浓度。这个压缩包包含了关于MQ-3传感器模块的详细技术资料和软件测试工程源码,帮助用户更好地理解和应用该模块。 《MQ-3.pdf》是MQ-3酒精传感器的技术手册,其中涵盖了传感器的工作原理、规格参数、电路设计、接口定义以及如何进行信号处理等关键内容。MQ-3传感器采用半导体气敏材料,当其暴露在含有酒精的气体中时,材料的电阻值会发生变化,通过测量电阻的变化可以间接获取酒精浓度信息。 《产品使用手册.doc》则为用户提供了一步一步的使用指导,包括传感器的安装、接线方式、电源需求、校准方法以及日常维护注意事项。这有助于确保用户正确地操作和保养MQ-3模块,从而获得准确可靠的检测结果。 《检测说明判断传感器是否正常.txt》提供了检查传感器工作状态的方法,包括初始校零、正常工作状态下的电压读数范围以及异常情况的识别。通过这些步骤,用户可以快速验证传感器是否正常工作,并排除潜在故障。 “TTL输出测试程序”和“模拟量测试参考程序”是配套的软件资源,用于读取和解析MQ-3传感器的输出信号。TTL输出测试程序可能是一个简单的Arduino或Raspberry Pi代码示例,展示了如何连接传感器并处理其数字输出。模拟量测试程序则可能涉及ADC(模拟-to-数字转换器)的使用,因为MQ-3传感器通常提供模拟信号,需要转换为数字值才能被微控制器处理。 在实际应用中,MQ-3酒精传感器常用于防酒驾装置、智能家居安全系统、工业过程监控等领域。通过软件测试工程源码,开发者可以了解如何将传感器数据整合到自己的项目中,实现报警、数据记录或其他定制功能。 总结来说,这个压缩包提供的信息涵盖了MQ-3酒精传感器的硬件、软件和应用层面,无论是初学者还是有经验的开发者,都能从中获益,掌握如何有效地利用MQ-3模块进行气体检测和相关项目开发。

MQ-3酒精传感器模块资料技术手册+软件测试工程源码.zip (40个子文件)

MQ-3酒精传感器模块资料技术手册+软件测试工程源码.zip (40个子文件)  MQ-3酒精传感器模块资料技术手册+软件测试工程源码

MQ-3酒精传感器模块资料技术手册+软件测试工程源码  检测说明判断传感器是否正常.txt 202B

检测说明判断传感器是否正常.txt 202B TTL输出测试程序

TTL输出测试程序  chengxu_Uv2.Bak 0B

chengxu_Uv2.Bak 0B STARTUP.OBJ 750B

STARTUP.OBJ 750B chengxu.M51 5KB

chengxu.M51 5KB STARTUP.A51 6KB

STARTUP.A51 6KB chengxu 2KB

chengxu 2KB chengxu.Uv2 2KB

chengxu.Uv2 2KB chengxu_Opt.Bak 1024B

chengxu_Opt.Bak 1024B STARTUP.LST 11KB

STARTUP.LST 11KB chengxu.lnp 62B

chengxu.lnp 62B chengxu.LST 4KB

chengxu.LST 4KB chengxu.OBJ 2KB

chengxu.OBJ 2KB chengxu.hex 164B

chengxu.hex 164B chengxu.c 2KB

chengxu.c 2KB chengxu.Opt 1KB

chengxu.Opt 1KB chengxu.plg 1KB

chengxu.plg 1KB MQ-3.pdf 141KB

MQ-3.pdf 141KB 产品使用手册.doc 1.63MB

产品使用手册.doc 1.63MB 模拟量测试参考程序

模拟量测试参考程序  ourhc.PWI 768B

ourhc.PWI 768B keil

keil  chengxu_Uv2.Bak 0B

chengxu_Uv2.Bak 0B STARTUP.OBJ 750B

STARTUP.OBJ 750B chengxu.M51 8KB

chengxu.M51 8KB chengxu.__i 37B

chengxu.__i 37B STARTUP.A51 6KB

STARTUP.A51 6KB chengxu 5KB

chengxu 5KB chengxu.Uv2 2KB

chengxu.Uv2 2KB chengxu_Opt.Bak 1KB

chengxu_Opt.Bak 1KB STARTUP.LST 11KB

STARTUP.LST 11KB chengxu.lnp 62B

chengxu.lnp 62B chengxu.LST 5KB

chengxu.LST 5KB chengxu.OBJ 5KB

chengxu.OBJ 5KB chengxu.hex 2KB

chengxu.hex 2KB chengxu.c 3KB

chengxu.c 3KB chengxu.Opt 1KB

chengxu.Opt 1KB chengxu.plg 1KB

chengxu.plg 1KB ourhc.DSN 182KB

ourhc.DSN 182KB Last Loaded ourhc.DBK 182KB

Last Loaded ourhc.DBK 182KB ADC0809中文资料.txt 2KB

ADC0809中文资料.txt 2KB ADC0809.pdf 317KB

ADC0809.pdf 317KB ~$产品使用手册.doc 162B

~$产品使用手册.doc 162B- 1

- 粉丝: 334

- 资源: 2100

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 冲气式打孔机(sw18可编辑+工程图)全套技术资料100%好用.zip

- 产品气密性测试设备sw19可编辑全套技术资料100%好用.zip

- apache-maven-3.8.2

- MATLAB语言实现PID参数的自动整定案例

- lrmx格式编辑器3.2.1.16安装包

- 20241230114sunmingzheng

- 56343智慧停车场微信小程序源码++智能停车系统源码+全开源+操作文档

- 链表押不中就嘎.txt

- 薄膜贴付机sw18可编辑全套技术资料100%好用.zip

- 202278030521 魏娜 图书商城管理系统.docx

- AXI VIP userguide2018

- 飞秋 局域网及时通讯传输软件

- IMG_20241229_152729.jpg

- Snipaste-2.8.3-windows安装包

- 大型喷画打印机sw18可编辑全套技术资料100%好用.zip

- FSCapture-V9.3-CH-2录屏工具

信息提交成功

信息提交成功

- 1

- 2

- 3

前往页