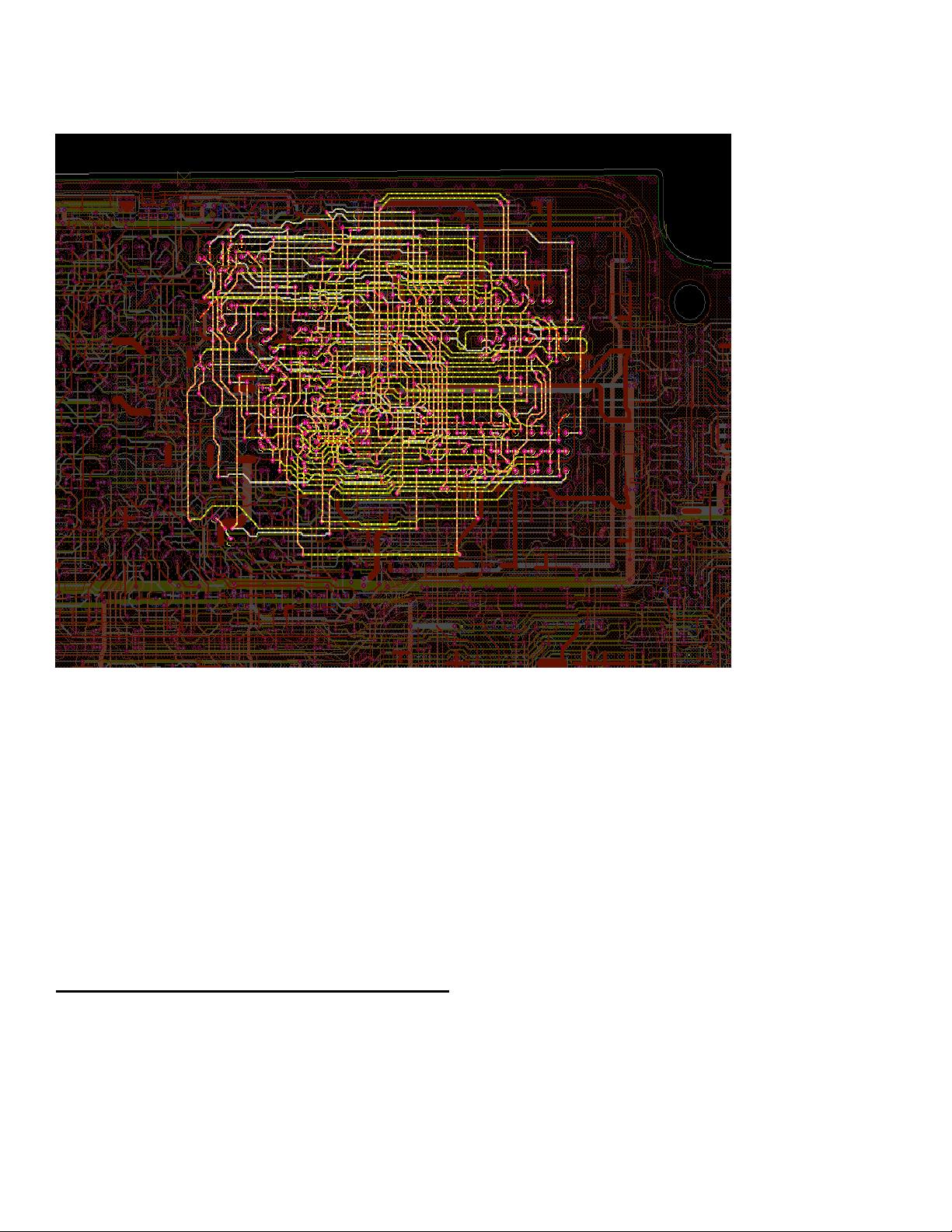

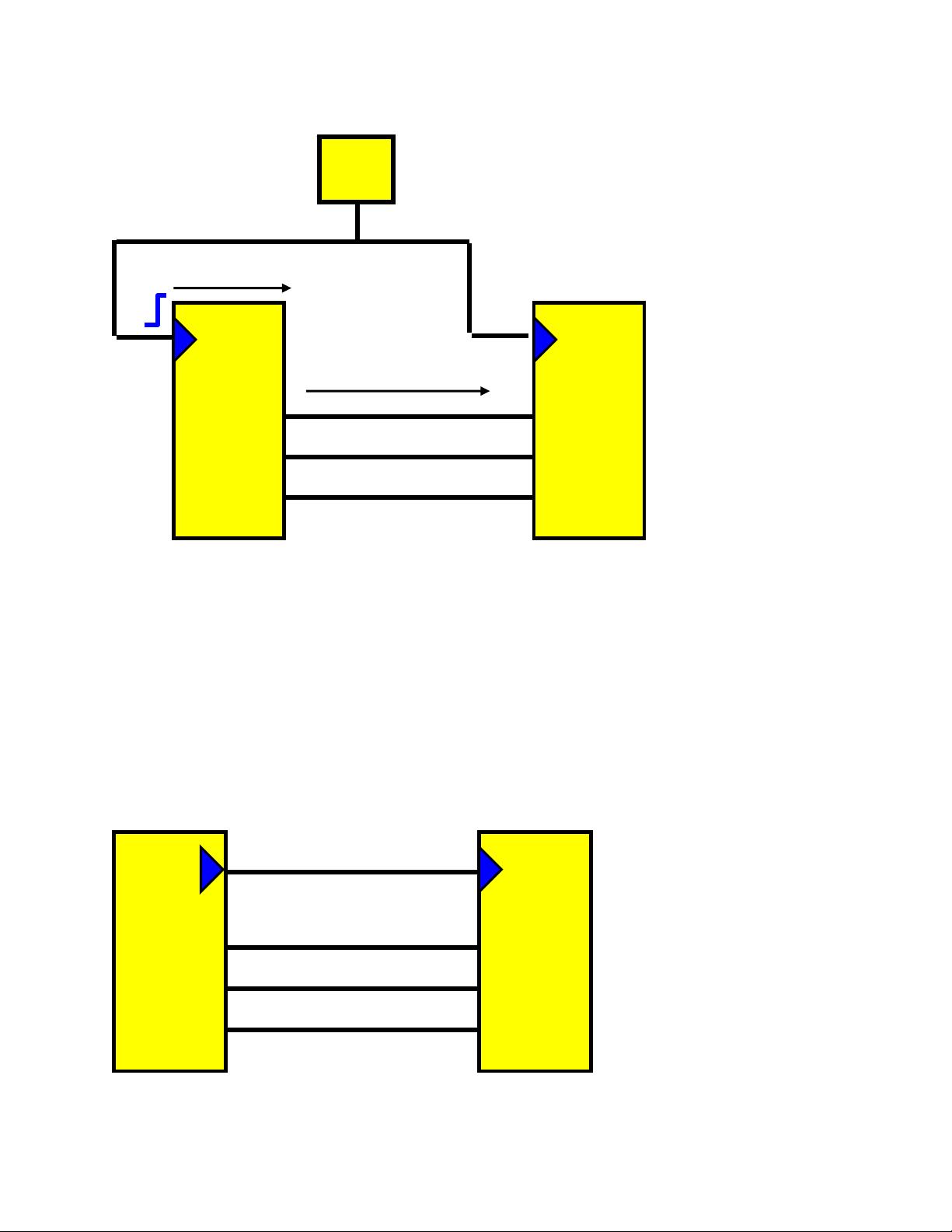

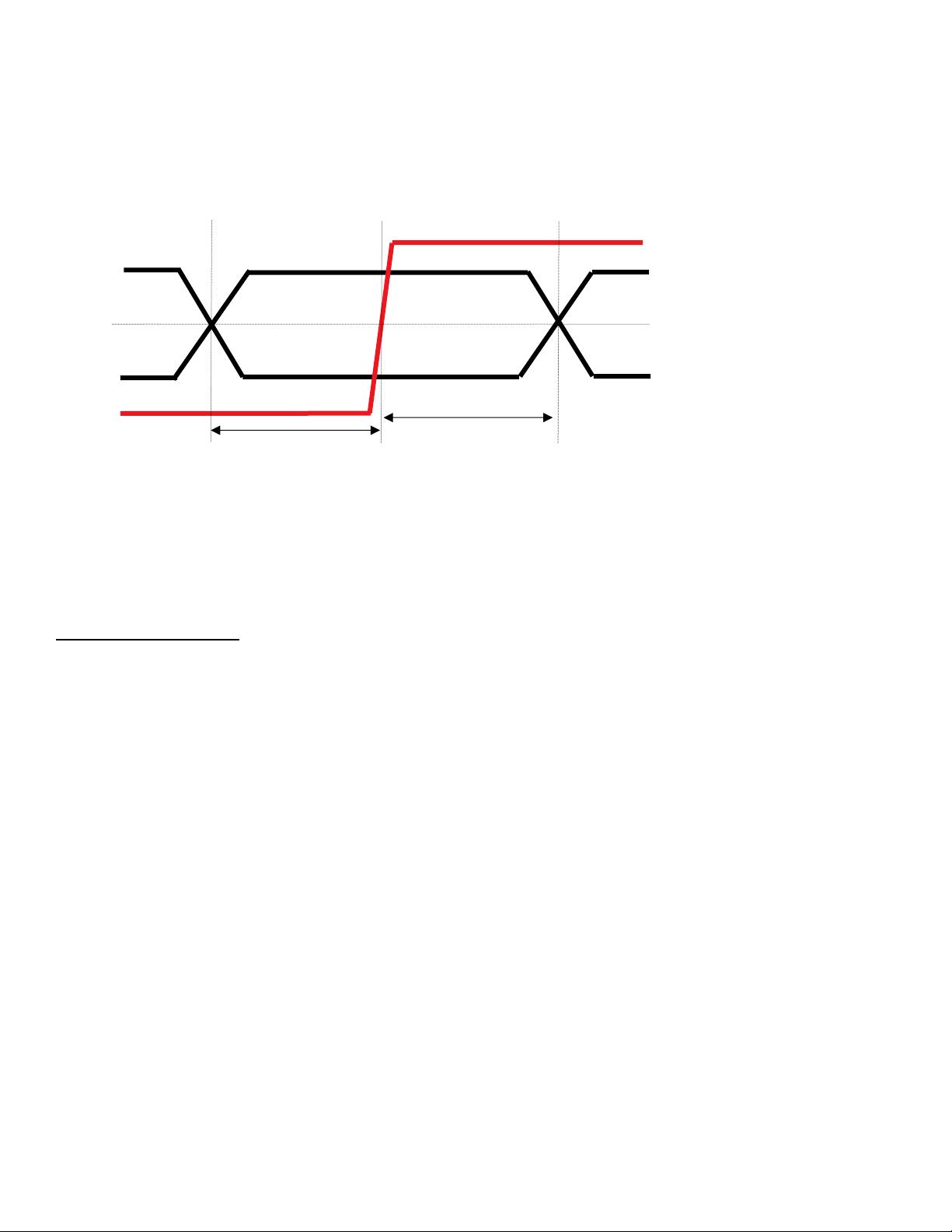

信号完整性(Signal Integrity)在印刷电路板(PCB)设计中的重要性日益凸显,尤其是在高速、高密度的数字设计领域。随着数据传输速率的不断提升,信号完整性问题成为了确保设计首次成功的关键因素。本文将深入探讨信号完整性分析在双倍数据速率(DDR)接口设计中的应用,基于Motorola的一款产品实例,利用Cadence的Allegro PCB SI工具进行设计。 ### 设计过程的关键阶段 #### 设计设置 设计之初,必须设定清晰的目标和约束条件,包括信号的频率、阻抗控制、层数、材料选择等。这些参数直接影响信号在PCB上的传播特性,从而决定信号完整性的优劣。 #### 预布线信号完整性分析 在实际布线之前,预布线信号完整性分析是必不可少的。这一阶段通过模拟信号在不同路径下的行为,预测潜在的问题,如反射、串扰、振荡等,并据此优化布局和布线策略。 #### 约束驱动布线 基于预分析的结果,采用约束驱动的布线方法,确保所有信号路径满足预先设定的信号完整性标准。这一步骤中,设计者需考虑的因素包括但不限于线路宽度、间距、长度匹配、终端匹配等。 #### 后布线信号完整性分析 布线完成后,进行后布线信号完整性分析,验证实际布局是否达到预期的信号完整性目标。这包括检查时延、上升时间、下降时间、过冲、下冲等关键指标,以及评估信号的抖动和眼图质量。 ### 双倍数据速率(DDR)接口的独特挑战 DDR接口作为源同步信号类型,其设计中管理时钟与数据之间的偏移(skew)成为核心挑战。源同步信号意味着数据和时钟信号在同一时刻由发送端发出,但在接收端可能因路径差异而出现不同步。为满足建立时间和保持时间的时序要求,必须精确控制各信号路径的长度和时延。 ### 项目背景与挑战 本案例研究基于iDEN Subscriber Group的一款手机设计,该手机采用移动Linux Java平台,内置双核定制处理器,分别运行于400MHz和208MHz。内存控制器支持16位NAND和DDR接口,其中DDR工作在133MHz。为了适应不同供应商的内存设备,设计必须考虑时序裕量、输入电容和缓冲器驱动强度的差异。此外,消费者对更小、更薄手机的偏好,使得关键组件和模块的设计与布局面临严峻挑战。在有限的空间内,不仅需要集成RF、电源管理、DC、音频、数字IC等功能,还要兼顾音箱、天线、显示屏和摄像头等部件的严格位置需求。 信号完整性分析对于现代高速数字系统设计至关重要,特别是在DDR接口等关键环节。通过综合运用先进的设计工具和方法,可以有效应对复杂多变的工程挑战,确保产品的高性能和可靠性。

剩余29页未读,继续阅读

- 粉丝: 0

- 资源: 14

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 要你命三千,集多种渗透工具于一身的终极武器霸王 .zip

- Python课程设计:手动/自动发射烟花项目实现源代码

- 技术资料分享010511-Translated-IP-test很好的技术资料.zip

- 全志 PMU axp707 完整 规格书 pdf

- 是的讣告哈桑大厦送到华山派的哈桑

- 规范渗透测试报告中的漏洞名称以及修复建议.zip

- 技术资料分享ADPCM格式说明很好的技术资料.zip

- 技术资料分享ADXL345很好的技术资料.zip

- com.tocaboca.tocahairsalon4zxb.apk

- 全志 A133 标案原理图 SCH PDF

- 新能源汽车类型识别,支持yolov8格式的标注,5391张正常采集的车辆信息可识别特斯拉 北汽新能源 宝马 世界 比亚迪秦,比亚迪宋 比亚迪唐 奇瑞 易达 福特 江淮汽车 江淮等.zip

- 计划创建遍布渗透测试平台,主要包括信息收集和漏洞扫描.zip

- 技术资料分享AL422B很好的技术资料.zip

- LeetCode145. 二叉树的后序遍历

- 技术资料分享AMS1117很好的技术资料.zip

- leetCode199. 二叉树的右视图

信息提交成功

信息提交成功