HCS12

Microcontrollers

freescale.com

MC9S12XS256

Reference Manual

Covers MC9S12XS Family

MC9S12XS256

MC9S12XS128

MC9S12XS64

MC9S12XS256RMV1

Rev. 1.09

09/2009

To provide the most up-to-date information, the document revision on the World Wide Web is the most

current. A printed copy may be an earlier revision. To verify you have the latest information available, refer

to: http://freescale.com/

This document contains information for the complete S12XS Family and thus includes a set of separate

flash (FTMR) module sections to cover the whole family. A full list of family members and options is

included in the appendices.

This document contains information for all constituent modules, with the exception of the CPU. For CPU

information please refer to CPU12XV1 in the CPU12/CPU12X Reference Manual.

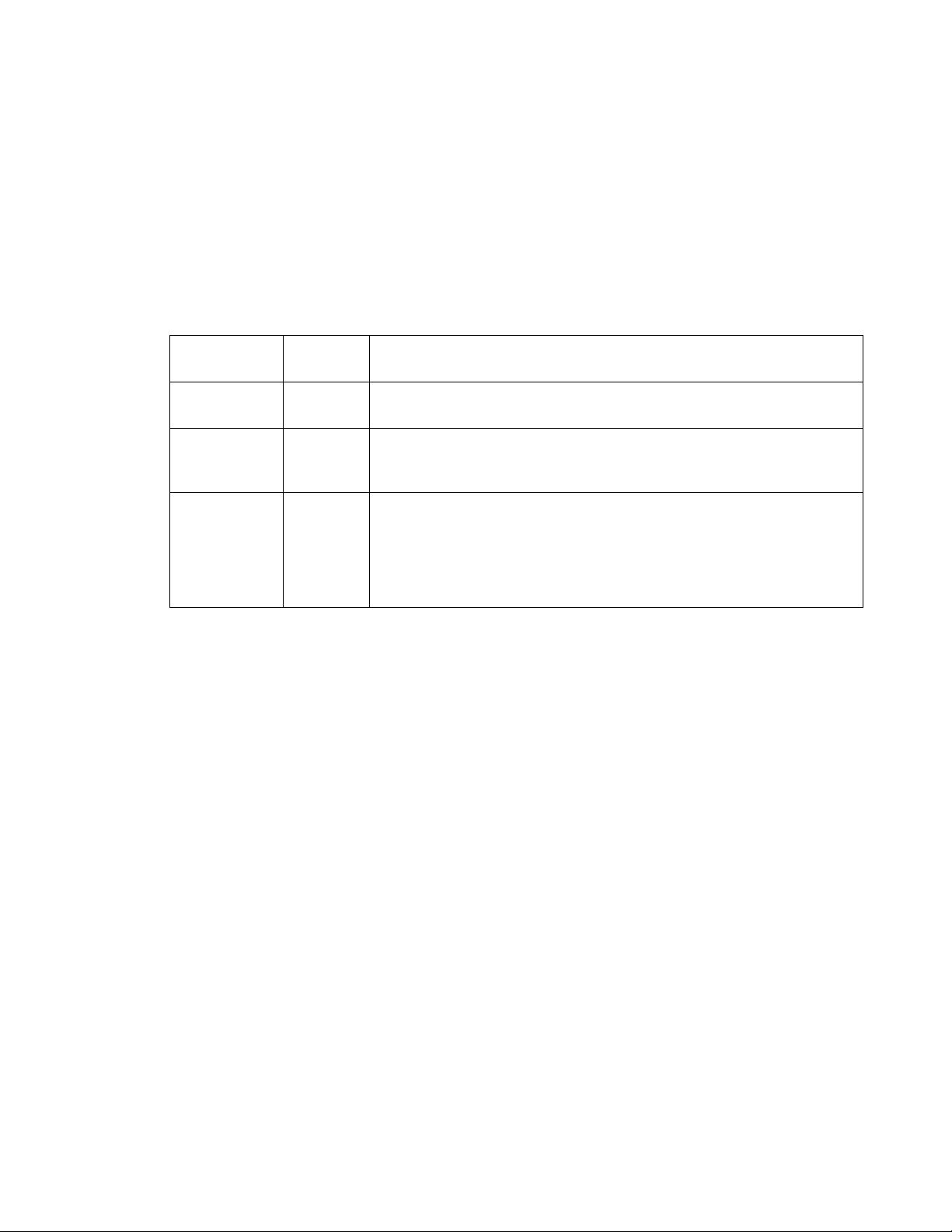

Revision History

Date

Revision

Level

Description

March, 2009 1.07

Corrected pin name in 112LQPF pinout

Updated XMMC, MSCAN, PIM sections

May, 2009 1.08

Removed all KGD references

Corrected Detailed Register Map (FERSTAT)

Corrected statement on VDDA/VDDX protection diodes

September,

2009

1.09

Updated Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1)

Updated Chapter 14 Serial Communication Interface (S12SCIV5)

Updated Chapter 16 Timer Module (TIM16B8CV2) Block Description

Updated Chapter 18 256 KByte Flash Module (S12XFTMR256K1V1)

Updated Chapter 19 128 KByte Flash Module (S12XFTMR128K1V1)

Updated Chapter 20 64 KByte Flash Module (S12XFTMR64K1V1)

S12XS Family Reference Manual, Rev. 1.09

Freescale Semiconductor 3

Chapter 1 Device Overview S12XS Family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Chapter 2 Port Integration Module (S12XSPIMV1) . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Chapter 3 Memory Mapping Control (S12XMMCV4) . . . . . . . . . . . . . . . . . . . . . . . .125

Chapter 4 Interrupt (S12XINTV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

Chapter 5 Background Debug Module (S12XBDMV2) . . . . . . . . . . . . . . . . . . . . . . .165

Chapter 6 S12X Debug (S12XDBGV3) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

Chapter 7 Security (S12XS9SECV2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .227

Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1) . . . . . . . . . . . . . . .233

Chapter 9 Pierce Oscillator (S12XOSCLCPV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . .263

Chapter 10 Analog-to-Digital Converter (ADC12B16CV1) . . . . . . . . . . . . . . . . . . . . .267

Chapter 11 Freescale’s Scalable Controller Area Network (S12MSCANV3) . . . . . .293

Chapter 12 Periodic Interrupt Timer (S12PIT24B4CV1) . . . . . . . . . . . . . . . . . . . . . . .347

Chapter 13 Pulse-Width Modulator (S12PWM8B8CV1) . . . . . . . . . . . . . . . . . . . . . . .363

Chapter 14 Serial Communication Interface (S12SCIV5) . . . . . . . . . . . . . . . . . . . . . .395

Chapter 15 Serial Peripheral Interface (S12SPIV5). . . . . . . . . . . . . . . . . . . . . . . . . . .433

Chapter 16 Timer Module (TIM16B8CV2) Block Description . . . . . . . . . . . . . . . . . . .459

Chapter 17 Voltage Regulator (S12VREGL3V3V1) . . . . . . . . . . . . . . . . . . . . . . . . . . .487

Chapter 18 256 KByte Flash Module (S12XFTMR256K1V1). . . . . . . . . . . . . . . . . . . .505

Chapter 19 128 KByte Flash Module (S12XFTMR128K1V1). . . . . . . . . . . . . . . . . . . .555

Chapter 20 64 KByte Flash Module (S12XFTMR64K1V1). . . . . . . . . . . . . . . . . . . . . .605

Appendix A Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .655

Appendix B Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .696

Appendix C PCB Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .706

Appendix D Derivative Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .710

Appendix E Detailed Register Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .711

Appendix F Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .733

S12XS Family Reference Manual, Rev. 1.09

4 Freescale Semiconductor

S12XS Family Reference Manual, Rev. 1.09

Freescale Semiconductor 5

Chapter 1

Device Overview S12XS Family

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

1.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.1.4 Device Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.1.5 Address Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

1.1.6 Detailed Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1.1.7 Part ID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

1.2 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.2.1 Device Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.2.2 Pin Assignment Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1.2.3 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1.2.4 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

1.3 System Clock Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

1.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

1.4.1 Chip Configuration Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

1.4.2 Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

1.4.3 Freeze Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1.5 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1.6 Resets and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1.6.1 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1.6.2 Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1.6.3 Effects of Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

1.7 ATD0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1.7.1 External Trigger Input Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1.7.2 ATD0 Channel[17] Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1.8 VREG Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1.8.1 Temperature Sensor Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1.9 Oscillator Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Chapter 2

Port Integration Module (S12XSPIMV1)

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

2.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

2.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

2.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

2.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

2.3.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63