serdes handbook

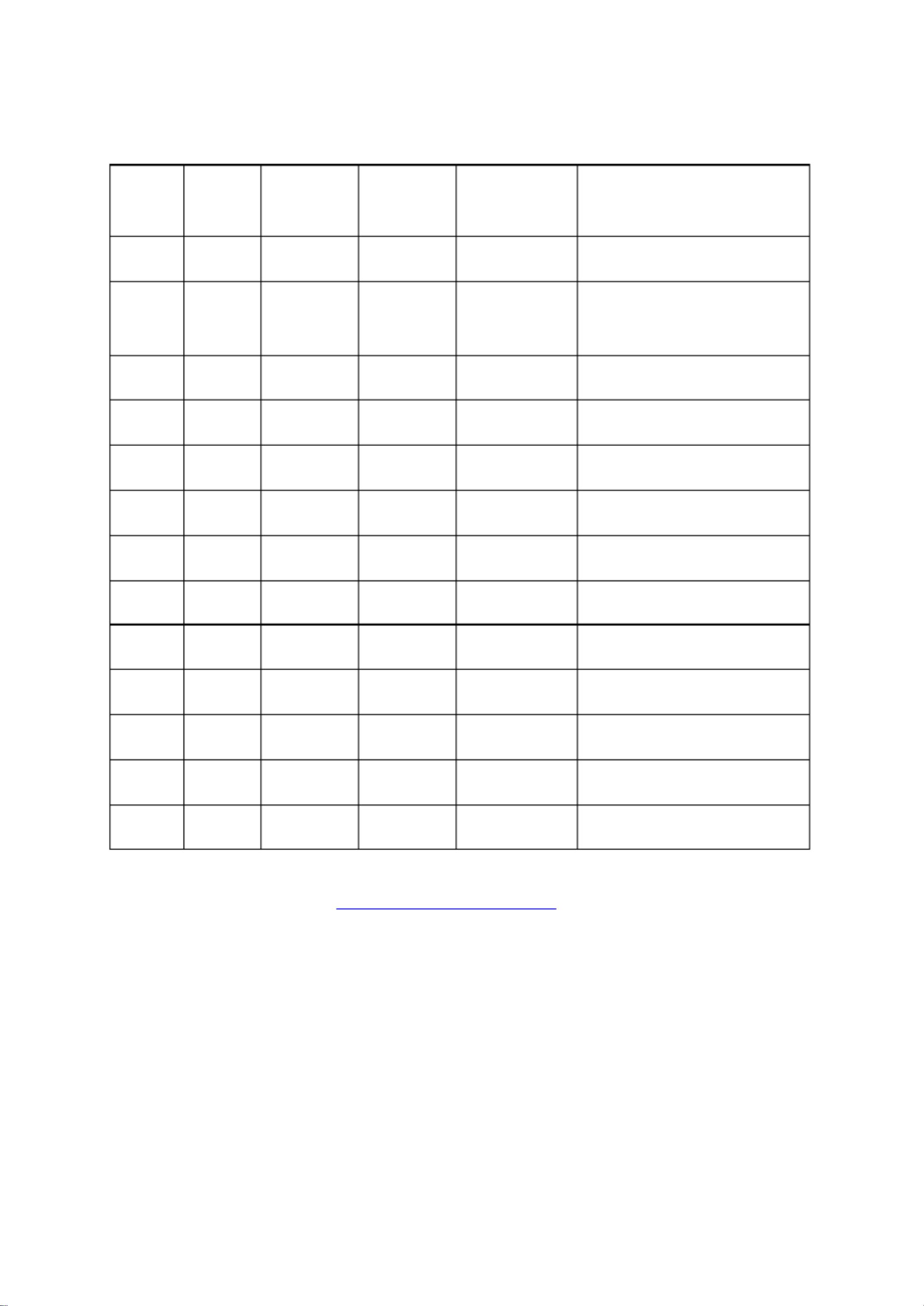

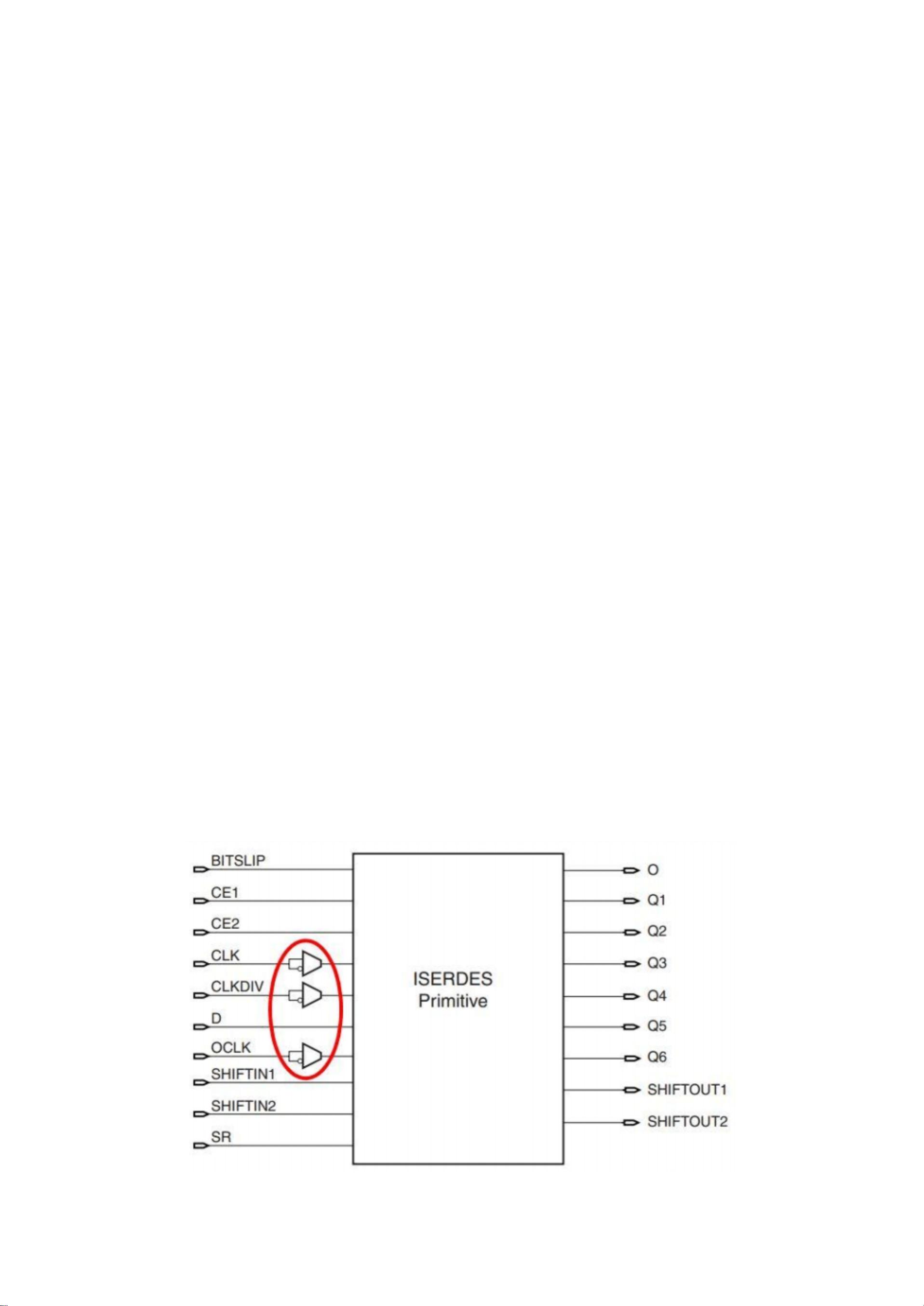

### SERDES FPGA设计手册知识点概览 #### 1. 目的 - **学习与交流**: 本手册旨在帮助读者理解和掌握Xilinx SerDes原语的使用方法,并通过实际项目中的设计案例分享来促进交流与学习。 - **工程实践**: 便于在实际工程项目中有效地运用SerDes技术进行设计。 #### 2. 范围 - **适用器件**: 本文档针对Xilinx V5系列器件,具体包括但不限于Xilinx Virtex-5、Spartan-5等FPGA型号。 - **内容覆盖**: 详细介绍SerDes的基本概念、工作原理及应用场景,特别是针对串行/并行转换器(ISERDES和OSERDES)的设计与实现。 #### 3. 术语 - **ISERDES**: 串行至并行转换器(Serial-to-Parallel Converter),用于将高速串行数据转换为低速并行数据。 - **OSERDES**: 并行至串行转换器(Parallel-to-Serial Converter),用于将低速并行数据转换为高速串行数据。 #### 4. SERDES基础知识 - 待补充内容将会涵盖SerDes的工作原理、基本架构、关键性能指标等方面的理论知识。 #### 5. SERDES应用指南 - 本章节提供了ISERDES和OSERDES的具体设计指导,包括配置参数、设计思路、仿真结果以及时序分析等内容。 ##### 5.1 ISERDES - **5.1.1 ISERDES基元** - 图1展示了ISERDES的基本结构,而图2则进一步揭示了其内部组成单元的结构框图。 - 表1列出了ISERDES的所有端口及其功能描述。 - 表2提供了ISERDES的主要属性及其描述。 - **5.1.2 ISERDES基元的时钟解决方案** - 针对不同的时钟需求提供灵活的解决方案,确保数据传输的稳定性和准确性。 ##### 5.2 OSERDES - **5.2.1 OSERDES组成功能模块** - 介绍了OSERDES的各个组成部分,如移位寄存器、时钟发生器等。 - **5.2.2 OSERDES基元** - 同样给出了OSERDES基元的结构框图及相关端口的描述。 - **5.2.3 OSERDES基元的时钟解决方案** - 提供了针对OSERDES的时钟管理策略,以支持不同速率的数据传输需求。 #### 6. SERDES应用指南 - 本节深入探讨了ISERDES和OSERDES的实际设计案例。 - **6.1 ISERDES设计** - **6.1.1 单个ISERDES单元设计(SDR)** - **ISERDES配置参数**: 列出并解释了配置ISERDES所需的各项参数。 - **设计思想**: 描述了设计ISERDES的核心理念和步骤。 - **仿真结果**: 展示了仿真验证的结果,以证明设计的有效性。 - **ISERDES数据时序** - 输入数据时序: 解释了ISERDES接收数据时的时序要求。 - 输出数据时序: 说明了ISERDES输出数据时的时序特性。 - **6.1.2 单个ISERDES单元设计(DDR)** - 类似于SDR设计,但重点在于双倍数据速率(DDR)的应用场景。 - **6.1.3 ISERDES宽度扩展** - 介绍了如何通过多个ISERDES单元来扩展数据宽度的方法。 - **6.2 OSERDES设计** - **6.2.1 单个OSERDES单元设计(SDR)** - **OSERDES配置参数**: 提供了配置OSERDES所需的关键参数。 - **设计思想**: 阐述了设计OSERDES的思路和步骤。 - **仿真结果**: 通过仿真验证了设计的有效性。 - **6.2.2 单个OSERDES单元设计(DDR)** - 重点关注了DDR模式下的设计细节。 - **6.2.3 OSERDES宽度扩展** - 讲解了如何通过多个OSERDES单元来实现数据宽度的扩展。 #### 总结 本手册通过详细阐述ISERDES和OSERDES的设计方法、参数配置、时序要求等内容,为读者提供了全面而实用的指导。无论是初学者还是有经验的设计者,都可以从中获得宝贵的参考信息和技术建议,从而更好地在Xilinx V5系列器件上实施高效的SerDes设计。

剩余31页未读,继续阅读

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 毕设和企业适用springboot区块链技术类及在线药品管理平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及在线票务管理平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及自动化测试平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链交易平台类及IT资产管理平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及家庭健康管理平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链交易平台类及公寓管理系统源码+论文+视频.zip

- 毕设和企业适用springboot区块链交易平台类及个性化推荐系统源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及跨境物流平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及企业培训平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及企业资源规划平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链交易平台类及健康数据分析系统源码+论文+视频.zip

- 毕设和企业适用springboot商城类及在线平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及视频监控平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及社交电商平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及网络游戏交易平台源码+论文+视频.zip

- 毕设和企业适用springboot商城类及运动赛事管理平台源码+论文+视频.zip

信息提交成功

信息提交成功