信庭-高速PCB设计技术规范-解密资料

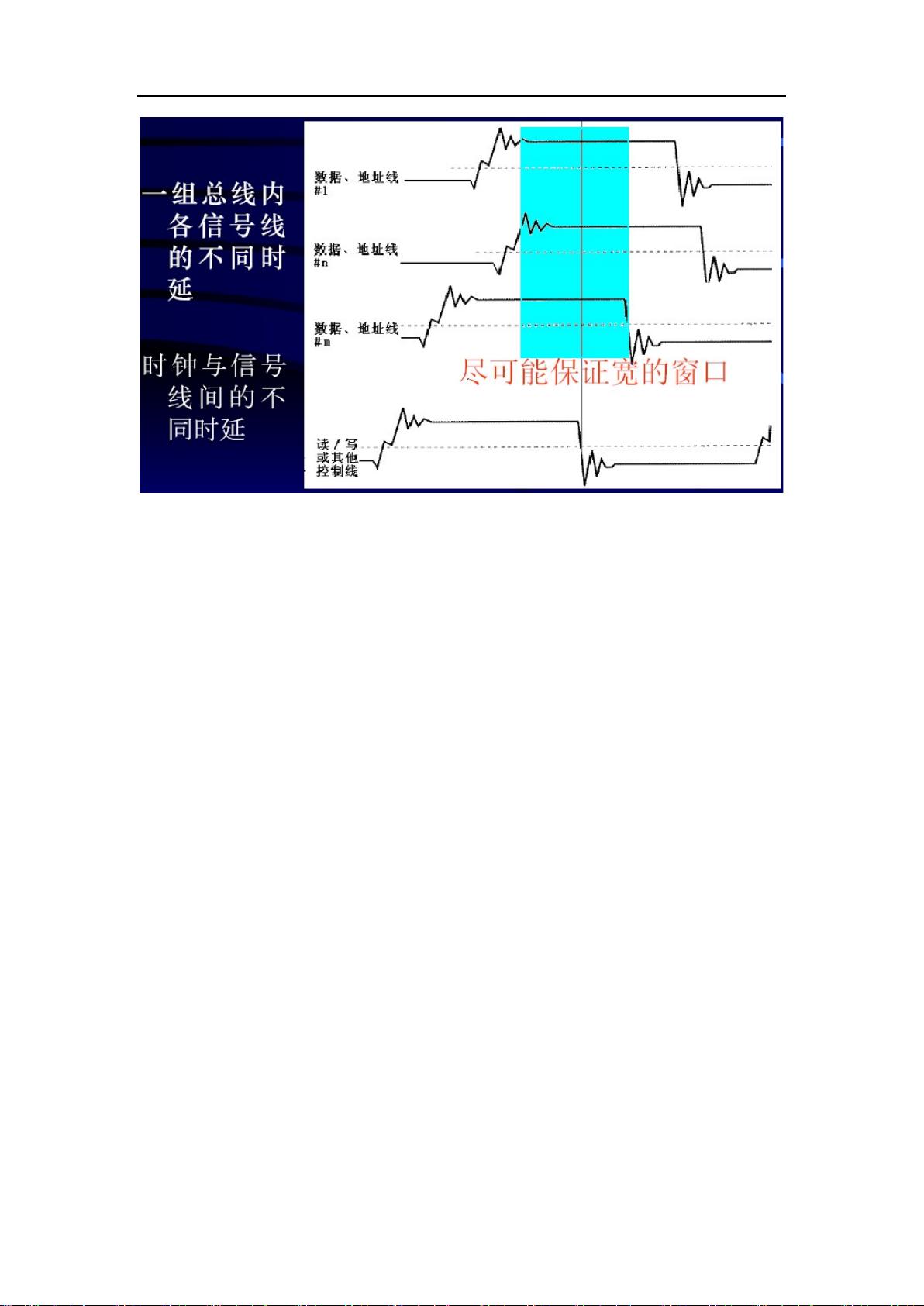

### 高速PCB设计技术规范 #### 一、PCB布线概述 PCB布线是电子产品设计过程中的关键步骤,它决定了电子信号的传输效率和完整性。在布线设计中,不仅要关注布线路径和长度,还要注意信号的传输线效应。高速PCB布线避免输入输出端边线相邻平行,以减少反射干扰,有时需要通过加地线进行隔离。相邻布线层应尽量垂直布线,避免平行布线导致寄生耦合。 #### 二、高速PCB布线技术与挑战 随着电子系统设计的复杂性和集成度的增加,设计师们不得不面对100MHz以上的电路设计。系统工作在50MHz以上时,传输线效应和信号完整性问题将凸显出来。尤其是当系统时钟频率达到120MHz时,不应用高速电路设计知识的PCB将难以工作。因此,掌握高速电路设计技术对电子系统设计师来说至关重要。 #### 三、高速电路与高速信号的定义 一个数字电路是否为高频电路,主要取决于信号的上升沿和下降沿以及系统时钟频率。如果信号的上升沿和下降沿时间小于5ns,或者系统频率超过45MHz~50MHz,都应按照高频电路进行设计。在高速PCB设计中,信号沿时间的减小会导致信号间串扰和电源系统稳定性问题,以及电磁干扰问题的出现。 #### 四、传输线效应与信号完整性 信号的传输发生在信号状态改变的瞬间,如果传输时间小于信号上升或下降时间的一半,反射信号就可能在信号改变状态之前到达驱动端,导致逻辑状态的改变。传输线效应的发生前提条件是信号的线传播延时大于1/2驱动端的信号上升时间。高速逻辑器件的信号上升时间通常为0.2ns,若PCB板上有GaAs芯片,最大布线长度不应超过7.62mm。 #### 五、高速PCB设计的技巧与规范 高速PCB设计中,要综合考虑信号的上升时间与传播延时的比例,以确定高速信号范围。安全区域的条件是信号上升时间是信号传播延时的四倍以上。不确定区域则为信号传播延时的两倍以上但小于四倍。若信号上升时间小于或等于两倍传播延时,信号处于问题区域,需特别关注信号完整性问题。 #### 六、PCB布线技术的实际应用 在2004年的技术条件下,通过Protel 99 SE软件走蛇形线实现过266Mhz DDR SDRAM布线,说明当时的设计人员已经能够利用高级布线软件应对高速信号的设计挑战。盲孔和埋孔技术的引入,解决了贯通孔在高速PCB设计中占用过多布线通道的问题,提高了布线效率。 #### 七、PCB设计过程的体会与真谛 PCB设计过程虽然复杂,但设计师通过长期实践和不断摸索,能够逐渐把握其中的规律和技巧。布线是整个PCB设计中最具有挑战性的部分,设计人员在面对各种问题时,需深入理解信号特性,并结合实践经验,灵活应用布线技术,才能设计出性能优越的高速电路板。 以上内容综合了PCB设计中的布线技巧、信号完整性、传输线效应以及高速电路设计的重要性,为电子工程设计人员提供了实际的设计指导和解决问题的思路。

剩余18页未读,继续阅读

- 粉丝: 98

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功