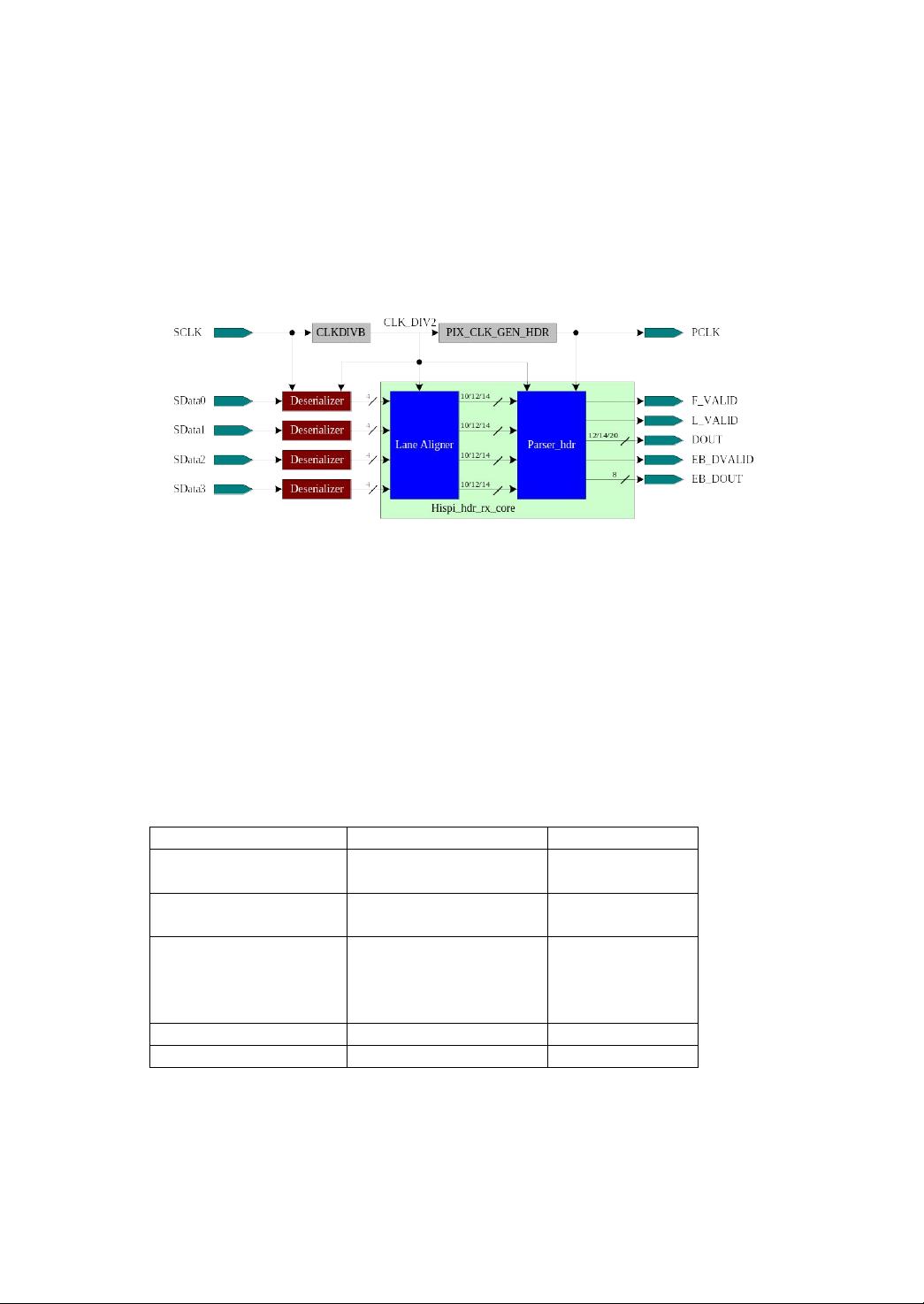

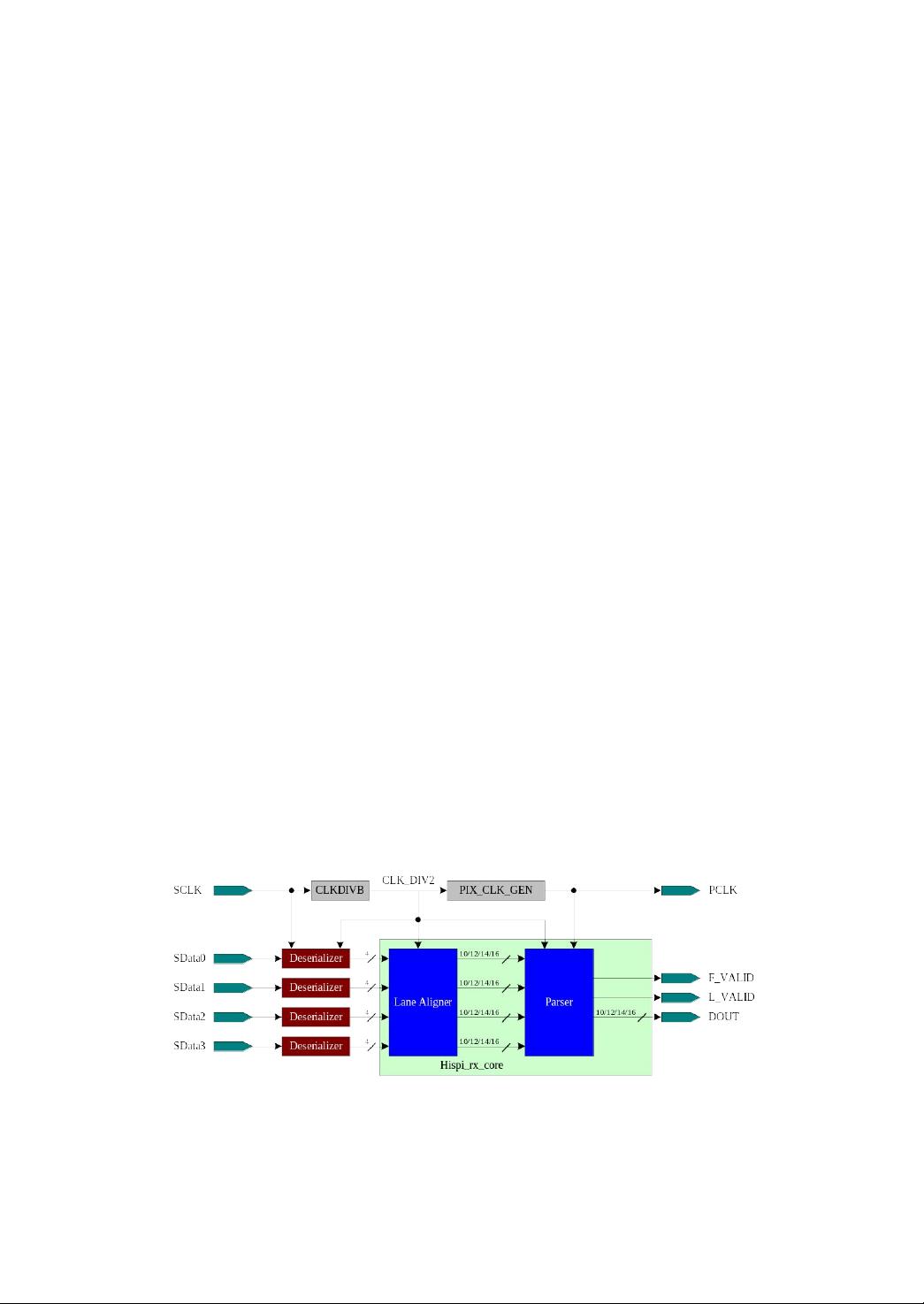

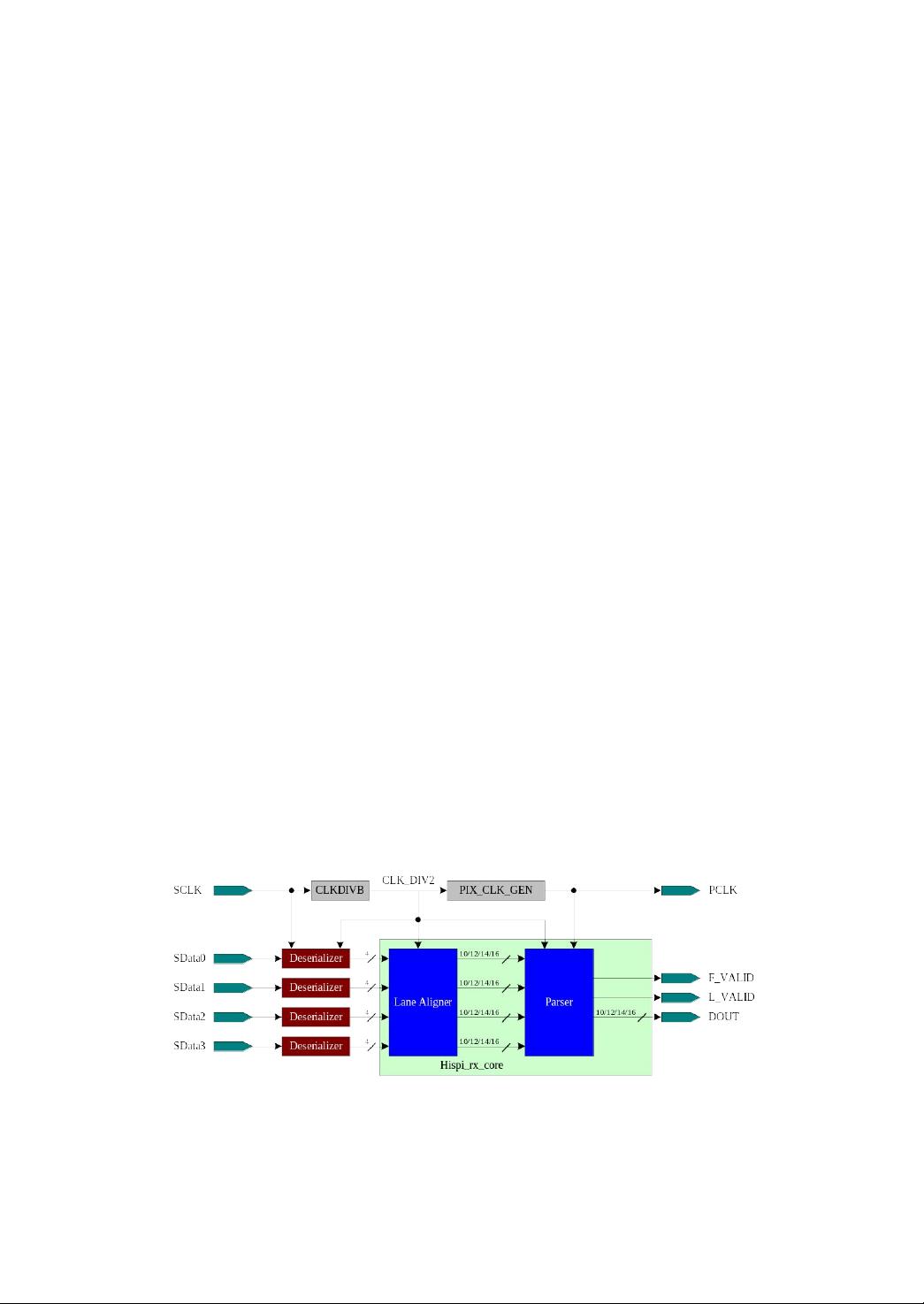

:“lattice hispi”指的是基于Lattice FPGA(Field-Programmable Gate Array,现场可编程门阵列)的HISPI(High-speed Interface for SPI,高速SPI接口)设计,用于处理Aptina传感器的数据。在本例中,Lattice FPGA型号为xp2,它的任务是将Aptina的HISPI串行数据转换为并行格式,以便于进一步的处理或存储。 :“latticeFPGA xp2用来做Aptina hispi转并行数据的实现程序hispi_receiver_v0.4_ngo_XP2_Streaming_S_16s_4s”表明这个项目是一个名为“hispi_receiver”的实现程序,版本号为v0.4,由NGO开发。这个程序专为Lattice FPGA xp2设计,实现了HISPI串行数据到并行数据的转换。其中,“Streaming_S_16s_4s”可能表示该设计支持16位数据宽度的串行流处理,并且有4个时钟周期的延迟(或者缓冲)。 : 1. **Aptina HISPI**:Aptina是一家专注于高性能图像传感器的公司,HISPI是他们的一种高速串行接口,旨在提供高速数据传输,通常用于高清摄像头和其他视觉应用。 2. **转并行**:这是设计的关键部分,意味着系统接收来自HISPI的串行数据流,并将其转化为并行格式,以适应并行处理的需求,例如在FPGA内部进行图像处理或在并行接口如LVDS(低压差分信号)上输出。 【压缩包子文件的文件名称列表】:“hispi_receiver_v0.4_ngo”可能包含以下组件: - **源代码**:设计的VHDL或Verilog代码,用于描述FPGA如何处理HISPI接口和转换数据的逻辑。 - **配置文件**:用于配置Lattice FPGA的.bit或.svf文件,这些文件包含了实现特定功能所需的FPGA门级逻辑配置。 - **仿真模型**:可能包括硬件描述语言(HDL)仿真模型,用于在设计阶段验证逻辑是否正确工作。 - **用户手册或文档**:详细说明如何使用该设计,包括设置指导、连接硬件和软件的说明等。 - **测试平台**:可能包括用于验证设计功能的测试向量或测试脚本。 综合以上信息,这个项目的核心是通过Lattice FPGA xp2实现一个高效的Aptina HISPI串行到并行转换器,这对于需要高速处理或分析Aptina传感器数据的系统非常关键。设计者可能需要熟悉FPGA编程、HISPI协议以及并行数据处理技术。同时,为了确保设计的正确性,还需要进行充分的仿真和硬件测试。

lattice hispi (771个子文件)

lattice hispi (771个子文件)  _info 8KB

_info 8KB _info 3KB

_info 3KB _info 3KB

_info 3KB hispi_design.adf 671B

hispi_design.adf 671B hispi_test_hispi_test.alt 1KB

hispi_test_hispi_test.alt 1KB hispi_test_hispi_test.areasrr 6KB

hispi_test_hispi_test.areasrr 6KB hispi_test_hispi_test_map.asd 2KB

hispi_test_hispi_test_map.asd 2KB 5_1_par.asd 1KB

5_1_par.asd 1KB hispi_test_hispi_test_ngd.asd 21B

hispi_test_hispi_test_ngd.asd 21B verilog.asm 543KB

verilog.asm 543KB verilog.asm 170KB

verilog.asm 170KB verilog.asm 170KB

verilog.asm 170KB verilog.asm 147KB

verilog.asm 147KB verilog.asm 101KB

verilog.asm 101KB verilog.asm 101KB

verilog.asm 101KB verilog.asm 97KB

verilog.asm 97KB verilog.asm 97KB

verilog.asm 97KB verilog.asm 92KB

verilog.asm 92KB verilog.asm 87KB

verilog.asm 87KB verilog.asm 80KB

verilog.asm 80KB verilog.asm 80KB

verilog.asm 80KB verilog.asm 70KB

verilog.asm 70KB verilog.asm 63KB

verilog.asm 63KB verilog.asm 40KB

verilog.asm 40KB verilog.asm 40KB

verilog.asm 40KB verilog.asm 38KB

verilog.asm 38KB verilog.asm 38KB

verilog.asm 38KB verilog.asm 35KB

verilog.asm 35KB verilog.asm 27KB

verilog.asm 27KB verilog.asm 27KB

verilog.asm 27KB verilog.asm 24KB

verilog.asm 24KB verilog.asm 24KB

verilog.asm 24KB verilog.asm 21KB

verilog.asm 21KB verilog.asm 18KB

verilog.asm 18KB verilog.asm 18KB

verilog.asm 18KB verilog.asm 17KB

verilog.asm 17KB verilog.asm 17KB

verilog.asm 17KB verilog.asm 16KB

verilog.asm 16KB verilog.asm 16KB

verilog.asm 16KB verilog.asm 15KB

verilog.asm 15KB verilog.asm 13KB

verilog.asm 13KB verilog.asm 12KB

verilog.asm 12KB verilog.asm 12KB

verilog.asm 12KB verilog.asm 11KB

verilog.asm 11KB verilog.asm 11KB

verilog.asm 11KB verilog.asm 11KB

verilog.asm 11KB verilog.asm 9KB

verilog.asm 9KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 7KB

verilog.asm 7KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 2KB

verilog.asm 2KB verilog.asm 2KB

verilog.asm 2KB verilog.asm 2KB

verilog.asm 2KB hispi_design.aws 185B

hispi_design.aws 185B hispi_rx_top_tb.v.bak 8KB

hispi_rx_top_tb.v.bak 8KB pll_ww12_3lane_xp2.lpc.bak 873B

pll_ww12_3lane_xp2.lpc.bak 873B pll_ww12_1lane_xp2.lpc.bak 872B

pll_ww12_1lane_xp2.lpc.bak 872B pll_ww12_4lane_xp2.lpc.bak 871B

pll_ww12_4lane_xp2.lpc.bak 871B pll_ww12_2lane_xp2.lpc.bak 870B

pll_ww12_2lane_xp2.lpc.bak 870B pll_ww14_4lane_xp2.lpc.bak 865B

pll_ww14_4lane_xp2.lpc.bak 865B pll_ww10_3lane_xp2.lpc.bak 865B

pll_ww10_3lane_xp2.lpc.bak 865B pll_ww16_4lane_xp2.lpc.bak 865B

pll_ww16_4lane_xp2.lpc.bak 865B pll_ww10_4lane_xp2.lpc.bak 865B

pll_ww10_4lane_xp2.lpc.bak 865B pll_ww14_1lane_xp2.lpc.bak 864B

pll_ww14_1lane_xp2.lpc.bak 864B pll_ww16_1lane_xp2.lpc.bak 864B

pll_ww16_1lane_xp2.lpc.bak 864B pll_ww10_1lane_xp2.lpc.bak 864B

pll_ww10_1lane_xp2.lpc.bak 864B pll_ww10_2lane_xp2.lpc.bak 863B

pll_ww10_2lane_xp2.lpc.bak 863B pll_ww14_2lane_xp2.lpc.bak 863B

pll_ww14_2lane_xp2.lpc.bak 863B pll_ww16_2lane_xp2.lpc.bak 863B

pll_ww16_2lane_xp2.lpc.bak 863B pll_ww16_3lane_xp2.lpc.bak 863B

pll_ww16_3lane_xp2.lpc.bak 863B pll_ww14_3lane_xp2.lpc.bak 863B

pll_ww14_3lane_xp2.lpc.bak 863B pll_hdr_ww_xp2.lpc.bak 859B

pll_hdr_ww_xp2.lpc.bak 859B sim.do.bak 754B

sim.do.bak 754B hispi_test_hispi_test.bgn 3KB

hispi_test_hispi_test.bgn 3KB .build_status 2KB

.build_status 2KB hispi_test_hispi_test_map.cam 42KB

hispi_test_hispi_test_map.cam 42KB hispi_test_XP2.ccl 18B

hispi_test_XP2.ccl 18B projlib.cfg 120B

projlib.cfg 120B library.cfg 102B

library.cfg 102B compile.cfg 63B

compile.cfg 63B _primary.dat 11KB

_primary.dat 11KB _primary.dat 11KB

_primary.dat 11KB _primary.dat 8KB

_primary.dat 8KB _primary.dat 8KB

_primary.dat 8KB _primary.dat 8KB

_primary.dat 8KB _primary.dat 8KB

_primary.dat 8KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 6KB

_primary.dat 6KB _primary.dat 6KB

_primary.dat 6KB _primary.dat 5KB

_primary.dat 5KB _primary.dat 5KB

_primary.dat 5KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 2KB

_primary.dat 2KB- 1

- 2

- 3

- 4

- 5

- 6

- 8

- 粉丝: 2

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功