AMBA_AXI总线详解.docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

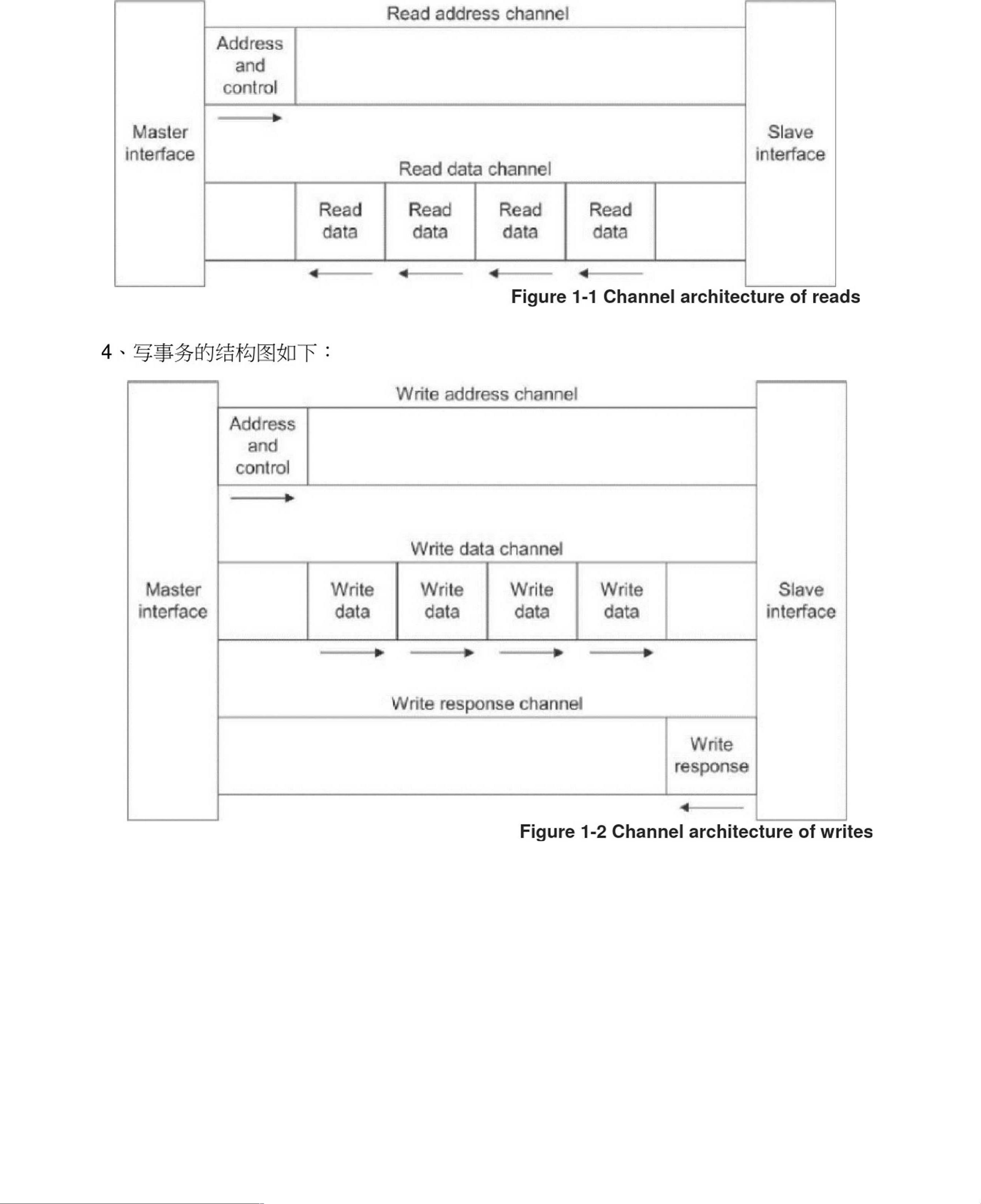

AMBA AXI(Advanced eXtensible Interface)总线协议是ARM公司推出的一种高性能、高带宽、低延迟的片上系统(SoC)通信协议,它是AMBA 3.0架构的重要组成部分。AXI旨在满足现代复杂SoC设计中对超高性能的需求,通过优化的通道设计和高效的传输机制,实现了数据传输的高效性和灵活性。 AXI协议的核心特点包括: 1. **单向通道体系结构**:每个通道只负责单向数据传输,简化了跨时钟域的桥接,降低了延迟和门电路数量,有利于减少功耗。 2. **支持多项数据交换**:通过并行执行突发操作(burst transfers),AXI可以大大提高数据吞吐量,从而在短时间内完成大量数据传输任务,同时满足高性能要求。 3. **独立的地址和数据通道**:地址和数据传输分开处理,允许对每个通道进行独立优化,提升时钟频率,降低延迟。 AXI总线协议包括5个主要的传输通道: 1. **读地址通道(Read Address Channel)**:传输读取操作的地址和控制信息。 2. **写地址通道(Write Address Channel)**:传输写入操作的地址和控制信息。 3. **读数据通道(Read Data Channel)**:从设备到主机的读取数据和响应信息。 4. **写数据通道(Write Data Channel)**:从主机到设备的写入数据。 5. **写响应通道(Write Response Channel)**:设备响应写入操作的状态。 每个事务都由地址和控制信息组成,这些信息在地址通道中传递。读事务和写事务各自拥有独立的地址通道,携带必要的地址和控制信息。传输的有效性由VALID和READY信号协调,信息源通过VALID指示数据有效,目的地通过READY表示准备好接收数据。读数据和写数据通道还包括LAST信号,标记事务的最后一个数据。 突发式读写操作是AXI协议的关键特性,它允许连续的数据传输,无需在每次数据包之间等待。突发式读操作的时序图显示,地址出现在地址总线后,随后数据出现在读数据通道上。RLAST信号标记最后的数据传输。重叠突发式读允许多次读操作同时进行,提高系统效率。突发式写操作则涉及主机先发送地址和控制信息,然后发送数据,设备通过BRESP(写响应)信号确认写操作的成功。 AXI接口和互联模型通常包含多个主设备(Masters)和从设备(Slaves),通过接口和互连网络连接,实现高效的数据交换。在传输过程中,只有当VALID和READY同时为高时,数据和地址信息才被认为是有效的。 总结来说,AMBA AXI总线协议通过其独特的通道设计和传输机制,为高性能SoC设计提供了强大的通信基础,有效地解决了高速数据传输的挑战,确保了系统的高效运行。

剩余36页未读,继续阅读

- 粉丝: 0

- 资源: 9万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于蚁群算法的VRPTW问题求解

- 基于java的车辆充电桩管理系统设计与实现.docx

- 基于java的点餐平台网站设计与实现.docx

- 基于java的高校校园点餐系统设计与实现.docx

- Another-Redis-Desktop-Manager

- 基于java的-家具销售电商平台设计与实现.docx

- 基于java的简历管理系统设计与实现.docx

- 基于java的教师人事档案管理系统设计与实现.docx

- 基于java的考研资讯平台设计与实现.docx

- 基于java的旧物置换网站设计与实现.docx

- 基于java的口腔管理平台设计与实现.docx

- 基于java的篮球论坛系统设计与实现.docx

- 基于java的垃圾分类网站设计与实现.docx

- 基于java的篮球竞赛预约平台设计与实现.docx

- spring-web-5.2.3和spring-webmvc-5.2.3

- 基于java的论坛管理系统设计与实现.docx

信息提交成功

信息提交成功