没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

AMCC PowerPC 460EX 开发方案

关键词: PowerPC,嵌入式系统, Linux,

DDR2, PCI-Express, GbE,千兆以太网,

摘要: AMCC 公司的低成本 PowerPC 460EX 评估套件适用于高性能的 PowerPC 460EX 和

460GT 处理器,它采用 Linux 操作系统,为用户评估处理器和软件开发提供了容易使用的平台.

本文介绍了 PowerPC 460EX 的主要特性和方框图,以及 PowerPC 460EX 评估套件的主要

特性和亮点,方框图以及详细的电路图.

AMCC 公司的低成本 PowerPC 460EX 评估套件适用于高性能的 PowerPC 460EX 和

460GT 处理器,它采用 Linux 操作系统,为用户评估处理器和软件开发提供了容易使用的平台.

本文介绍了 PowerPC 460EX 的主要特性和方框图,以及 PowerPC 460EX 评估套件的主要

特性和亮点,方框图以及详细的电路图.

AMCC Introduces Low-Cost Evaluation Kits for High-Performance PowerPC 460EX

and 460GT Processors

The PowerPC 440 Core

To enhance overall throughput, the PowerPC 440 superscalar core incorporates a 7-stage

pipeline and executes up to two instructions per cycle. Its large 32-KB data cache and

32-KB instruction cache are 64-way setassociative. Versatile configurations enhance

performance tuning while optional parity protection preserves data integrity. For additional

system performance, the PowerPC 440 core includes dynamic branch prediction and 24

multiply accumulate instructions (MAC) that can be used for signal processing or other

numerical tasks, as well as non-blocking caches that can be managed in either

writethrough or write-back mode.

High Performance FPU

In addition to its powerful 440 core, the PowerPC 460EX includes a high-performance

FPU. This superscalar FPU supports both single and double precision operations, and

offers single cycle throughput on most instructions. The result is exceptional performance

in imaging and other calculation intensive applications.

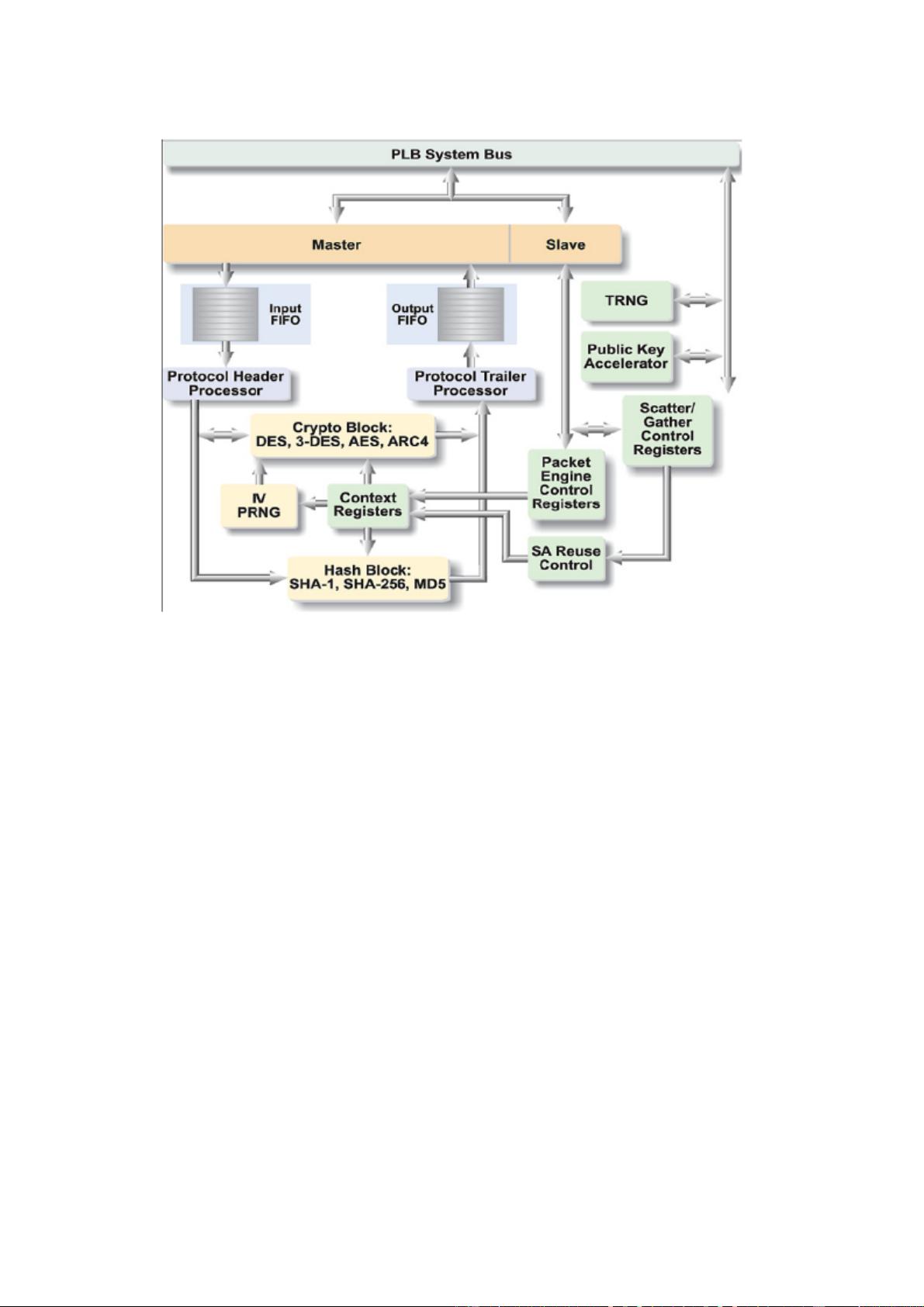

Turbo Security (Optional)

The PPC460EX delivers advanced security capabilities with the optional Turbo Security

Engine. This security engine attaches directly to the PLB4 bus for the fastest possible

throughput between the PPC460 processor, memory, and the security engine itself. The

Turbo Security engines supports DES, 3DES, AES, ARC-4 encryption, MD-5, SHA-1

and SHA-256 hashing. The security engine includes a pseudo random number generator

as well as header and trailer protocol processor. The header/trailer protocol processor

eliminate any need for security processing by the PPC460 processor, freeing it to handle

applicationbased operations, while improving overall security performance. The engine

incorporates an on-chip true random number generator and a public key accelerator.

The algorithms are compliant with FIPS-140-2 and ANSI X9.17 Annex C.

图1.Turbo安全引擎方框图

High-Bandwidth Bus Architecture

The PowerPC 460EX 128-bit processor local bus (PLB) provides a two-way crossbar, with

a separate 128-bit read and 128-bit write data bus for each way. The four 128-bit data

buses may operate concurrently, providing up to 12.8 GBs/s of peak on-chip bandwidth at

200 MHz. The SDRAM controller attaches to both PLB slave segments to provide optimal

access to memory from any other peripheral/core.

Lower bandwidth I/O devices are supported by the onchip peripheral bus (OPB).

Extensive Memory Support

An on-chip double data rate 1/2 (DDR1/2) SDRAM controller provides a 32/64-bit memory

interface with optional error checking and correcting (ECC). It supports four memory

banks of up to 4 GBs each, for a maximum capacity of 16 GBs. An integrated NAND Flash

controller allows up to four banks of Flash memory devices to be connected to the

processor’s external peripheral bus. The Flash controller supports device densities up to

256 Mbytes. It can also interface to an optional SmartMedia card interface. Theses

devices can be accessed much like diskette drives, with available boot capability.

On-Chip Memory

The PowerPC 460EX offers 64 KB of on-chip memory.

PCI Express and PCI Interfaces

The 460EX offers two independent PCI-Express interfaces compliant with PCI-Express

base specification 1.1. One interface has four lanes and supports x4 or x1 configurations.

The other interface has one lane. Both interfaces can be configured as root or end point

ports. In addition, the 460EX offers a 32-bit PCI V2.2 interface and supports frequencies

of up to 66 MHz. Multiple read prefetch and write post buffers enhance throughput, while

the ability to boot the processor from PCI bus memory increases functionality.

SATA

The 440EX offers an on-chip one port SATA controller. Fully compliant with Serial ATA II

specifications, the SATA controller supports both 1.5Gb/s and 3.0 Gb/s.

Dual Ethernets with QoS and TCP/IP Acceleration Hardware For extensive connectivity

options, the 460EX offers two integrated 10/100/1000 Ethernet ports with TCP/IP

Acceleration Hardware, QoS and Jumbo Frame support.

Supports GMII/MII, TBI, RTBI, RGMII, SGMII and SMII interfaces.

USB Interface

The 460EX includes USB 2.0 host and OTG controllers able to operate at 1.5, 12 and

480Mbps.

External Bus Interface

To accommodate connectivity with other devices, the PowerPC 460EX offers a 32-bit bus

supporting up to six ROM, RAM or slave peripheral I/O devices and speeds up to 100

MHz. The 4-Channel DMA is also supported.

The PowerPC 460EX offers support for up to 64 general-purpose I/O (GPIO) and

two IIC controllers. A serial peripheral interface (SPI), also referred to as a serial

communications port (SCP), allows full-duplex, synchronous data exchanges with

other serial devices. The 460EX also supports up to four UARTs in a variety of

configurations. A JTAG interface is provided for debugging purposes.

PowerPC Partners Ecosystem

AMCC's embedded PowerPC processors are supported by an extensive

ecosystem of products and services from a wide range of leading suppliers.

AMCC's PowerPC Partners program includes industry standard providers of:

• Embedded operating systems

• Hardware and software development tools

• Embedded software products and services

• Board-level products

• System design services

• Technical training.

AMCC also provides an evaluation kit for this PowerPC processor, including an

optimized evaluation board as well as sample applications and other software.

PowerPC 460EX 主要特性:

• CPU Speed (frequency): 600 MHz to 1.2GHz

• Performance: 2.0 DMIPS/MHz (2,400 DMIPS @ 1.2 GHz peak)

• 32-KB-I/32-KB-D L1 caches, and 256-KB L2/SRAM with parity protection

• 64KB On Chip Memory

• On-chip double data rate 1/2 (DDR1/2) SDRAM controller with 32/64-bit interface

– Support for four banks of DDR SDRAM memory of up to 4 GB each, maximum

capacity of 16 GBs with CAS latencies of 2, 3, 4, 5, 6, and 7

• Two PCI-Express interfaces, one with four lanes and one with one lane; 2.5-Gbit/s

full duplex per lane; compliant with PCI-Express base specification 1.1; configurable

as root or end point

剩余11页未读,继续阅读

资源评论

eaglelau

- 粉丝: 32

- 资源: 18

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功