没有合适的资源?快使用搜索试试~ 我知道了~

为满足系统设计人员的不同要求,我们提供了多种 Xilinx FPGA 配置方法以及 CPLD 和 PROM 编程方法。本技术文档讲述了不同的配置模式,以期协助设计人员选择恰当的配置或编程方 法。我们举例说明部分最常用的方法,这些方法可用于生产和原型开发。

资源推荐

资源详情

资源评论

XAPP501 (v1.4) 2003 年 7 月 24 日 www.xilinx.com/cn 1

© 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at http://www.xilinx.com/legal.htm. All other

trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this fea-

ture, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you

may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any

warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

提要 本应用指南讨论 Xilinx 的复杂可编程逻辑器件 (CPLD)、现场可编程门阵列 (FPGA) 和 PROM 系

列的配置与编程选项,并演示了各系列最常用的部分配置方法。

简介 为满足系统设计人员的不同要求,我们提供了多种 Xilinx FPGA 配置方法以及 CPLD 和 PROM

编程方法。本技术文档讲述了不同的配置模式,以期协助设计人员选择恰当的配置或编程方

法。我们举例说明部分最常用的方法,这些方法可用于生产和原型开发。

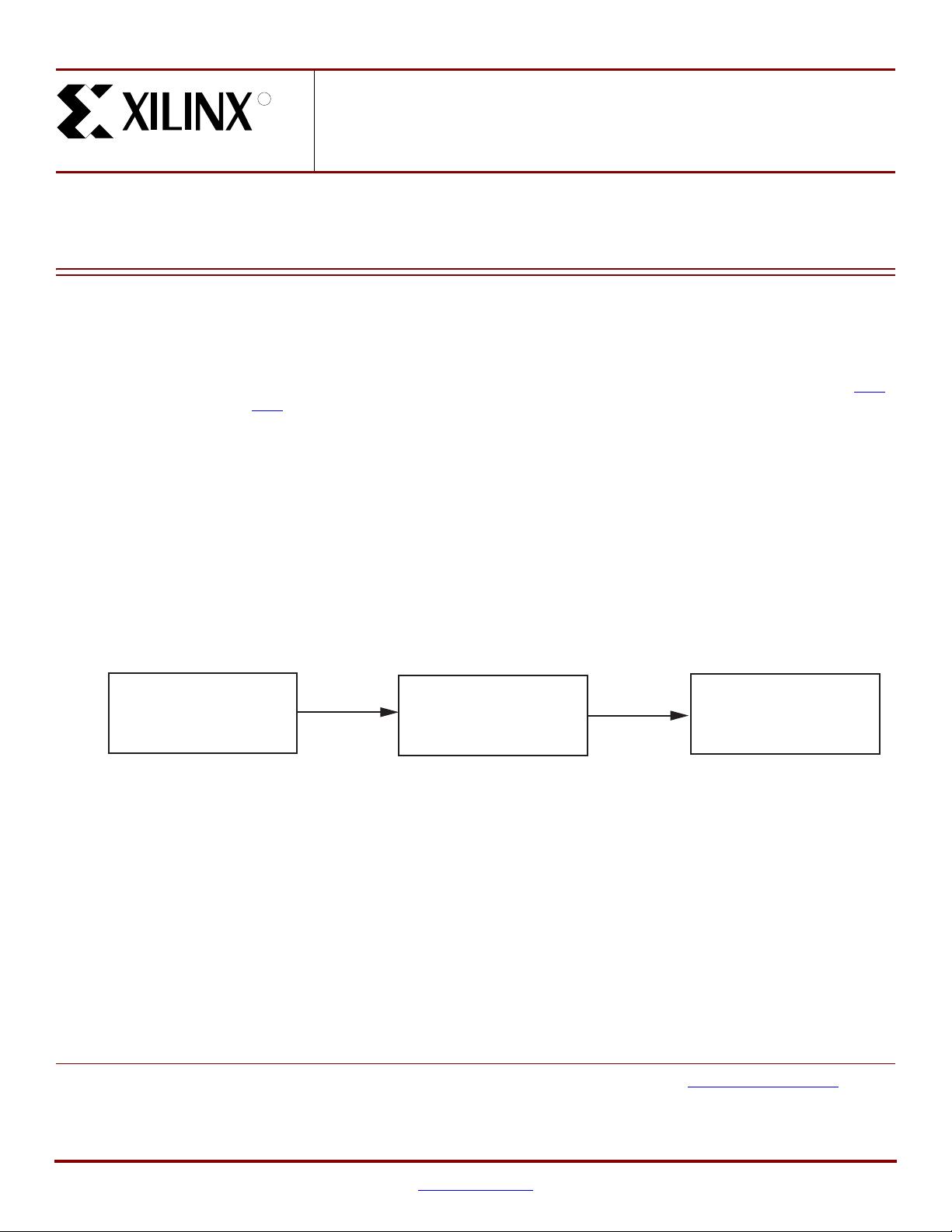

配置 Xilinx 可编程逻辑器件或为其编程需要以下三个常规步骤。有关详情,请参阅 Xilinx 软件

手册。

• 步骤 1 - 设计输入

用软件设计输入工具以 VHDL、Verilog、ABEL 或 Schematic (原理图)创建设计。

• 步骤 2 - 实现

用软件实现工具将设计网表导入所需的 Xilinx 架构,并且生成配置比特流或 JEDEC 文件。

• 步骤 3 - 配置或编程

配置是用外部数据源 (如 PROM、CPLD 或微处理器)将配置数据下载到 FPGA 中的过

程。

编程是将配置数据或程序数据载入 CPLD 或 PROM 的过程。请见图1。

器件定义

Xilinx 生产三种可编程逻辑器件。以下简要说明这些产品类型,以帮助设计人员了解各类型所

需的配置:

应用指南: Xilinx 系列

XAPP501 (v1.4) 2003 年 7 月 24 日

配置快速入门指南

作者: Stephanie Tapp

R

图 1:

配置与编程流程概览

Design Entry

(VHDL, Verilog, ABEL,

or Schematic)

Implementation

(Fitting to Device

Architecture)

Configuration or

Programming

Step 2

Step 1

Step 3

x501_01_010901

EDIF Netlist

Bitstream (.bit),

jedec file (.jed),

or PROM file

(.mcs, .exo, .tek)

2 www.xilinx.com/cn XAPP501 (v1.4) 2003 年 7 月 24 日

配置快速入门指南

R

FPGA

Xilinx FPGA 基于 SRAM 技术,因此是易失性的。也就是说,如果关掉器件的电源,其配置就

会丢失。在生产型环境中,FPGA 通常使用外部存储器件 (如 PROM)防止停电时丢失配置数

据。在没有外部存储器件的情况下,可以用电缆为 FPGA 编程。

PROM

Xilinx PROM 器件是非易失性器件,通常用于存储 Xilinx FPGA 的配置数据。这些器件有两种不

同类型:

• 一次性可编程 (OTP) PROM

• 在系统可编程 (ISP) 的可重复编程 PROM (XC18V00、Platform Flash)

CPLD

Xilinx CPLD 采用 EEPROM 或 FLASH Cell 技术,通常是非易失性的。Xilinx CPLD 不需要外部

存储器件,因而其非易失性致使编程过程中的要求有所不同。

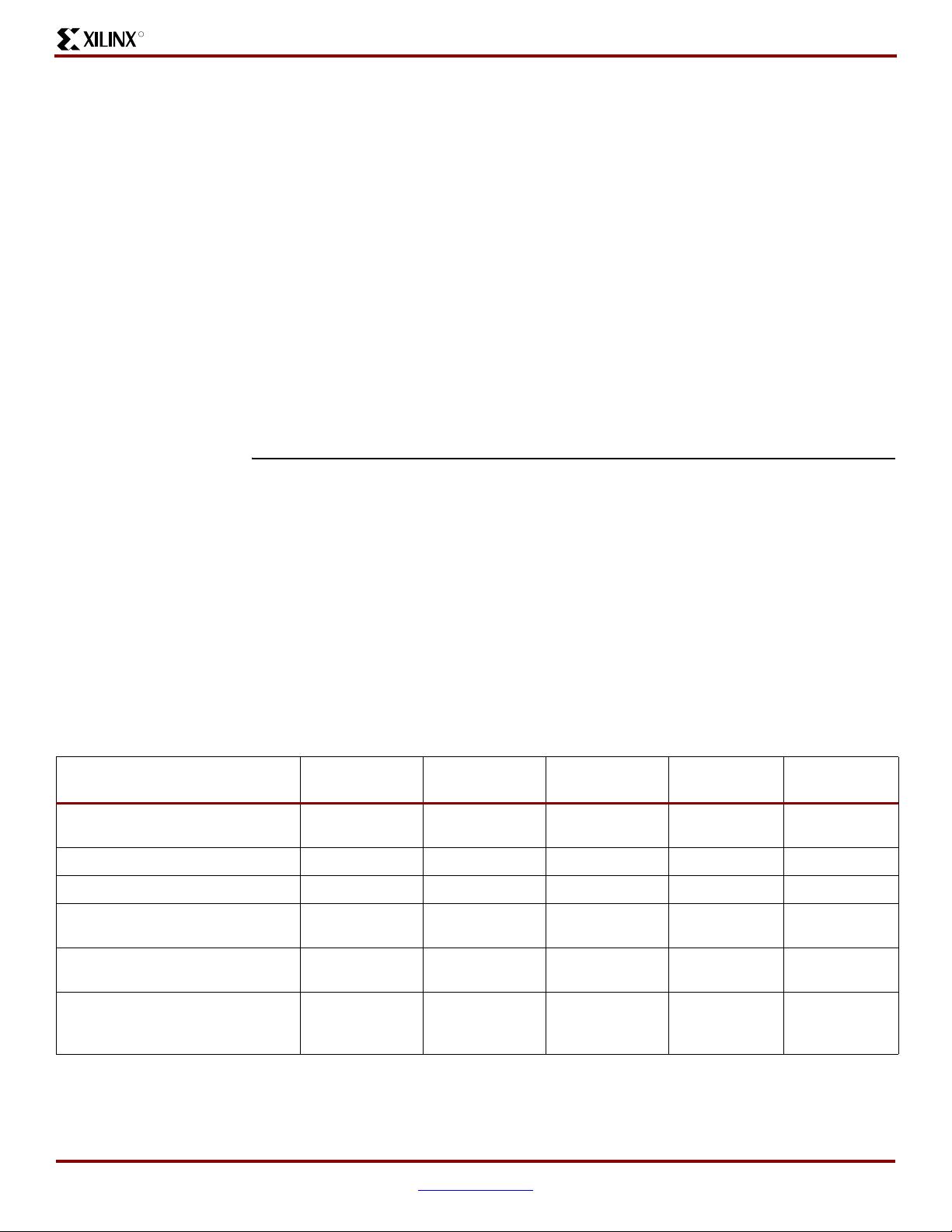

软件工具概述 本部分简述可用于 Xilinx FPGA、CPLD 和 PROM 产品的软件。对于 Xilinx 器件的配置与编程,

表1 所示软件工具有两种用途:

1. 生成配置或编程文件:对于 FPGA 是一个比特流 (.bit 文件),对于 CPLD 是一个 jedec

(.jed) 文件,对于 PROM 是一个 PROM (.mcs、.exo、.tek)文件。

- 设计输入工具 - 生成设计网表。

- 实现工具 - 生成比特流或 JEDEC 文件。

- iMPACT 软件 - 从设计网表生成 PROM 文件。

2. 将文件下载到器件:

-

–iMPACT Xilinx 软件下载工具 (Software Download Tool),用于与边界扫描 (JTAG)

兼容的任意 Xilinx 器件链的编程,或者从串模式或 SelectMAP 模式的 FPGA 器件的编

程。

表 1:

可用的 Xilinx 软件包

产品名称

Foundation

(DE>IMP>CP)

(1)

Foundation ISE

(DE>IMP>CP)

(1)

WebPACK ISE

(DE>IMP>CP)

(1)

Alliance

(IMP>CP)

(1)

WebFITTER

(DE>IMP)

(1)

Virtex™ 系列 / Virtex-II 系列 /

Virtex-II Pro™ 平台 FPGA

XXX

(2)

X

Spartan™-II/IIE/3 系列 (FPGA)

XXX

(2)

X

XC9500/XL/XV 系列 (CPLD)

XXXXX

CoolRunner™/CoolRunner-II™

系列 (CPLD)

XXXXX

XC18V00/Platform Flash 系列

(ISP PROM)

XXXX

XC1700L、XC17S00A、

XC1700E、XC17V00、SC17S00

系列 (OTP PROM)

XXXX

注:

1. DE = 包括设计输入软件; IMP = 包括实现软件; CP = 包括配置或编程软件。

2. 有关对 FPGA 器件的支持,请参阅最新版 WebPACK。

配置快速入门指南

XAPP501 (v1.4) 2003 年 7 月 24 日 www.xilinx.com/cn 3

R

选择配置模式 确定配置环境之前,重要的是要了解可用的配置模式。表2 所示为各系列支持的模式,表后给

出了对各模式的说明。

FPGA 支持的模式

JTAG 或边界扫描模式

JTAG 或边界扫描模式是一种行业标准 (IEEE 1149.1 或 1532)串行编程模式。此模式用通过

电缆、微处理器或其他器件提供的外部逻辑驱动 JTAG 专用引脚:测试数据输入 (TDI) 引脚、

测试模式选择 (TMS) 引脚和测试时钟 (TCK) 引脚。这种模式因其标准化程度和可通过同样四个

JTAG 引脚为 FPGA、CPLD 和 PROM 编程的能力而广受欢迎。在这种模式下,数据以每 TCK

一位的速度加载。

SelectMAP/ 从并模式

Virtex 系列支持 SelectMAP™ 模式,而 Spartan-II 系列支持从并模式。SelectMAP/ 从并模式

允许通过字节宽度端口并行读写。这种模式需要外部时钟源、微处理器、下载电缆或其他

FPGA。在这种模式下,数据以每 CCLK 一字节的速度加载。当配置速度是重要因素时,这种

模式通常在 Virtex/Virtex-E/Virtex-II、Virtex-II Pro 或 Spartan-II/IE/3 器件上用作配置模式。

主串模式

所有 Xilinx FPGA 系列都支持主串模式,但 Xilinx CPLD 不支持这种模式。这是最简单的 FPGA

配置方法。FPGA 从串行 PROM 加载配置数据。这种模式由 FPGA 提供时钟,实际上是加载其

自身并使用其内部振荡器,该振荡器驱动配置时钟。FPGA 提供所有控制逻辑。在这种模式

下,数据以每 CCLK 一位的速度加载。

从串模式

像主串模式一样,所有 Xilinx FPGA 系列都支持从串模式,但 Xilinx CPLD 不支持这种模式。这

种模式使用外部时钟,允许菊花链配置。这种模式需要一个外部时钟 (如微处理器)、另一个

FPGA 或一条下载电缆。在这种模式下,数据以每 CCLK 一位的速度加载。

表 2:

各系列支持的模式

JTAG 模式

SelectMAP/

从并模式 主串模式 从串模式 独立编程器模式

Virtex 系列 / Virtex-II 系列

/Virtex-II Pro 平台 FPGA

XXXX

Spartan-II/IIE 系列 (FPGA) XXXX

XC9500-XL/XV 系列 (CPLD) XX

CoolRunner/CoolRunner-II

系列 (CPLD)

XX

XC18V00/Platform Flash ISP

PROM 系列

XX

OTP PROM 系列 X

:

剩余15页未读,继续阅读

资源评论

drjiachen

- 粉丝: 172

- 资源: 2138

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功