MIG2.0 是 Xilinx 内嵌在 ISE 中用来生成各种 IP 核的软件工具,可以用它来直接生成

DDR2 控制器设计模块,模块包含可自由修改的 HDL 源代码和约束文件。用户可以在 MIG

的 GUI 图形界面根据所选的存储器件选择对应模板、总线宽度和速度级别,并设置 CAS 延

迟、突发长度、引脚分配等关键参数。如果所选器件与 MIG 所列模板不相符,可在代码生

成后灵活修改这些代码。

DDR2 SDRAM 控制器参考设计主要包含四个模块:Infrastructure module(基础模块)、

Data_Path module(数据通道模块)、Controller module(控制模块)和 IOBs module(输入输

出接口模块)。

Infrastructure module 产生控制器工作的时钟和复位信号,时钟信号由内部的 DCM(时

钟管理单元)对外部输入的时钟倍频产生,模块还包含一个延迟校准监视器,用来校准读

数据选通脉冲(DQS)对读数据(DQ)的延迟,使读数据选通脉冲边沿正确对齐 DQ 有效

窗口的中间位置,以便正确锁存读数据。

Data_Path module 负责传输数据,在写操作时将写数据传送给 DDR2 SDRAM;在读操

作时将 DDR2 发送过来的数据寄存并同步到系统时钟去。

Controller module 负责 DDR2 SDRAM 的上电初始化,在初始化后接收用户的指令并将

其译码产生读写和相关的控制信号,此外控制器也为其他模块提供控制信号以辅助这些模

块完成其功能。

控制器所有的输入/输出信号都在 IOBs module 中被接收或者发送,而所有地址和控制

信号在 IOB 中都用触发器打一拍后再被送出,以最大限度的满足 DDR2 SDRAM 的建立和

保持时间。

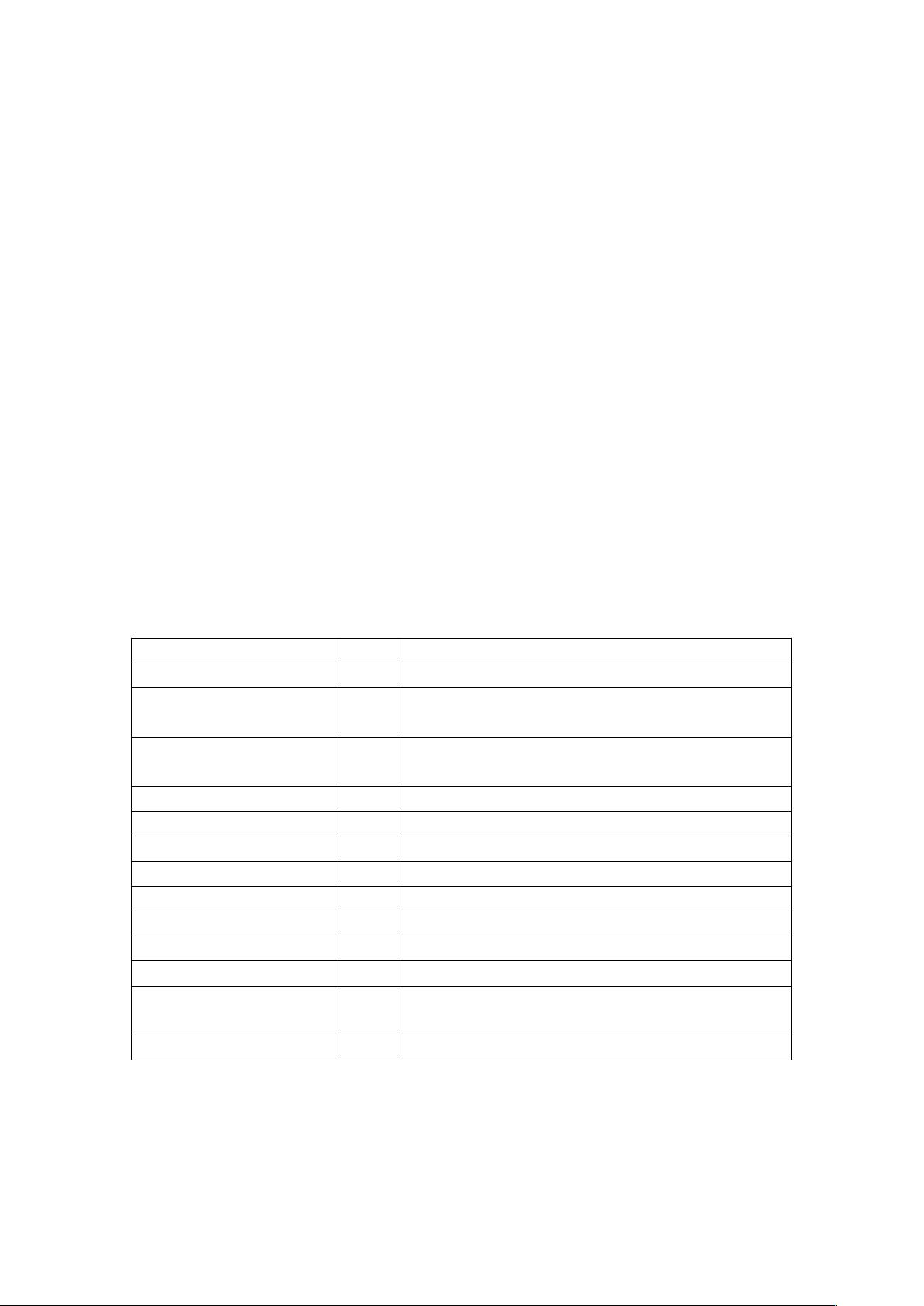

用户接口信号

信号名称 方向 描述

reset_in I

系统复位

user_input_data[31:0] I

写数据,DQS 的上升沿传送写数据的高 16 位,DQS

的下降沿传送写数据的低 16 位

user_data_mask[3:0] I

写数据的数据屏蔽位,高 2 位负责上升沿数据的屏

蔽,低 2 位负责下降沿数据的屏蔽

user_output_data[31:0] O

读出数据

user_data_valid I

为‘1’时代表读出数据有效

user_input_address[22:0] I

行列地址,行地址在高位,列地址在低位

user_bank_address[1:0] I

DDR2 SDRAM 的 bank 地址

user_command_reg[3:0] I

DDR2 控制器的命令寄存器

user_cmd_ack I

为‘0’代表允许用户发出命令

init_val I

为‘1’代表初始化操作已完成

burst_done O

为‘1’时终止突发操作

rst_dqs_div_in I

在读操作时被置‘0’,由控制器自动产生,用户无需输

入

rst_dqs_div_out O

在外部与 rst_dqs_div_in 连接

系统上电后,用户发出初始化命令,控制器负责对 DDR2 进行寄存器的配置及其他初

始化操作,待初始化完成后,控制器置 init_val 为‘1’,然后用户就可以继续对 DDR2

SDRAM 进行读写等操作。