AD9371/AD9375 System Development User Guide

UG-992

One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

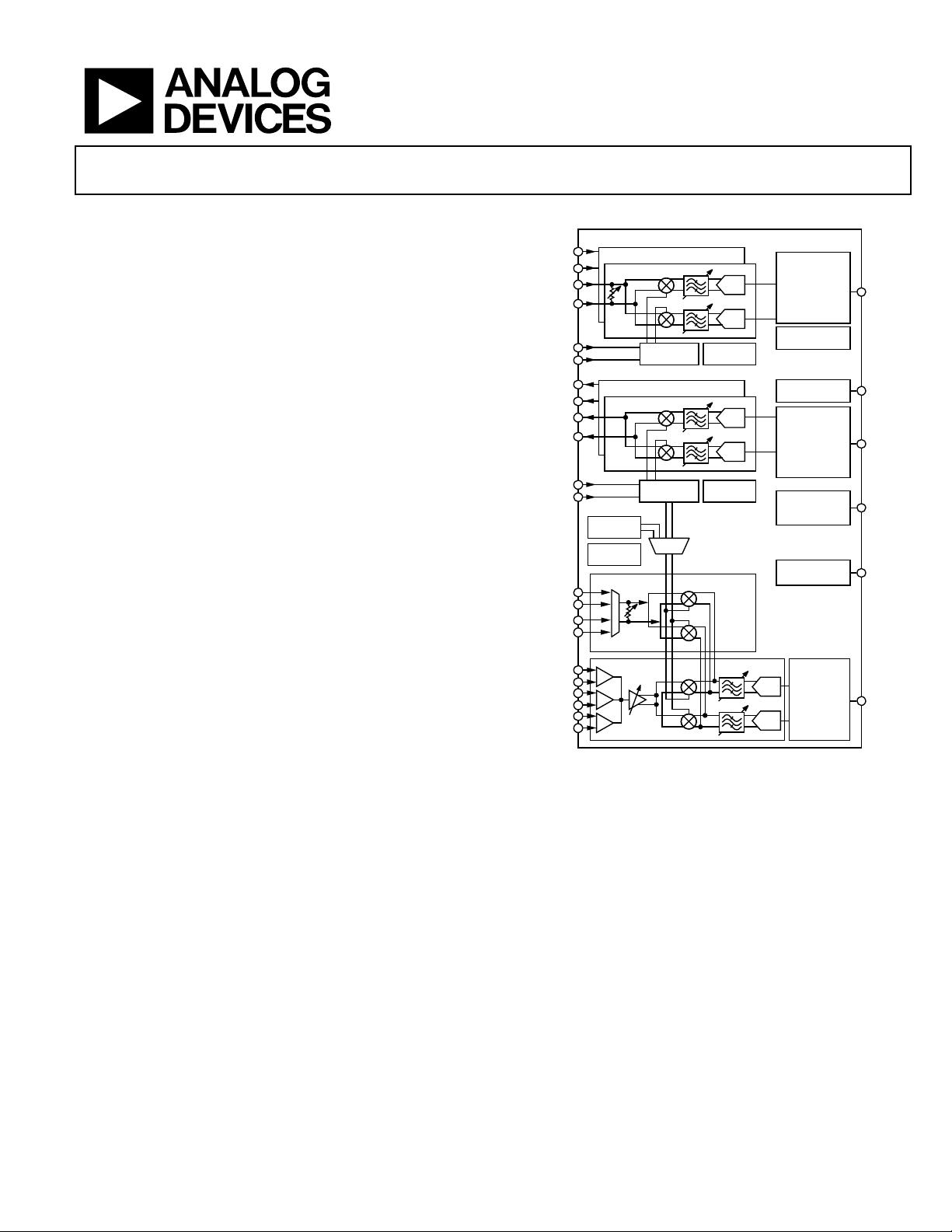

System Development User Guide for the AD9371 and AD9375 Integrated Dual-

Channel RF Transceivers

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

Rev. B | Page 1 of 360

INTRODUCTION

This user guide is the main source of information for systems

engineers and software developers using the AD9371 family of

software defined radio transceivers. This family includes the

AD9371 and the AD9375. For this the user guide, these devices

are interchangeable unless otherwise stated. The sections in this

user guide are organized to simplify navigation for users to find

the information pertinent to their area of interest.

UG-992 AD9371/AD9375 System Development User Guide

Rev. B | Page 2 of 360

TABLE OF CONTENTS

Introduction ...................................................................................... 1

Revision History ............................................................................... 4

User Guide Section Description ..................................................... 7

System Overview .............................................................................. 8

System Architecture Description .................................................. 11

Software Architecture ................................................................ 11

Folder Structure .......................................................................... 12

Software Integration ....................................................................... 13

Modifying common.c ................................................................ 13

Developing the Application ...................................................... 14

Serial Peripheral Interface (SPI) ................................................... 17

SPI Configuration Using API Function .................................. 17

SPI Bus Signals ............................................................................ 17

SPI Data Transfer Protocol ........................................................ 18

Timing Diagrams ........................................................................ 19

JESD204B Interface ........................................................................ 21

Receivers (ADC) Datapath ........................................................ 22

Transmitters (DAC) Datapath .................................................. 41

Link Establishment ..................................................................... 55

Hardware Considerations for SYNC Signals .............................. 56

Compatibility with Xilinx JESD204B FPGA IP ..................... 56

Multichip Synchronization ........................................................ 56

Multichip API Function Description ....................................... 58

System Initialization ....................................................................... 59

Modification of common.c for User Code Integration ......... 59

Data Structure Member Initialization ..................................... 59

Initialization Sequence............................................................... 61

Example Code ............................................................................. 61

Source Code Examples .............................................................. 62

Quadrature Error Correction, Calibration, and ARM

Configuration .................................................................................. 83

ARM State Machine Overview ................................................. 83

Loading the ARM ....................................................................... 83

Initial ARM Calibrations ........................................................... 84

Tracking Calibrations ................................................................. 85

Tracking Calibration Scheduler ................................................ 85

System Considerations for ARM Calibrations ....................... 88

ARM GPIOs ................................................................................ 96

Initial Calibration Errors ........................................................... 97

Tracking Calibration Errors ...................................................... 99

Reading the ARM Version ........................................................ 99

Performing an ARM Memory Dump ...................................... 99

System Control.............................................................................. 102

Control of Signal Chains (Tx/Rx) .......................................... 102

ORx Path Control ..................................................................... 104

ARM GPIO Operation ............................................................ 107

Tx Power Control ......................................................................... 108

Power Amplifier (PA) Protection ............................................... 109

PA Error Flag ............................................................................ 109

Protection Algorithm ............................................................... 109

API Commands for PA Protection ........................................ 111

Reference Clock and SYSREF Connections .............................. 113

Connections for External Clock (DEV_CLK_IN) ............... 113

DEV_CLK Phase Noise Requirements .................................. 113

SYSREF Requirements ............................................................. 114

Synthesizer Configuration........................................................... 116

Connections for External LO ................................................. 117

Software Configuration ........................................................... 119

RF PLL Frequency Change Procedure .................................. 122

RF PLL Resolution Limitations .............................................. 126

Gain Control ................................................................................. 127

Variable Gain Elements in the Receiver Datapaths .................. 127

Gain Table Format .................................................................... 129

Gain Table Programming Description .................................. 132

Rx Gain Delay ........................................................................... 132

Manual Gain Control, Hybrid Mode, and Automatic Gain

Control Overview ..................................................................... 134

Manual Gain Control ............................................................... 135

Hybrid Gain Control................................................................ 136

Automatic Gain Control (AGC) ............................................. 137

AGC API Commands .............................................................. 143

Application Programming Interface (API) Programming

Summary ................................................................................... 144

Summary of the AGC Parameters .......................................... 154

Digital Gain Compensation, Slicer, and Floating Point

Formatter ................................................................................... 155

Slicer API Commands and GPIO Information .................... 159

Floating Point API Commands .............................................. 161

Filter Configuration ..................................................................... 163

Receiver Signal Path ................................................................. 163

Rx Signal Path Example ........................................................... 165

AD9371/AD9375 System Development User Guide UG-992

Rev. B | Page 3 of 360

Transmitter Signal Path ........................................................... 166

Tx Signal Path Example ........................................................... 167

Observation Receivers Signal Path ........................................ 168

Observation Receiver Signal Path Example.......................... 169

Application Programming Interface (API) Data Structures

and API Commands ................................................................ 170

Observation Receiver (ORx) ....................................................... 172

Observation System Receiver Details .................................... 173

ORx AGC, Hybrid, and MGC ................................................ 175

Observation System Receiver Front-End Programming .... 176

TDD Configuration and Setup ................................................... 178

TDD in the Mykonos Evaluation System ............................. 178

API/DLL Commands for TDD Configuration .................... 190

General-Purpose Input/Output (GPIO) Configuration ......... 195

GPIO Operation ....................................................................... 196

GPIO Manual Mode ................................................................ 201

Monitor Output ........................................................................ 202

ARM GPIO Interface ............................................................... 209

Tx Attenuation Control ........................................................... 213

Secondary Serial Peripheral Interface (SPI2) ....................... 216

Rx Manual Gain Control ......................................................... 218

3.3 V General-Purpose Input/Output Overview ..................... 221

3.3 V General-Purpose Input/Output control ..................... 223

General-Purpose Interrupt Overview ....................................... 225

Auxiliary Converters—AUXDAC_x, AUXADC_x, and

Temperature Sensor ..................................................................... 227

Auxiliary DACs ........................................................................ 227

Auxiliary ADC .......................................................................... 230

Temperature Sensor ................................................................. 232

RF Port Interface .......................................................................... 236

Series and Parallel Impedance Models .................................. 236

RF Port Impedance Data ......................................................... 237

Transmitter Bias and Port Interface ....................................... 245

General Receiver Path Interface ............................................. 246

Impedance Matching Network ............................................... 249

Board Layout Design Recommendations ............................. 255

Printed Circuit Board Layout Guidelines ................................. 256

PCB Material and Stack Up Selection ................................... 256

Fanout and Trace Space Guidelines ....................................... 258

Component Placement and Routing Priorities .................... 259

RF and JESD204B Transmission Line Layout ...................... 264

Isolation Techniques Used on the ADRV9371-N/PCBZ

Evaluation Board ....................................................................... 273

Unused Balls .............................................................................. 276

Power Management Considerations ........................................... 277

Power Supply Sequence ............................................................ 277

Power Distribution for Different Power Supply Domains .. 277

ADRV9371-N/PCBZ Evaluation Board Power Supply Block

Diagram ...................................................................................... 279

RF and Clock Synthesizer Supplies......................................... 280

Demonstration System Overview ............................................... 281

Initial Setup ................................................................................ 281

Hardware and Software Requirements .................................. 281

Hardware Setup for External Tx LO Leakage Calibration .. 285

Hardware Operation ................................................................. 286

Transceiver Evaluation Software ................................................. 287

Installation ................................................................................. 287

Starting the Transceiver Evaluation Software (TES) ............ 287

Normal Operation .................................................................... 289

Configuring the AD9371 ......................................................... 290

Programming the Evaluation System ..................................... 301

Other TES Features ................................................................... 302

Receiver Setup ........................................................................... 305

Transmitter Setup ...................................................................... 308

TDD Mode ................................................................................. 310

Scripting ..................................................................................... 315

DPD, CLGC, and VSWR Measurement (AD9375 Only) ........ 319

DPD Overview .......................................................................... 319

CLGC Overview ........................................................................ 323

Voltage Standing Wave Ratio Measurement Overview ....... 323

DPD GUI ........................................................................................ 324

Waveform Setup ........................................................................ 325

DPD Setup ................................................................................. 327

PA Calibration Configuration ................................................. 329

Error Messages and Debug Information................................ 331

DPD API ........................................................................................ 332

ARM Setup Commands ........................................................... 332

DPD API Data Structures ........................................................ 334

DPD Functionality API Functions ......................................... 339

CLGC Tracking Calibration......................................................... 341

CLGC Configuration ................................................................ 341

CLGC API ...................................................................................... 342

CLGC API Data Structures...................................................... 342

UG-992 AD9371/AD9375 System Development User Guide

Rev. B | Page 4 of 360

CLGC Functionality API Functions ...................................... 345

VSWR Tracking Calibration ....................................................... 346

VSWR Monitoring ................................................................... 346

VSWR API ..................................................................................... 347

VSWR API Data Structures .................................................... 347

VSWR Functionality API Functions ...................................... 350

Systems Design Considerations .................................................. 351

DPD Tuning Procedure ........................................................... 351

DPD Model Save/Restore Functionality ............................... 351

Guidelines for Developing and Troubleshooting a DPD

System ........................................................................................ 352

Designing a System for a TDD Application .......................... 353

External Loopback Flatness Requirements ........................... 354

CLGC Convergence Time ....................................................... 356

DPD Limitations ...................................................................... 356

Other Considerations .............................................................. 356

Typical Test Setup And DPD Performance ............................... 357

TDD Setup Instructions .............................................................. 359

REVISION HISTORY

5/2017—Rev. A to Rev. B

Added AD9375 .............................................................. Throughout

Updated Layout ................................................................... Universal

Changes to Title and Introduction ................................................. 1

Added User Guide Section Description Section .......................... 7

Changes to Overview Section ......................................................... 8

Added Figure 2; Renumbered Sequentially ................................ 10

Changes to Table 5 .......................................................................... 22

Changes to MYKONOS_setupDeserializers(…) Section ......... 46

Changes to External Tx LO Leakage Initial Calibration Section .... 90

Changes to System Considerations for Tracking Calibrations

Section .............................................................................................. 91

Changes to External Channel Section ......................................... 96

Changes to ORx Path Control Section ...................................... 104

Added Power Amplifier (PA) Protection Section and Table 92;

Renumbered Sequentially ............................................................ 109

Add Figure 48 ................................................................................ 110

Changes to MYKONOS_setupPaProtection(…) Section ....... 111

Changes to MYKONOS_getPaProtectErrorFlagStatus(…)

Section ............................................................................................ 112

Changes to Table 95 Caption ...................................................... 117

Changes to RF PLL Frequency Change Procedure .................. 122

Changes to RF PLL Resolution Limitations Section ................ 126

Changes to Gain Control Section ....................................................... 127

Changed Receiver Datapath—Variable Gain Elements Section to

Variable Gain Elements in the Receiver Datapath Section ............ 127

Changes to Figure 59 and Figure 60 ........................................... 132

Changes to PMD Measurement Duration Section and PMD

Measurement Configuration Section ......................................... 153

Changes to Real IF Section .......................................................... 164

Changes to Rx Signal Path Example Section, Figure 77, and

Figure 78 ........................................................................................ 165

Changes to THB2 Section and THB1 Section .......................... 166

Changes to Figure 85 .................................................................... 169

Changes to Figure 87 .................................................................... 170

Changed Programming Filter Settings to the AD9371 via API

Section to Programming Filter Settings via API Section ........ 171

Changes to Datapath Trigger Modes Section and Table 138 .. 183

Changes to Table 139 .................................................................... 184

Changes to Table 155 ................................................................... 207

Changes to MYKONOS_getGpioMonitorOut Section .................. 209

Deleted Figure 112; Renumbered Sequentially ................................ 224

Changes to MYKONOS_getGpio3v3PinLevel Section ........... 224

Changes to Table 163 ................................................................... 226

Added Auxiliary DAC Control Software Control Procedure

Sec tion ............................................................................................ 227

Added Auxiliary (AUX) ADC Readback Software Control

Procedure Section ......................................................................... 230

Changes to Example 1: SEDZ to PEDZ Conversion Section ........ 236

Changes to Example 2: PEDZ to SEDZ Conversion Section ........ 237

Changes to Impedance Matching Network Section ........................ 249

Changes to Figure 151 ........................................................................... 252

Changes to Table 170 to Table 172 ...................................................... 253

Changes to Table 173 to Table 176 ...................................................... 254

Added Mykonos Tx1 and Tx2 Port Impedance Section .......... 255

Changes to Figure 159 Caption .................................................. 262

Changes to Figure 161 Caption .................................................. 263

Changes to Line Design Examples Section ............................... 264

Changed Transmitter Bias and Port Interface Section to

Transmitter Bias Design Considerations Section ..................... 268

Changes to Isolation Techniques Used on the ADRV9371-N/PCBZ

Evaluation Board Section ............................................................ 273

Changed AD9371 Demonstration System Overview Section to

Demonstration System Overview Section ................................ 281

Changes to Hardware Setup Section .......................................... 281

Changed AD9371 Transceiver Evaluation Software (TES)

Section to Transceiver Evaluation Software (TES) Section and

AD9371 Starting the Transceiver Evaluation Software Section to

Starting the Transceiver Evaluation Software Section ............. 287

Changes to Installation Section and Figure 183 Caption ........ 287

Changes to Figure 184 ................................................................. 288

Changes to GPIO Configuration Tab Section .......................... 293

Changes to Figure 207 ........................................................................... 301

Changes to File Dropdown Menu Section, Figure 209 Caption,

Figure 210 Caption, ..................................................................... 302

Changes to Tools Dropdown Menu Section, Figure 212

Caption, Figure 213 Caption, and Table 188 ............................ 303

AD9371/AD9375 System Development User Guide UG-992

Rev. B | Page 5 of 360

Changes to Help Dropdown Menu, Figure 214 Caption, System,

System Status Bar Section, Figure 215 Caption, and Figure 217

Caption ...........................................................................................304

Changes to Rx Signal Chain Section ...........................................306

Added DPD, CLGC, and VSWR Measurement (AD9375 Only)

Section, DPD Overview Section, and Figure 229 .....................319

Added Figure 230 ..........................................................................320

Added Figure 231 to Figure 233 ..................................................321

Added Figure 234 and Equation 57; Renumbered Sequentially ... 322

Added CLGC Overview Section, Voltage Standing Wave Ratio

Measurement Overview Section, Equation 58, and Figure 235 ... 323

Added DPD GUI Section amd Figure 236 .................................324

Added Figure 237, Waveform Setup Section, and Figure 238 ....... 325

Added DPD Setup Section, Figure 239, and Figure 240 ..........327

Added Figure 241 ..........................................................................328

Added PA Calibration Configuration Section and Figure 242 ..... 329

Added Error Messages and Debug Information Section and

Figure 243 .......................................................................................331

Added DPD API Section, ARM Setup Commands Section, and

Table 190 .........................................................................................332

Added Table 191 ............................................................................333

Added DPD API Data Structures Section, Figure 244, and

Table 192 .........................................................................................334

Added Figure 245 ..........................................................................335

Added Table 193 ............................................................................336

Added Figure 246 and Table 194 .................................................338

Added DPD Functionality API Functions Section ...................339

Added CLGC Tracking Calibration Section, CLGC

Configurations Section, Figure 247, and Figure 248 ................341

Added CLGC API Section, CLGC API Data Structures Section,

Figure 249, and Table 195 .............................................................342

Added Figure 250 and Table 196 .................................................344

CLGC Functionality API Functions ...........................................345

Added VSWR Tracking Calibration Section, VSWR Monitoring

Section, and Figure 251 ................................................................346

Added VSWR API Section, VSWR API Data Structures Section,

Figure 252, and Table 197 .............................................................347

Added Figure 243 and Table 198 .................................................349

Added VSWR Functionality API Functions Section ................350

Added Systems Design Considerations Section, DPD Tuning

Procedure Section, and DPD Model Save/Restore Functionality

Section ............................................................................................351

Added Guidelines for Developing and Troubleshooting a DPD

System Section ...............................................................................352

Added Designing a System for a TDD Application Section and

Table 199 .........................................................................................353

Added External Loopback Flatness Requirements and

Figure 254 .......................................................................................354

Added Figure 255 ..........................................................................355

Added CLGC Convergence Time Section, Figure 256, DPD

Limitations Section, and Other Considerations Section .........356

Added Typical Test Setup and DPD Performance Section and

Figure 257 .......................................................................................357

Added Figure 258 ..........................................................................358

Added TDD Setup Instructions Section and Figure 259 .........359

Added Figure 260 .......................................................................... 260

1/2017—Rev. 0 to Rev. A

Changes to Introduction Section .................................................... 1

Deleted /src/example Section .......................................................... 7

Changes to Figure 3 .......................................................................... 8

Changes to Developing the Application Section ........................ 10

Changes to API Sequence Section ................................................ 11

Changes to Figure 4 and Figure 5 ................................................. 15

Change to t

CO

Parameter, Table 4 and Figure 6 ........................... 16

Changes to Table 38 ........................................................................ 38

Added Hardware Considerations for Sync Signals Section ....... 53

Changes to Data Structure Member Initialization Section ....... 56

Deleted Folder Location Section and Figure 28;

Renumbered Sequentially .............................................................. 58

Changes to headless.c Section ....................................................... 58

Added Reference Clock and SYSREF Connections Section,

Connections for External Clock (DEV_CLK_IN) Section,

Figure 47, DEV_CLK Phase Noise Requirements Section,

Table 92, and Table 93; Renumbered Sequentially ................... 104

Added SYSREF Requirements Section and Figure 48 .............. 105

Added Minimum Delay Requirements Between SYSREF Pulses

Section, Timing of SYSREF Compared to DEV_CLK Section,

Figure 50, and Figure 51 ............................................................... 106

Added Connections for External LO Section, Figure 52, and

Table 94 ........................................................................................... 107

Added Performance Limitations Section and Figure 53 .......... 109

Changes to Example 1 Section, Example 2 Section, and

Example 3 Section ......................................................................... 118

Deleted DEV_CLK, SYSREF, and External LO Section,

Overview Section, Connections for the External Clock

(DEV_CLK_IN) Section, Figure 51, and Figure 52; ................. 120

Deleted DEV_CLK Phase Noise Requirements Section,

Figure 53, Table 94, and Table 95; Renumbered Sequentially ....... 121

Deleted Figure 54 and Figure 55 ................................................. 122

Deleted Multichip Synchronization (JESD204B Mode) Section

and Figure 56 ................................................................................. 123

Deleted Connections for External LO Section, Figure 57, and

Table 96 ........................................................................................... 124

Changes to Analog Peak Detector (APD) Basics Section ........ 127

Changes to Half-Band 2 (HB2) Overload Detector

Basics Section ................................................................................ 129

Added TDD Configuration and Setup Section, TDD in the

Mykonos Evaluation System Section, ARM Input and Output

Signals Section, and ARM Pin Mode Configurations Section ...... 168

Added Figure 88 ............................................................................ 169

Added ARM Acknowledge Signals Section, Table 133, and

Figure 89 ......................................................................................... 170

Added Table 134 and Table 135 ................................................... 171

Added Figure 90 and Table 136 ................................................... 172

Added FPGA Output Signals Section, Data Path Trigger

Modes Section, and Table 137 ..................................................... 173

Added Table 138 ............................................................................ 174

Added TDD Finite State Machine Class Section, Quick Help for

Programming FPGA/Mykonos Section, and Table 139........... 175