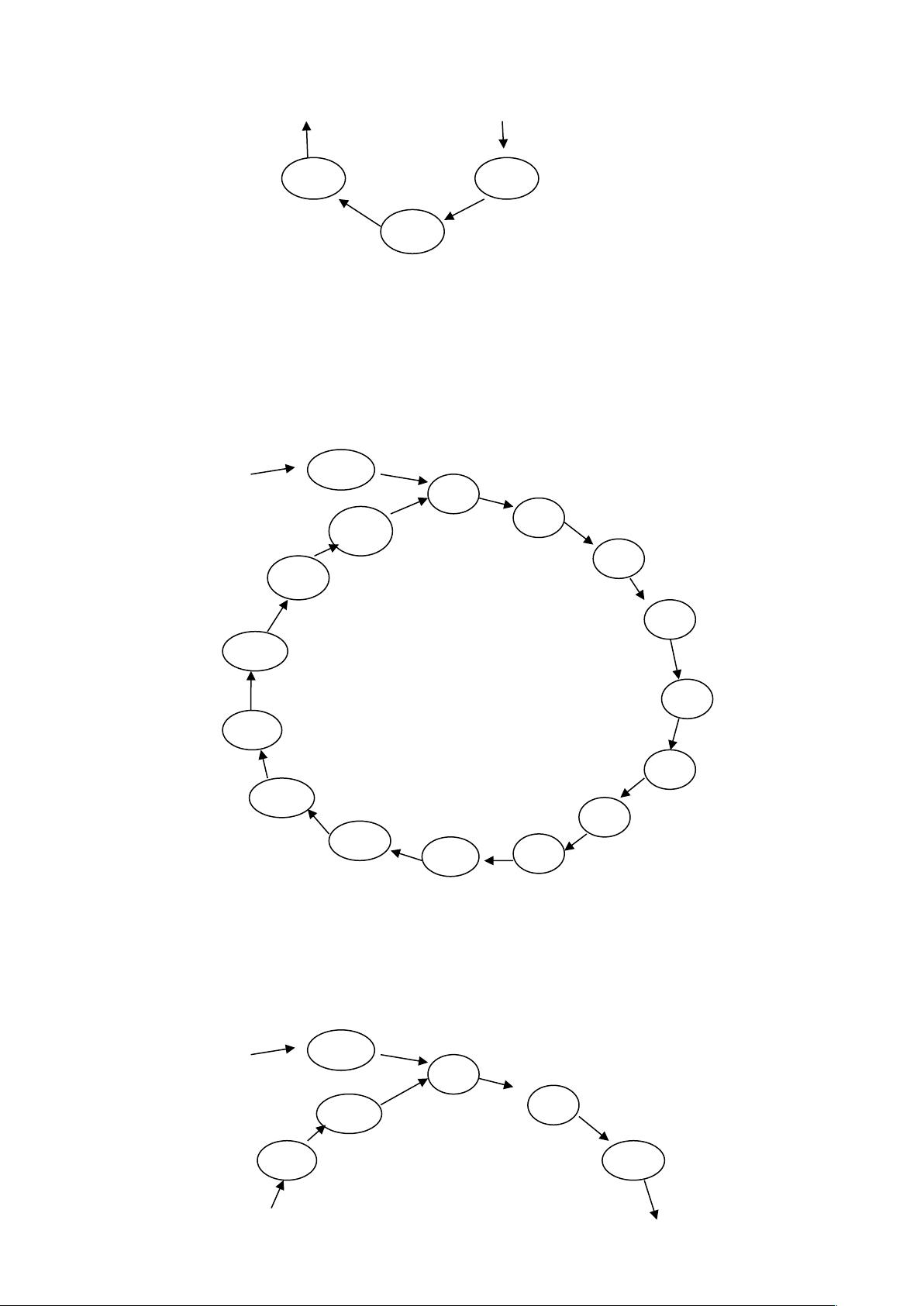

### VHDL 八路彩灯控制器相关知识点 #### 1. 引言及背景 在当前社会中,为了吸引顾客的注意力,商家采用各种手段进行装饰宣传,其中彩灯装饰是一种非常常见且有效的方式。彩灯不仅可以增添环境的美观度,还能提升场所的氛围,使城市夜景更加璀璨夺目。随着技术的发展,使用可编程逻辑器件(Programmable Logic Devices, PLDs)来进行彩灯控制变得越来越普遍。 VHDL(Very High Speed Integrated Circuit Hardware Description Language)作为一种标准的硬件描述语言,具有强大的描述能力、广泛的覆盖范围以及较高的抽象级别,在电子设计自动化(Electronic Design Automation, EDA)领域得到了广泛应用。通过EDA工具,设计师能够实现整个系统的自动化设计,从而将更多的精力集中在创新方案与概念构思上,显著提高设计效率并缩短产品开发周期。 #### 2. 八路彩灯控制器概述 本设计采用VHDL语言实现了一个基于FPGA的八路彩灯控制器。该控制器支持三种不同的彩灯模式,每种模式都有独特的亮灯顺序。具体而言,控制器通过状态机来实现不同彩灯模式之间的切换。 - **花样一**:从两边向中间亮,然后再从中间向两边亮。 - **花样二**:依次点亮所有灯,最后再从最右边逐渐熄灭。 - **花样三**:单个灯从左到右逐个点亮,然后再反向点亮。 #### 3. 总体设计方案 根据题目描述,八路彩灯控制器采用状态机的方式来控制彩灯的变化。对于每种彩灯模式,状态机的状态转移图如下所示: - **花样一**: - S0: "ZZZZZZZZ" - S1: "10000001" - S2: "01000010" - S3: "00100100" - S4: "00011000" - S5: "00100100" - S6: "01000010" - CLR - **花样二**: - S0: "ZZZZZZZZ" - S1: "00000000" - S2: "10000000" - S3: "11000000" - S4: "11100000" - S5: "11110000" - S6: "11111000" - S7: "11111100" - S8: "11111110" - S9: "11111111" - S10: "01111111" - S11: "00111111" - S12: "00011111" - S13: "00001111" - S14: "00000111" - S15: "00000011" - S16: "00000001" - CLR - **花样三**: - S0: "ZZZZZZZZ" - S1: "10000000" - S2: "01000000" - S3: "00100000" - S4: "00010000" - S5: "00001000" - S6: "00000100" - S7: "00000010" - S8: "00000001" - S9: "00000010" - S10: "00000100" - S11: "00001000" - S12: "00010000" - S13: "00100000" - S14: "01000000" - CLR #### 4. 模块设计详解 - **分频器模块**:由于原始时钟频率可能过高,不适用于彩灯控制器的正常工作,因此需要设计一个分频器模块。该模块的作用是将原始时钟信号进行分频,输出符合需求的新时钟信号。VHDL代码示例如下: ```vhdl ENTITY fenpinqi IS PORT ( CLK : IN STD_LOGIC; -- 原始机器时钟 CLR : IN STD_LOGIC; CLK1 : OUT STD_LOGIC -- 分频后的时钟 ); END fenpinqi; ARCHITECTURE ART OF fenpinqi IS SIGNAL CK : STD_LOGIC; BEGIN PROCESS (CLK, CLR) IS VARIABLE TEMP : STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN IF CLR = '1' THEN CK <= '0'; TEMP := "000"; ELSIF (CLK'EVENT AND CLK = '1') THEN IF TEMP = "111" THEN TEMP := "000"; CK <= NOT CK; ELSE TEMP := TEMP + '1'; END IF; END IF; END PROCESS; CLK1 <= CK; END ART; ``` - **花样一模块**:该模块利用分频器产生的时钟信号来控制彩灯的显示。其功能是从两边向中间亮,再从中间向两边亮。VHDL代码示例如下: ```vhdl ENTITY hy1 IS PORT ( CLK1 : IN STD_LOGIC; CLR : IN STD_LOGIC; XUAN : IN STD_LOGIC_VECTOR(1 DOWNTO 0); LED1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END ENTITY hy1; ARCHITECTURE ART OF hy1 IS TYPE STATE IS (S0, S1, S2, S3, S4, S5, S6); -- 设计状态机, 实现花样转换 SIGNAL CURRENT_STATE : STATE; SIGNAL LIGHT : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN PROCESS (CLR, CLK1, XUAN) IS CONSTANT L1 : STD_LOGIC_VECTOR(7 DOWNTO 0) := "10000001"; CONSTANT L2 : STD_LOGIC_VECTOR(7 DOWNTO 0) := "01000010"; CONSTANT L3 : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00100100"; -- 定义其他状态对应的常量 BEGIN -- 状态转移逻辑 CASE CURRENT_STATE IS WHEN S0 => CURRENT_STATE <= S1; LIGHT <= L1; WHEN S1 => CURRENT_STATE <= S2; LIGHT <= L2; WHEN S2 => CURRENT_STATE <= S3; LIGHT <= L3; -- 其他状态转移逻辑 WHEN S6 => CURRENT_STATE <= S0; LIGHT <= "ZZZZZZZZ"; -- 重置状态 WHEN OTHERS => CURRENT_STATE <= S0; LIGHT <= "ZZZZZZZZ"; END CASE; END PROCESS; LED1 <= LIGHT; END ART; ``` 以上是基于VHDL的八路彩灯控制器设计的关键点和实现细节。通过这种方式,不仅可以实现彩灯的动态变化,还可以灵活地扩展更多的彩灯模式,为实际应用场景提供更多的可能性。

剩余11页未读,继续阅读

鼠标CS2013-12-21最好说明一下在quartus里面怎么运行,或者直接给个工程文件。

鼠标CS2013-12-21最好说明一下在quartus里面怎么运行,或者直接给个工程文件。

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 下载视频工具,c++开发

- PHP的ThinkPHP5多小区物业管理系统源码(支持多小区)数据库 MySQL源码类型 WebForm

- 【安卓毕业设计】Android作业源码(完整前后端+mysql+说明文档).zip

- 【安卓毕业设计】基于Android租房软件app源码(完整前后端+mysql+说明文档).zip

- Untitled7.ipynb

- C#ASP.NET酒店管理系统源码 宾馆管理系统源码数据库 SQL2008源码类型 WebForm

- 【安卓毕业设计】基于安卓的奶牛管理源码(完整前后端+mysql+说明文档).zip

- 【安卓毕业设计】Android app作业源码(完整前后端+mysql+说明文档).zip

- Scrapy基础(讲解详细、包括框架流程代码实战,最佳学习资料).zip

- FPGA实现IIC通信quartus工程,纯verliog,可进行移植

信息提交成功

信息提交成功