5

5

4

4

3

3

2

2

1

1

E E

D D

C C

B B

A A

Title:

Rev:

Modified:

Sheet: of

Document:

Broadcom Corporation : Proprietary and Confidential

Size:

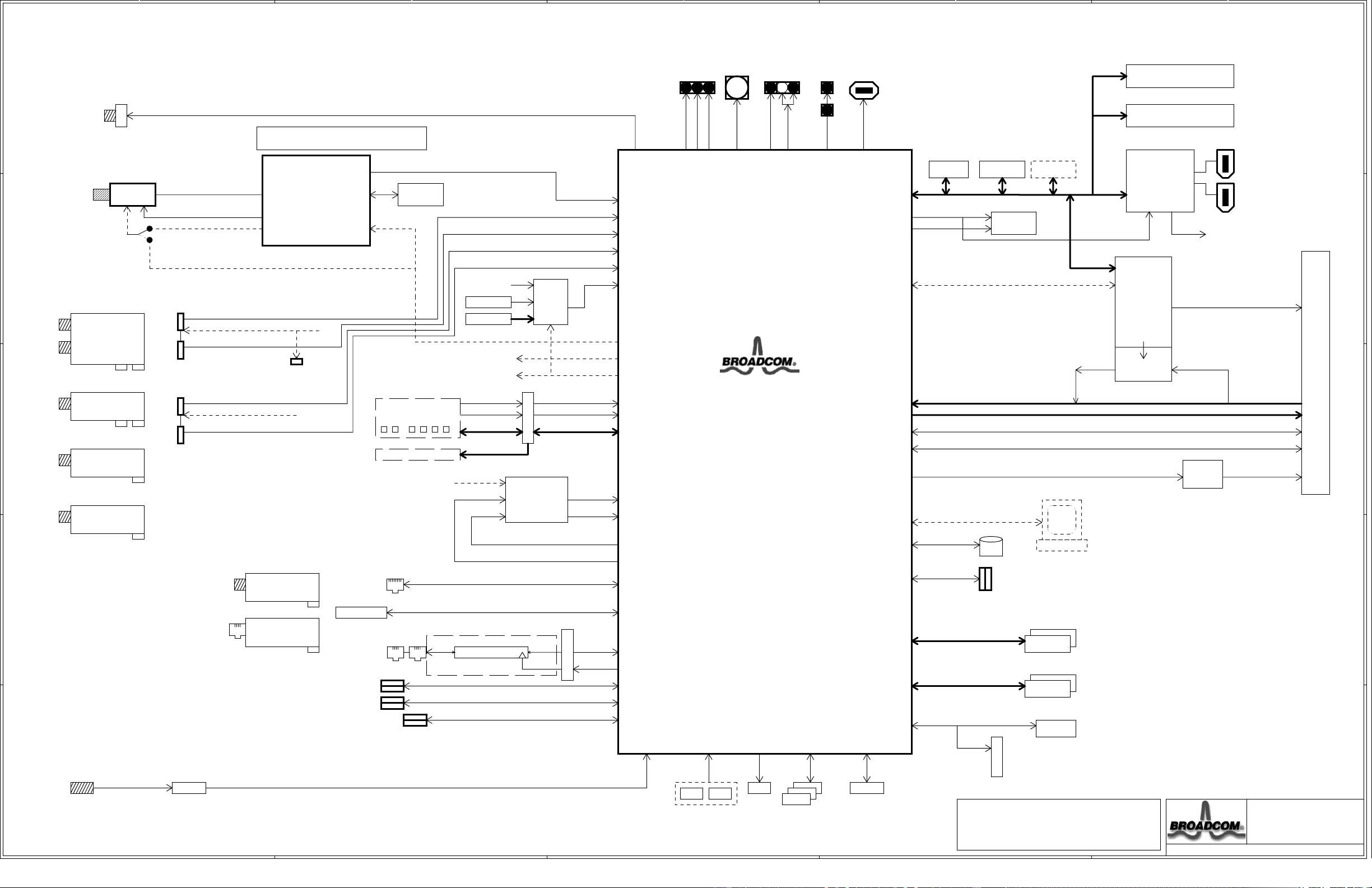

Revision History / Index

237

Thursday, June 19, 2008

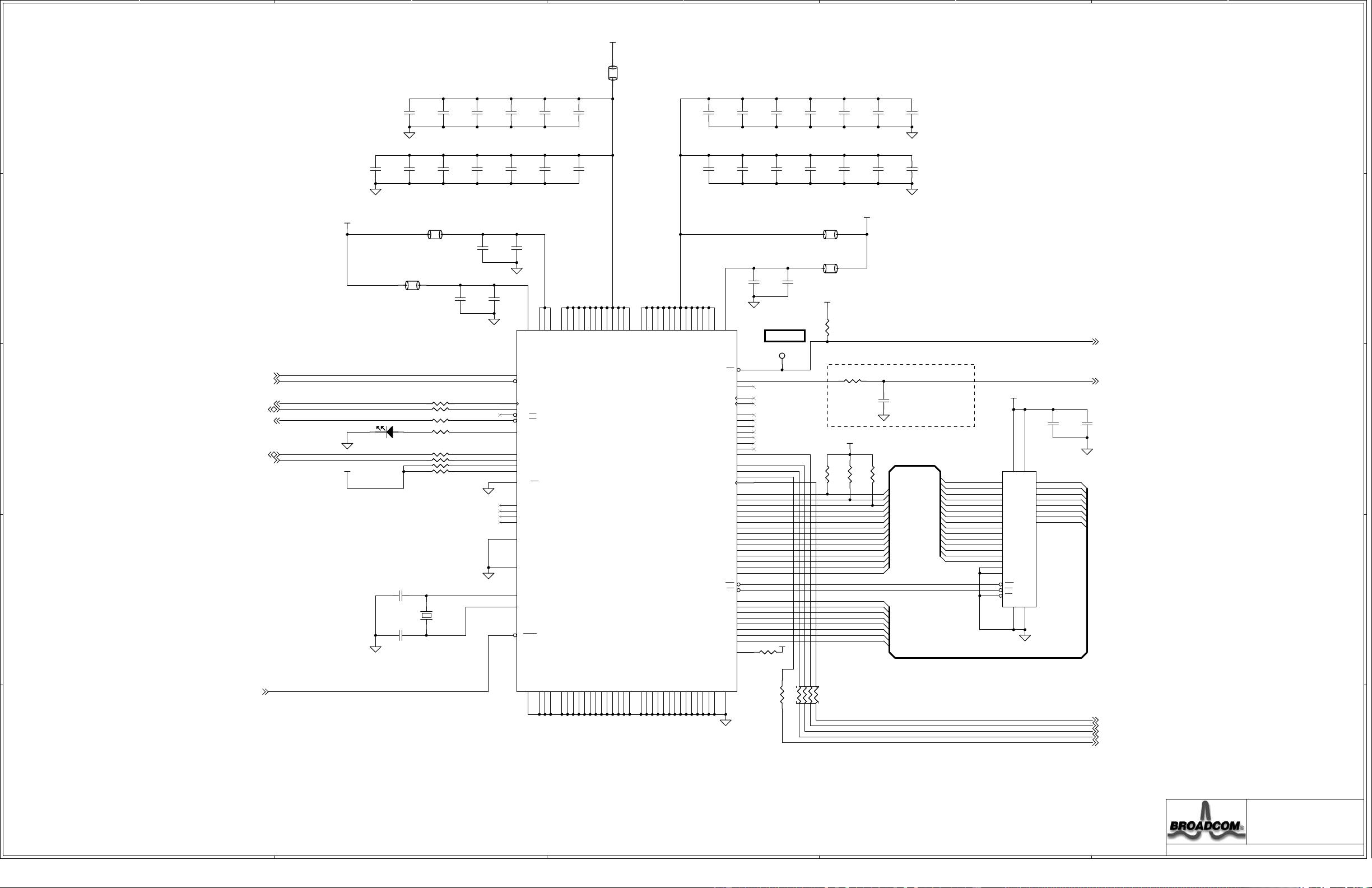

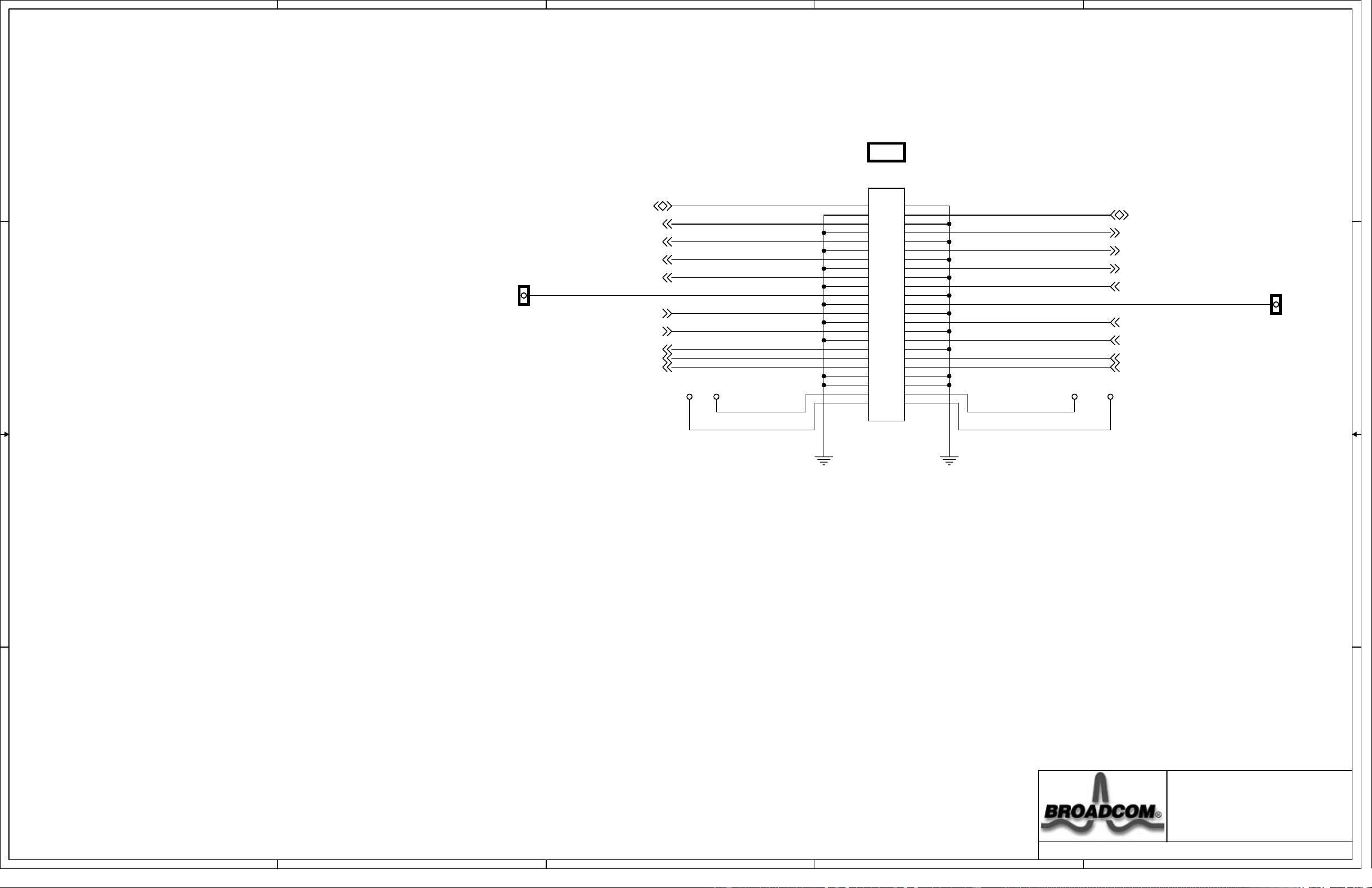

BCM97405MBv00 Schematic

Title:

Rev:

Modified:

Sheet: of

Document:

Broadcom Corporation : Proprietary and Confidential

Size:

Revision History / Index

237

Thursday, June 19, 2008

BCM97405MBv00 Schematic

Title:

Rev:

Modified:

Sheet: of

Document:

Broadcom Corporation : Proprietary and Confidential

Size:

Revision History / Index

237

Thursday, June 19, 2008

BCM97405MBv00 Schematic

ECOs:

Errata:

Page Index

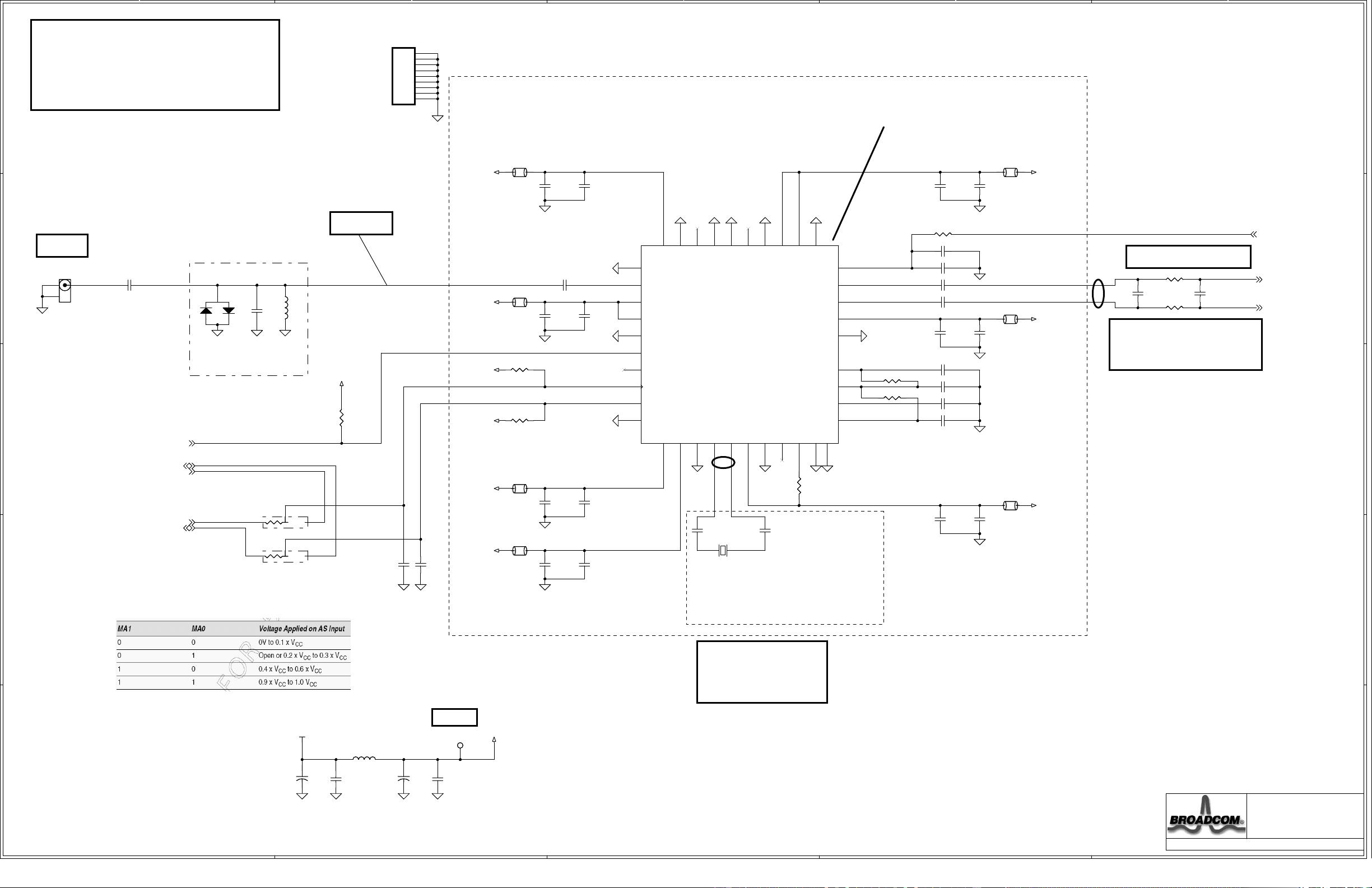

ECO BCG-02008: V00 Rev. P1:

- Initial Release

ECO BCG-02042: V00 Rev. P2 changes:

- Pg 28 Changed J1307 to RoHS part.

ECO BCG-02086: V00 Rev. P3 changes:

- Pg 13 Moved RD1306, RD1328 to Position A.

( Selects correct DRAM size for MEMC0/1 )

- Pg 22 Moved RD2201 to Positon B

(Enables EJTAG.)

- Pg 19 Stuff RN1904, RN1905 with 0 ohms (528499-00)

( Connect SLOT1 and Transport FPGA to PKT4 and PKT5.)

- Pg 30 Remove RN3001

( Disconnect PKT5 from I2S output of VDEC-VEC daughter card.)

- Pg 26 Change C2609 to 100pf (500569-00)

Change R2617 to 4K 1% (502672-00)

( Correct USB RRef.)

ECO BCG-02143: V00 Rev. P5:

-Pg 11 Swap SDA and SCL for BSC_M0,2,3 busses

-Pg 13 Replace resistor straps RD1303, RD1304, RD1324 with 3-pin jumpers

for DDR_Configuration.

-Pg 30 Remove RN3014 and stuff RN3012, RN3013

with 0 ohm rpacks 528499-00.

(Enables PKT_VALID[5:0], PKT_ERROR[5:4],

disables 656 out of J3001:

ECO BCG-02114: V00 Rev. P4:

-Agile documentation correction. No impact on schematic.

ECO BCG-02213: V00 Rev. P6:

- New PCB spin. Includes all previous revisions plus:

-Pg 08 Add 20 DDR test pads. Place them close to 7405.

Move old TP's over by DDR chips.

-Pg 09 Replace Micron DDR2-667 RAM with Samsung DDR2-800

-Pg 11 Swap SDA and SCL for BSC_M1 bus

-Pg 13 Replace resistor straps RD1308, RD1310, RD1322 with 3-pin jumpers

for Flash/ROM Size1, Flash Type, USB Mode

Change strapping for CPU frequency to 405 MHz

-Pg 32 Add D5.0V to J216-1 heatsink fan connector.

Move TP218, TP225 out of POD path. Distribute GND TP's better.

-Pg 37 DNI backup power regulators

ECO BCG-02417: V00 Rev. P8:

-Pg 03 Change C526, C527 from 1000pf to 27pf. (Fixes slow rise time on BSC_M0.)

-Pg 08 Change R804 to 150 ohms (Fixes RCOMP)

-Pg 21 Replace U2105 with 8Gb NAND Flash

-Pg 22 Change various R and C values in 3OT Crystal circuit.

-Pg 26 Change R2609 from 1k to 1.24k.

Remove R2605, R2606, R2607, R2608 (E-net PHY already terminated on die)

-Pg 32 Short pins 9, 12 together on U202. (Connects AVIN to PVIN on ER5336QI.)

-Pg 32-33 Corrected Red TP's from 531213-00 to 521741-00.

-Pg 20, 21, 25, 29 Changed 0.1uf caps to 520193-00 to be same as those on Pg 4.

The following changes were made to the schematic:

-Pg 10, 11, etc. Multi-function pin names on Bcm7405 symbol corrected.

-Pg 13 Corrected strapping table:

"strap_ebi_rom_size" settings for NAND ECC inverted

"strap_ebi_boot_memory" added info for NAND WR-protect.

-Pg 32, 33 Amperage and Power numbers corrected.

Updated / corrected notes on several pages.

-Pg 05 Add MICTOR connector to MII lines for logic analyzer.

-Pg 15 Consider using MAX9722 for audio opamps. (for pop suppression)

-Pg 19 Add RMX_PAUSE0/1 to Remux connectors. Stuff DNI'd resistors to enable these paths.

-Pge 21 Add skt footprint for testing various NAND Flash (see Emulation Technology)

-Pg 26 eSATA & E-net ports need ESD protection.

Add 25-30MHz SATA xtal footprint.

Change SATA connectors to SMT.

-Pg 32 Split 1.8v power so DDR and 7405 can be measured separately.

Add GND puddle on Layer 5 under DDR address and data traces on Layer 6.

Replace Enpirion regulator with another brand.

ECO CORP-06712: V00 Rev. P7:

-BRCM p/n 502858-00 CAP,CER,0603,0.1uF,20%,16V,X7R) will be made

obsolete as it is a duplicate of the BRCM p/n 520192-00. This ECO will update all

BOM that currently used 502858-00 and update with 520192-00.

ECO BCG-03062: V00 Rev. P9:

-Pg 04 Change Y601 to 28 MHz (for high-symbol-rate QAM)

-Pg 10 GND RN1025-1,2,3,4 to prevent POD VPP enables from floating.

Remove RN1026, RN1027 to disconnect UART stubs on MII lines.

Add 0 ohm to R1016 to connect MII_TX_ERR.

-Pg 10,30 Remove R1022, add jumper to move 3510 IRQ from GPIO_015 to GPIO_024.

-Pg 17 Remove C1708, the 56pf cap on HDMI CEC line.

-Pg 21 Remove R2169 to disable Block Lock on NAND flash.

-Pg 23,24,29 Remove R2301, R2302, R2909 and jumper UART0 Rx/Tx to GPIO_111/112.

Jumper POD_VCC_ON to GPIO_110.

The following changes were made to the schematic:

-Pg 16 Change 30 MHz filter name to "elliptical".

-Pg 22 Change EJTAG note.

-Pg 24 Add NDS note.

Other minor note changes.

ECO BCG-03757: V00 Rev. P10:

-Pg 08 Change PCOMP, NCOMP terminations (R805, R806) to 24.3 ohms

-Pg 09 Change DDR_CLK terminations to Thevenin (PU/PD)

Change all VTT terminations to 62 ohms.

The following changes were made to the schematic:

-Pg 08 Revise DDR2 layout rules.

-Pg 26 Add note to use 25-30MHz backup SATA crystal

Add note to leave E-Net termination pads on board

Add note to add 1k differential terminations to SATA lines.

-Pg 34 Add note that C114 not needed now that RFM_PLLCAP is just a test port.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功

- 1

- 2

前往页