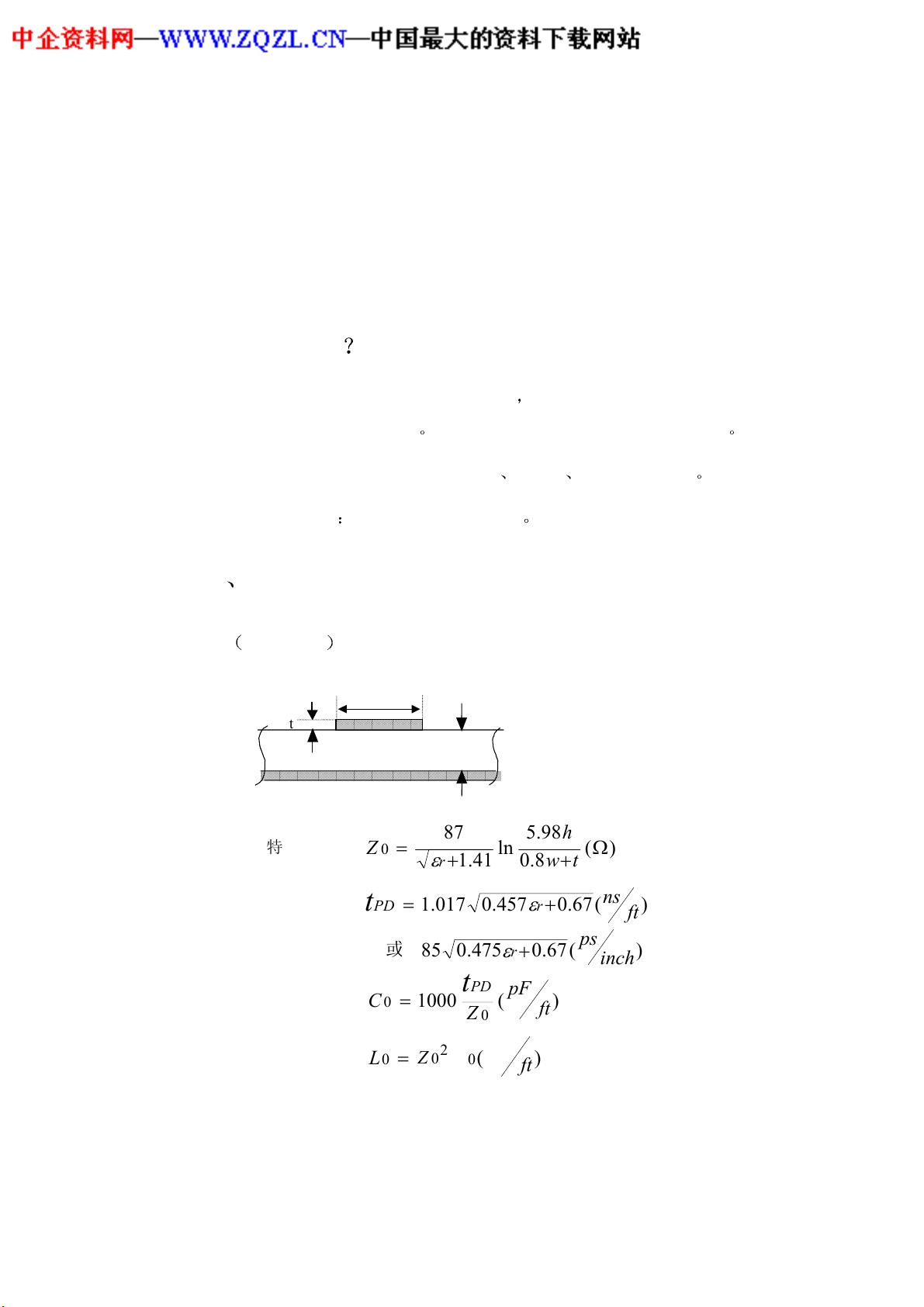

### 高速数字电路设计及EMC设计 #### 一、高速数字电路设计 ##### 1.1 何谓高速数字信号 高速数字信号是指在传输过程中能够支持较高数据传输速率的信号。这类信号通常涉及的数据传输速率较高,例如超过100 Mbps,甚至高达几个Gbps或更高。随着信息技术的发展,高速信号的应用越来越广泛,例如在高速计算机网络、高性能服务器、移动通信系统等领域。 ##### 1.2 微带线与带状线的概念 - **1.2.1 微带线(Microstrip)** - 微带线是一种常见的传输线形式,由一个导体带和位于其下方的接地平面组成,两者之间通过介质材料隔开。 - 微带线的特点是结构简单、易于加工,适用于高频信号的传输。 - 微带线的设计需考虑其特性阻抗(通常为50Ω),以确保信号传输过程中减少反射。 - **1.2.2 带状线(Stripline)** - 带状线是一种介于两个接地平面之间的信号导体,两侧及底部均被接地平面包围。 - 相较于微带线,带状线具有更好的屏蔽性能,可以有效减少电磁干扰。 - 带状线的设计同样需关注其特性阻抗,一般为50Ω或75Ω。 - **1.2.3 经验数据** - 微带线和带状线的设计涉及到具体的物理尺寸、介质材料的选择等因素。 - 工程实践中,可以通过查阅相关的手册或软件工具来获取具体的参数值。 - **1.2.4 同轴线(Coaxial Cable)** - 同轴线由内导体、绝缘层、外导体和保护层四部分组成,适用于长距离的信号传输。 - 其特点是具有良好的屏蔽效果和较低的损耗,适用于高频信号的传输。 - **1.2.5 双绞线(Twisted-Pair Cable)** - 双绞线是由两根互相缠绕的导线组成,通过相互缠绕可以减少电磁干扰。 - 双绞线分为屏蔽双绞线(STP)和非屏蔽双绞线(UTP),前者具有更好的屏蔽效果。 - **1.2.6 等间隔的电容负载的影响** - 在高速电路设计中,等间隔的电容负载会对信号的完整性产生影响。 - 电容负载会导致信号的衰减和时延增加,从而影响数据的传输质量。 ##### 1.3 常见高速电路 - **1.3.1 ECL (Emitter-Coupled Logic) 电路** - ECL是一种基于发射极耦合的逻辑门电路,常用于高速数字电路中。 - 其特点是速度快、功耗相对较大,适合于高速信号处理。 - **1.3.2 CML (Current-Mode Logic) 电路** - CML是一种采用电流模式的逻辑门电路,相比于电压模式的电路具有更高的信号带宽。 - CML电路主要用于高速接口设计中。 - **1.3.3 GTL (Gunning Transceiver Logic) 电路** - GTL电路是一种用于高速数据传输的标准,主要用于长距离的数据通信。 - GTL具有较好的噪声抑制能力,适用于高速数据传输。 - **1.3.4 BTL (Backplane Transceiver Logic) 电路** - BTL电路是一种专为背板通信设计的逻辑标准,具有较好的信号完整性。 - BTL适用于高速背板通信系统。 - **1.3.5 TTL (Transistor-Transistor Logic) 电路** - TTL是一种基于双极型晶体管的逻辑门电路,是早期数字电路中的常用类型。 - 虽然TTL的传输速度相对较慢,但在某些低速应用中仍然被广泛使用。 - **1.3.6 模数转换电路** - 模数转换电路(ADC)将模拟信号转换为数字信号,是高速数据采集系统的关键组成部分。 - ADC的设计需考虑采样速率、分辨率等因素,以满足不同应用场景的需求。 ##### 1.4 常见电路匹配措施 - **1.4.1 反射** - 在高速电路设计中,信号反射是常见的问题之一。 - 为了减少反射,需要确保传输线的特性阻抗与负载阻抗相匹配。 - **1.4.2 终端匹配** - 终端匹配是在信号传输线的末端接入与特性阻抗相匹配的电阻,以减少信号反射。 - 适当的终端匹配可以提高信号的质量。 - **1.4.3 始端匹配** - 始端匹配是指在信号源端进行阻抗匹配。 - 这种方法适用于信号源内部阻抗已知的情况,有助于减少信号在传播过程中的失真。 #### 二、高速电路设计的一般原则和调试方法 - **1.5.1 同步逻辑设计** - 在高速数字电路设计中,同步逻辑设计是非常重要的。 - 同步逻辑设计可以确保电路中的各个部分按照预定的时间顺序执行操作。 - **1.5.2 了解选用器件的输入输出结构** - 选择合适的器件对于高速电路设计至关重要。 - 需要了解器件的具体输入输出结构,以便进行正确的匹配设计。 - **1.5.3 对极高速率(300MHz以上)的信号** - 对于极高频率的信号,建议采用互补逻辑设计,以降低对电源的要求。 - 这有助于提高电路的整体稳定性。 - **1.5.4 了解每一根高速信号电流的流向** - 了解信号电流的流向有助于优化电路设计,确保信号的正确传输。 - 电流流向的分析还可以帮助发现潜在的问题点。 - **1.5.5 信号的布线** - 高速信号的布线需遵循微带线或带状线的要求。 - 需要保证信号线路与地平面的良好配合,以减少信号失真。 - **1.5.6 电源滤波** - 电源滤波对于高速电路来说非常重要。 - 适当的滤波措施可以有效减少电源噪声对信号的影响。 - **1.5.7 对很高速度的信号要估算其走线延迟** - 估算信号的走线延迟有助于调整电路设计,以满足时序要求。 - 这对于保证信号的正确传输至关重要。 - **1.5.8 在满足速度要求的前提下,尽量选用工作速率低的器件** - 选择工作速率低的器件可以在不影响性能的情况下降低功耗。 - 这有助于提高整个系统的效率。 - **1.5.9 差分线尽量靠近走线** - 在高速电路设计中,差分线的紧密排列可以有效减少电磁干扰。 - 这对于提高信号的完整性非常关键。 - **1.5.10 测试方法** - 高速电路的测试通常需要使用高速示波器。 - 自制的探头可以帮助更准确地捕捉信号的变化。 - **1.5.11 Ringing, Crosstalk, Radiated Noise —— 数字系统的三种噪声** - Ringing指的是信号在到达目的地后出现的振荡现象。 - Crosstalk则是指不同信号线之间的干扰。 - Radiated Noise是指电路产生的电磁辐射。 - 减少这些噪声对于提高高速电路的可靠性至关重要。 - **1.5.12 数字信号的绝大部分能量(功率谱密度)集中在f_knee之内** - f_knee是指信号带宽内的转折频率点。 - 大多数信号的能量主要集中在该频率点以下,这对于信号完整性分析非常关键。 - **1.5.13 延时** - FR4 PCB的外层走线延时大约为140~180 ps/inch,内层走线约为180 ps/inch。 - 了解延时有助于精确控制信号传输的时间。 - **1.5.14 集总参数与分布参数系统** - 集总参数系统假设元件参数在整个电路中保持不变。 - 分布参数系统则认为参数随位置而变化。 - 高速电路设计中,需要根据实际情况选择合适的方法。 - **1.5.15 互感与耦合电容的作用** - 互感和耦合电容都是高速电路中常见的电磁现象。 - 了解这些效应对于优化电路设计非常关键。 - **1.5.16 ECL电路的上升时间和下降时间的计算** - 上升时间和下降时间是评价高速电路性能的重要指标。 - 计算这两个参数有助于评估电路的工作速度。 - **1.5.17 在数字系统中,耦合电容引起的串扰比起互感引起的串扰要小** - 耦合电容和互感都会导致信号之间的串扰。 - 在大多数情况下,耦合电容引起的串扰较小。 - **1.5.18 传输通道包括器件封装、PCB布局、连接器** - 传输通道的设计直接影响信号的完整性和稳定性。 - 需要在fknee范围内保持平坦的频响,以确保信号不失真。 - **1.5.19 阻容负载对电流变化的作用** - 阻容负载会影响信号的上升时间和下降时间。 - 正确处理阻容负载对于改善信号完整性非常重要。 - **1.5.20 噪声容限** - 噪声容限是指电路能够容忍的最大噪声水平。 - 了解噪声容限有助于设计更加健壮的高速电路。 - **1.5.21 地反弹(Ground Bounce)** - 地反弹是指由于多个信号同时切换导致的地线上电压波动。 - 地反弹可能引起信号失真,需要采取措施减轻其影响。 - **1.5.22 寄生电容的影响** - 寄生电容对高输入阻抗电路的影响尤其显著。 - 优化电路布局可以有效减少寄生电容的影响。 - **1.5.23 示波器探针的电气模型** - 示波器探针的电气模型对于理解高速信号测试结果非常重要。 - 探针的阻抗匹配和衰减比是关键参数。 - **1.5.24 21:1探针** - 21:1探针是一种常用的高速信号测试探针。 - 它可以将信号放大21倍,以适应高速示波器的输入范围。 - **1.5.25 趋肤效应** - 趋肤效应是指在高频下,电流倾向于集中在外层的现象。 - 这种效应会增加导线的损耗,并影响信号的质量。 - **1.5.26 对低频信号,电流流经电阻最小的路径;对高频信号,回流路径的电感远比其电阻重要** - 低频信号和高频信号在流经路径时的行为有所不同。 - 对于高频信号,减少回流路径的电感是关键。 - **1.5.27 负载电容对上升时间的影响** - 负载电容会影响信号的上升时间。 - 适当调整负载电容有助于优化信号的质量。 - **1.5.28 直流匹配和交流匹配的功耗比较** - 直流匹配和交流匹配的功耗存在差异。 - 在高速电路设计中,需要权衡功耗和信号完整性。 - **1.5.29 电源系统设计原则** - 电源系统的设计对于高速电路的稳定运行至关重要。 - 需要考虑电源的纹波、噪声等因素。 - **1.5.30 TTL和ECL的混合系统** - 在TTL和ECL的混合系统中,需要注意两种逻辑电路之间的兼容性。 - 采取适当的接口设计可以确保两种逻辑的正常工作。 - **1.5.31 电源线上的电磁辐射防护** - 电源线上的电磁辐射是高速电路设计中需要考虑的问题。 - 采取合适的防护措施可以有效减少电磁辐射的影响。 - **1.5.32 旁路电容的选取和安装** - 旁路电容的选择和安装对于减少电源噪声至关重要。 - 需要根据具体的应用场景选择合适的电容值。 - **1.5.33 连接器对高速系统的影响** - 连接器是高速电路中不可或缺的一部分。 - 选择合适的连接器可以减少信号损失,提高信号质量。 - **1.5.34 总线** - 总线是高速电路中用于连接各个模块的重要组成部分。 - 总线的设计需考虑信号的完整性和时序要求。 ### 三、电磁兼容性(Electromagnetic Compatibility, EMC) #### 2.1 关于电磁兼容性的基本原理 - **2.1.1 下面的电路布局有什么问题?** - 在高速电路设计中,不良的电路布局会导致电磁干扰问题。 - 例如,信号线和电源线之间的距离过近可能导致串扰。 - 避免这种布局问题有助于提高电路的EMC性能。 - **2.1.2 走线可穿过回流平面的缝隙吗?** - 不建议走线穿过回流平面的缝隙。 - 这种做法可能会增加电磁干扰的风险。 - **2.1.3 走线的电感和电容** - 走线的电感和电容会影响信号的完整性。 - 优化走线设计可以减少这些效应的影响。 - **2.1.4 接地的作用** - 接地对于高速电路设计来说非常重要。 - 正确的接地可以减少电磁干扰,并提高电路的稳定性。 - **2.1.5 信号参考点应在何处接至基底(chassis)** - 信号参考点的选择对于减少电磁干扰非常重要。 - 将信号参考点接到基底上可以有效降低干扰。 - **2.1.6 周期信号** - 周期信号在高速电路中非常常见。 - 对于周期信号的分析有助于减少电磁干扰。 - **2.1.7 EMC三要素** - EMC设计需要考虑三个要素:源(source)、路径(path)和接收器(receiver)。 - 通过减少源的辐射、优化路径设计以及增强接收器的抗干扰能力,可以提高整体的EMC性能。 - **2.1.8 共模和差模** - 共模信号和差模信号是高速电路设计中常见的两种信号类型。 - 共模信号是两个信号线相对于参考地的电压相同;差模信号是两个信号线之间的电压差。 - 优化电路设计可以减少共模和差模信号的影响。 - **2.1.9 减小噪声的措施** - 为了减少高速电路中的噪声,可以采取多种措施。 - 包括使用合适的滤波器、优化电源设计、改进接地等方法。 通过上述内容的详细介绍,我们可以看到高速数字电路设计及其EMC设计涉及众多复杂的概念和技术要点。这些知识点不仅涵盖了信号传输的基本原理,还深入探讨了各种实际应用中的技术挑战和解决方案。对于从事高速电路设计的工程师而言,理解和掌握这些知识是非常重要的。

剩余50页未读,继续阅读

- 粉丝: 3

- 资源: 11

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Java的tio-http-server演示学习源码

- 基于Java和C#的C#课程实验与Winform学习及Android实验设计源码

- 基于Java的电厂职工管理系统设计源码

- 基于Python的RSA+AES加密的SecureHTTP设计源码

- 基于Java平台的集成nsg-dao设计源码,涵盖jdbc、hibernate、mybatis框架

- 基于Vue的Java+JavaScript+CSS+HTML搭建的二手交易平台设计源码

- 基于Java和Vue的Spring Boot博客系统设计源码

- 基于MS51单片机的eeprom32与sst39vf040存储器读写设计源码

- 基于Python和Shell脚本的多环境配置运行命令管理器PyMake设计源码

- 基于Python和uiautomator2的支付宝积分活动自动化脚本设计源码

信息提交成功

信息提交成功