atmega64a资料

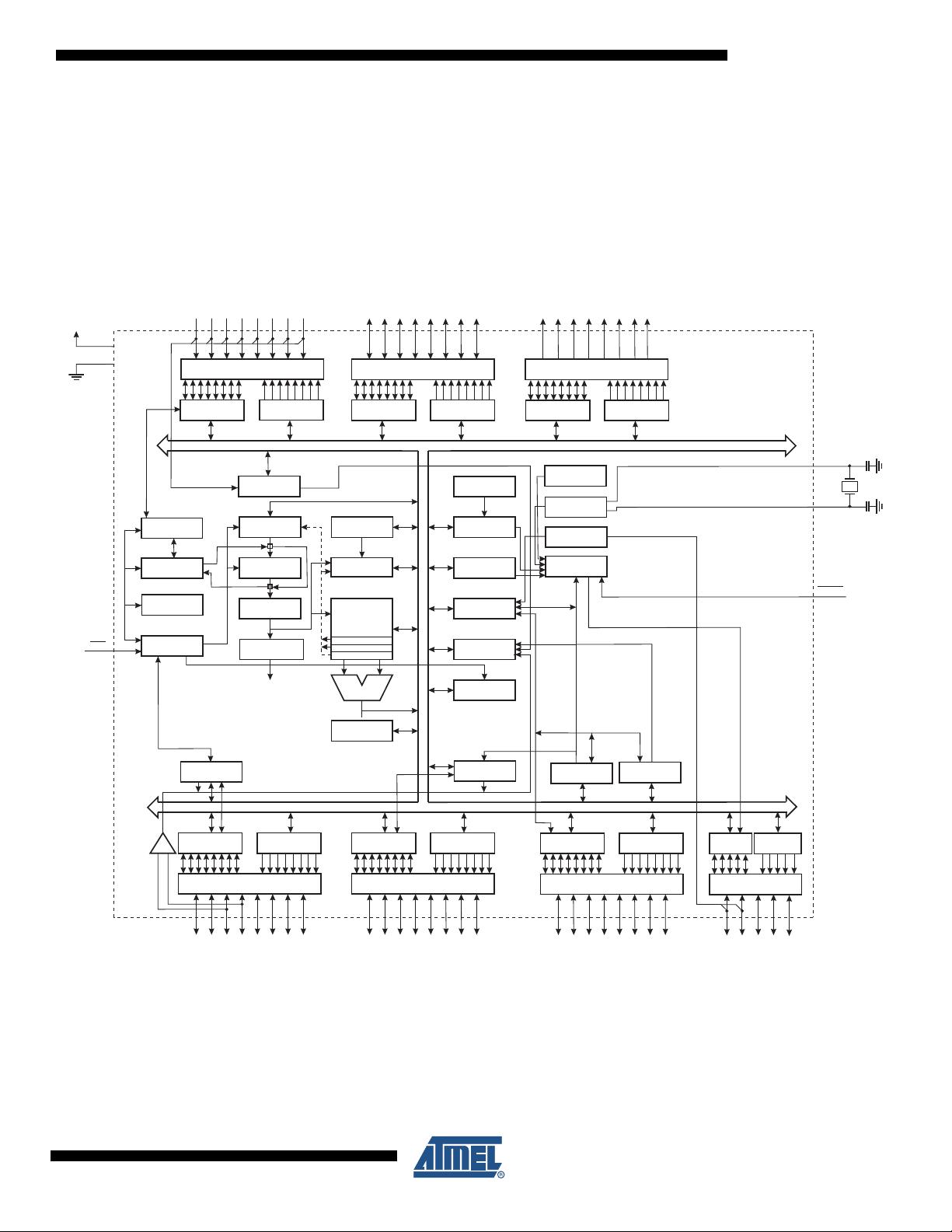

### ATmega64A单片机详尽解析 #### 高性能、低功耗的AVR®8位微控制器 ATmega64A是Atmel公司出品的一款高性能、低功耗的8位微控制器(MCU)。这款微控制器基于先进的精简指令集计算机(RISC)架构设计,能够实现高速数据处理,同时保持低能耗特性,非常适合于各种嵌入式应用领域。 #### 先进的RISC架构 ATmega64A拥有130条强大的指令集,大部分指令都能在一个时钟周期内执行完成,大大提升了处理速度和效率。其32个8位通用工作寄存器以及外加的外围控制寄存器,提供了丰富的数据操作能力。该微控制器支持全静态操作模式,可以在宽广的频率范围内运行,最高可达到每秒16百万条指令(MIPS)的吞吐量,在16MHz时钟频率下实现。 #### 高耐久性非易失性存储段 ATmega64A配备了大容量的在系统可重编程闪存程序存储器,高达64KB,以及2KB的EEPROM存储空间和4KB的内部SRAM,满足了数据存储和快速访问的需求。其写入/擦除循环次数分别达到了10,000次(闪存)和100,000次(EEPROM),保证了高耐久性。数据保留时间在85°C下为20年,在25°C下则可长达100年,确保了长期的数据可靠性。此外,还提供了一个可选的引导代码区域,具有独立的锁定位。 #### 在系统编程与安全功能 这款MCU支持在系统编程,即通过内置的引导程序进行更新,无需外部设备。它还支持真正的读写同时操作,可以接入高达64KB的外部存储空间,并提供了软件安全锁,防止未经授权的编程。SPI接口使得在系统编程成为可能,增强了灵活性和实用性。 #### JTAG标准接口 符合JTAG(IEEE标准1149.1)的接口,具备边界扫描能力,遵循JTAG标准,提供了全面的片上调试支持。不仅可以通过JTAG接口编程闪存、EEPROM、熔丝位和锁定位,还能进行故障检测和调试,大大提高了开发效率和产品可靠性。 #### 多样化的外设功能 ATmega64A配备了丰富的外设资源,包括两个8位定时器/计数器,每个都有独立的预分频器和比较模式;两个扩展的16位定时器/计数器,同样配备独立的预分频器、比较模式和捕获模式;一个具有独立振荡器的实时计数器;两个8位脉冲宽度调制(PWM)通道;以及6个具有可编程分辨率从1到16位的PWM通道。8通道、10位模数转换器(ADC)支持8路单端输入、7路差分输入和2路可编程增益(1倍、10倍、200倍)的差分输入,满足了复杂信号采集需求。此外,还提供了一个字节导向的两线串行接口,双可编程串行USART接口,以及主/从SPI串行接口,增强了与其他设备的通信能力。 #### 特殊的微控制器特性 ATmega64A还具备电源复位和可编程欠压检测功能,内置校准的RC振荡器,支持内外部中断源,六种睡眠模式:空闲、ADC噪声减少、省电、掉电、待机和扩展待机,软件可选的时钟频率,以及ATmega103兼容模式,由熔丝选择。全局上拉禁用功能,优化了电路设计。 #### I/O与封装 该MCU提供了53个可编程I/O引脚,采用64引脚TQFP或64焊盘QFN/MLF封装,便于PCB布局和信号完整性设计。 #### 工作电压与速度等级 ATmega64A的工作电压范围为2.7V至5.5V,适用于广泛的电源条件,而速度等级则支持0-16MHz,适应不同应用场景下的速度需求。 ATmega64A是一款高度集成、功能强大且易于使用的微控制器,特别适合于需要高性能、低功耗和高可靠性的嵌入式应用,如工业控制、汽车电子、消费电子产品等。

剩余391页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Python智能红绿灯控制系统的开发-实时交通流量检测与红绿灯状态优化切换实现方案含代码

- Java-Java资源

- jsBook-跨年倒计时html代码

- New-Year-Card-新年倒计时

- 跨年烟花大屏show-跨年

- fireworks-烟花代码

- vue-mapvgl-烟花代码

- CS-Books-Store-计算机网络课后题答案

- front-end-Doc-烟花代码大全html

- html新年快乐3d烟花代码HTML/CSS/JS实现新年快乐动态3D烟花特效及应用案例

- Front-end-tutorial-烟花代码大全html

- walle-web-烟花代码

- hardseed-python新年快乐代码

- JavaFamily-master-上学的小垃圾

- 基于HTML5的交互式新年倒计时与动态烟花展示

- 元旦烟花html,Web前端技术实现元旦烟花动画特效:HTML/CSS/JavaScript联合演示

信息提交成功

信息提交成功