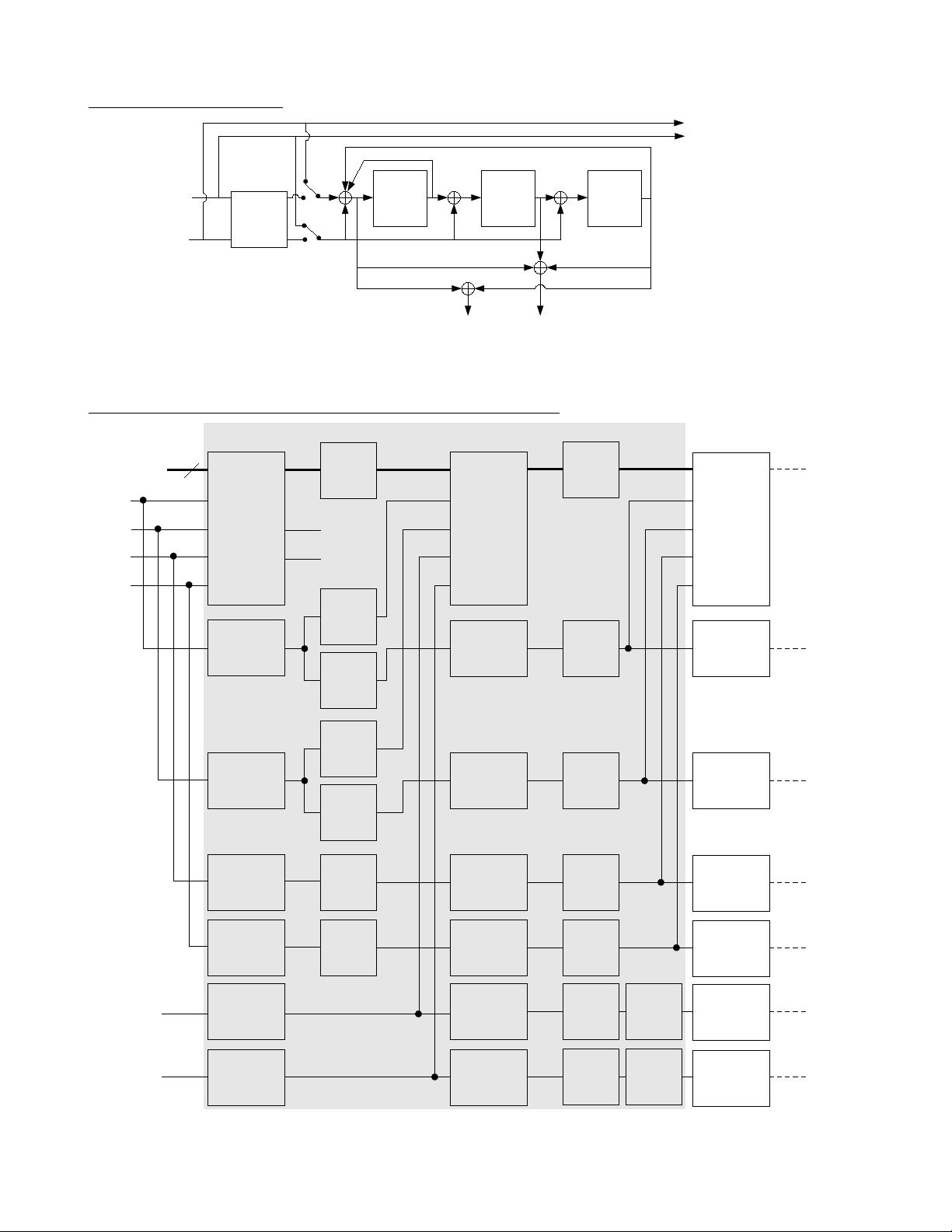

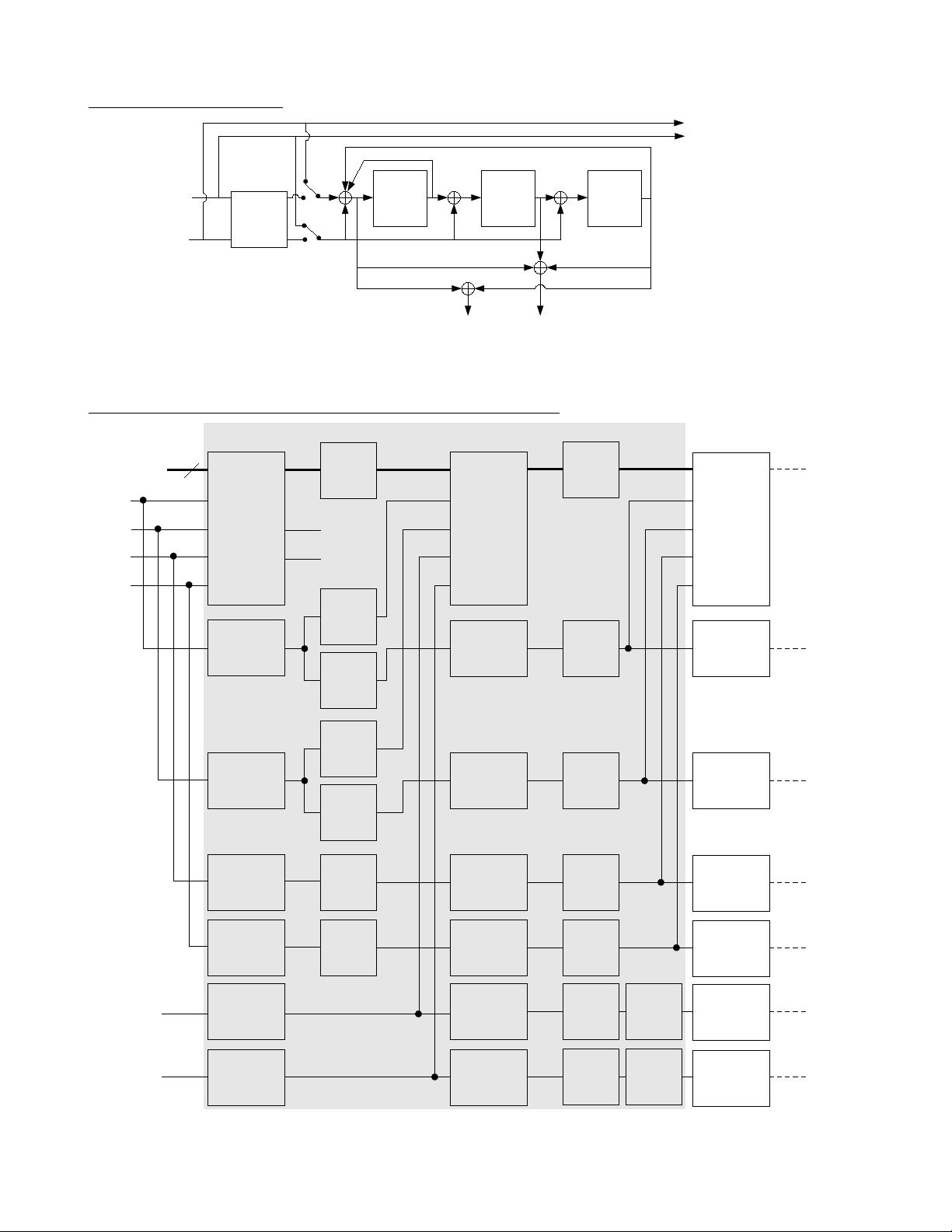

** Turbo码介绍 ** Turbo码是一种具有极强纠错能力的前向错误纠正(Forward Error Correction,FEC)编码技术,由Berrou等人在1993年提出,被誉为是继香农理论之后的第二次编码革命。Turbo码通过两个或多个交织器和并行的迭代软输入软输出(Soft Input Soft Output,SISO)译码器实现,其性能逼近Shannon限,即在高信噪比下能实现接近无误码传输。 ** VHDL语言 ** VHDL(VHSIC Hardware Description Language,超高速集成电路硬件描述语言)是一种用于电子设计自动化(EDA)的硬件描述语言,广泛应用于数字系统的设计和实现,包括 FPGA(Field-Programmable Gate Array)和 ASIC(Application-Specific Integrated Circuit)等。VHDL允许设计师以结构化的方式描述数字系统的逻辑功能,然后可以被编译、仿真和综合成实际的电路。 ** Turbo码的VHDL实现 ** 在VHDL中实现Turbo码涉及以下几个关键组件: 1. **编码器**:Turbo码的编码器通常由一个RSC(Rate-1/2, Systematic Convolutional)编码器和一个IRC(Interleaved Rate-1/2, Recursive Systematic Convolutional)编码器组成,这两个编码器的输出经过交织器后组合在一起形成码流。 2. **交织器**:交织器的作用是打乱输入数据的顺序,增加错误的随机性,使得译码器能够更有效地纠正错误。在VHDL中,可以通过查找表或者移位寄存器等方式实现。 3. **SISO译码器**:基于迭代的BCJR(Bahl-Cocke-Jelinek-Raviv)算法,SISO译码器接收软输入(即信道概率信息)并提供软输出(校正后的概率信息)。在VHDL中,这需要实现复杂的数学计算和状态机控制逻辑。 4. **解交织器**:解交织器的功能与交织器相反,它将SISO译码后的数据恢复到原始顺序,以便正确解码。 5. **输出判决**:根据解交织后的软输出进行硬判决,得出最终的解码数据。 ** VHDL源代码分析 ** 在提供的压缩包文件"src"中,很可能包含了上述各个组件的VHDL源代码文件。每个文件可能对应编码器、交织器、SISO译码器等部分,也可能包含主设计文件来协调各个模块。通过阅读和理解这些代码,可以学习如何在实际工程中实现Turbo码,并且了解VHDL在描述复杂数字逻辑时的语法和技巧。 这个项目对于理解和实现Turbo码以及熟悉VHDL编程都是一个很好的实践。通过这个源代码,学习者不仅可以掌握Turbo码的工作原理,还能深入了解VHDL在硬件描述中的应用,为未来在通信、嵌入式系统等领域的工作打下坚实基础。

turbo—VHDL.zip (93个子文件)

turbo—VHDL.zip (93个子文件)  src

src  vhdl

vhdl  sova_e.vhd 4KB

sova_e.vhd 4KB distance_synth.vhd 3KB

distance_synth.vhd 3KB zPermut_synth.vhd 4KB

zPermut_synth.vhd 4KB iteration_e.vhd 5KB

iteration_e.vhd 5KB min8_synth.vhd 6KB

min8_synth.vhd 6KB turbopack.vhd 26KB

turbopack.vhd 26KB punct_e.vhd 4KB

punct_e.vhd 4KB reduction_synth.vhd 3KB

reduction_synth.vhd 3KB accDist_e.vhd 3KB

accDist_e.vhd 3KB sova_synth.vhd 8KB

sova_synth.vhd 8KB coder_synth.vhd 3KB

coder_synth.vhd 3KB acs_synth.vhd 6KB

acs_synth.vhd 6KB reg_synth.vhd 3KB

reg_synth.vhd 3KB mux8_synth.vhd 4KB

mux8_synth.vhd 4KB abPermut_e.vhd 3KB

abPermut_e.vhd 3KB turboDec_e.vhd 4KB

turboDec_e.vhd 4KB mux2_e.vhd 3KB

mux2_e.vhd 3KB coder_e.vhd 3KB

coder_e.vhd 3KB accDistSel_e.vhd 3KB

accDistSel_e.vhd 3KB accDistSel_synth.vhd 4KB

accDistSel_synth.vhd 4KB opposite_e.vhd 3KB

opposite_e.vhd 3KB distances_synth.vhd 4KB

distances_synth.vhd 4KB distances_e.vhd 3KB

distances_e.vhd 3KB delayer_e.vhd 3KB

delayer_e.vhd 3KB partDistance_e.vhd 3KB

partDistance_e.vhd 3KB trellis1_e.vhd 4KB

trellis1_e.vhd 4KB delayer_synth.vhd 3KB

delayer_synth.vhd 3KB limiter_synth.vhd 5KB

limiter_synth.vhd 5KB subs_synth.vhd 3KB

subs_synth.vhd 3KB cod3_e.vhd 3KB

cod3_e.vhd 3KB stateSel_e.vhd 3KB

stateSel_e.vhd 3KB iteration_synth.vhd 14KB

iteration_synth.vhd 14KB trellis1_synth.vhd 7KB

trellis1_synth.vhd 7KB abPermut_synth.vhd 3KB

abPermut_synth.vhd 3KB min4_synth.vhd 4KB

min4_synth.vhd 4KB partDistance_synth.vhd 4KB

partDistance_synth.vhd 4KB mux4_synth.vhd 3KB

mux4_synth.vhd 3KB cod2_e.vhd 3KB

cod2_e.vhd 3KB clkDiv_e.vhd 3KB

clkDiv_e.vhd 3KB trellis2_e.vhd 4KB

trellis2_e.vhd 4KB mux4_e.vhd 3KB

mux4_e.vhd 3KB trellis2_synth.vhd 12KB

trellis2_synth.vhd 12KB subs_e.vhd 3KB

subs_e.vhd 3KB reduction_e.vhd 3KB

reduction_e.vhd 3KB distance_e.vhd 3KB

distance_e.vhd 3KB cod3_synth.vhd 3KB

cod3_synth.vhd 3KB extInf_e.vhd 4KB

extInf_e.vhd 4KB clkDiv_synth.vhd 3KB

clkDiv_synth.vhd 3KB min8_e.vhd 3KB

min8_e.vhd 3KB limiter_e.vhd 4KB

limiter_e.vhd 4KB punct_synth.vhd 5KB

punct_synth.vhd 5KB acs_e.vhd 4KB

acs_e.vhd 4KB adder_synth.vhd 3KB

adder_synth.vhd 3KB cod2_synth.vhd 3KB

cod2_synth.vhd 3KB .xhdl3.xref 152B

.xhdl3.xref 152B clkrst_e.vhd 3KB

clkrst_e.vhd 3KB mux8_e.vhd 3KB

mux8_e.vhd 3KB accDist_synth.vhd 4KB

accDist_synth.vhd 4KB zPermut_e.vhd 3KB

zPermut_e.vhd 3KB reg_e.vhd 3KB

reg_e.vhd 3KB interleaver_e.vhd 3KB

interleaver_e.vhd 3KB cmp2_synth.vhd 3KB

cmp2_synth.vhd 3KB mux2_synth.vhd 3KB

mux2_synth.vhd 3KB min4_e.vhd 3KB

min4_e.vhd 3KB extInf_synth.vhd 5KB

extInf_synth.vhd 5KB adder_e.vhd 3KB

adder_e.vhd 3KB turboDec_synth.vhd 7KB

turboDec_synth.vhd 7KB cmp2_e.vhd 3KB

cmp2_e.vhd 3KB opposite_synth.vhd 3KB

opposite_synth.vhd 3KB stateSel_synth.vhd 3KB

stateSel_synth.vhd 3KB clkrst_beh.vhd 3KB

clkrst_beh.vhd 3KB interleaver_synth.vhd 7KB

interleaver_synth.vhd 7KB myhdl

myhdl  coder.py 4KB

coder.py 4KB trellis.py 15KB

trellis.py 15KB noiser.py 5KB

noiser.py 5KB extInf.py 5KB

extInf.py 5KB turboTop.py 9KB

turboTop.py 9KB synthesis.py 191B

synthesis.py 191B acs.py 5KB

acs.py 5KB distances.py 7KB

distances.py 7KB select.py 4KB

select.py 4KB limiter.py 4KB

limiter.py 4KB misc.py 11KB

misc.py 11KB iteration.py 8KB

iteration.py 8KB punct.py 5KB

punct.py 5KB clock.py 4KB

clock.py 4KB interleaver.py 7KB

interleaver.py 7KB args.py 3KB

args.py 3KB testbench.py 7KB

testbench.py 7KB permut.py 4KB

permut.py 4KB sova.py 5KB

sova.py 5KB launchTurbo.py 7KB

launchTurbo.py 7KB turbo.pdf 36KB

turbo.pdf 36KB- 1

zjbxiaobai2014-06-13不错的例子,可以做参考用

zjbxiaobai2014-06-13不错的例子,可以做参考用 rugesanqiu2012-07-16这个代码主要是解码 编码的的内容很少

rugesanqiu2012-07-16这个代码主要是解码 编码的的内容很少

- 粉丝: 1

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 虚拟电脑病毒无害无需资源

- 探索Python数据可视化:Matplotlib库的深入指南

- 全站数据爬取技术与实践:方法、代码与策略

- 微信自动抢红包APP.zip毕业设计参考学习资料

- 为 Wireshark 能使用纯真网络 IP 数据库(QQwry)而提供的格式转换工具.zip

- 音频格式转换工具.zip学习资料程序资源

- 自用固件,合并openwrt和immortalwrt编译AX6(刷机有风险).zip

- 最新GeoLite2-City.mmdb,GeoLite2-Country.mmdb打包下载

- 基于BootStrap + Springboot + FISCO-BCOS的二手物品交易市场系统.zip

- 使用Java语言编写的九格拼游戏,找寻下曾经小时候的记忆.zip

信息提交成功

信息提交成功