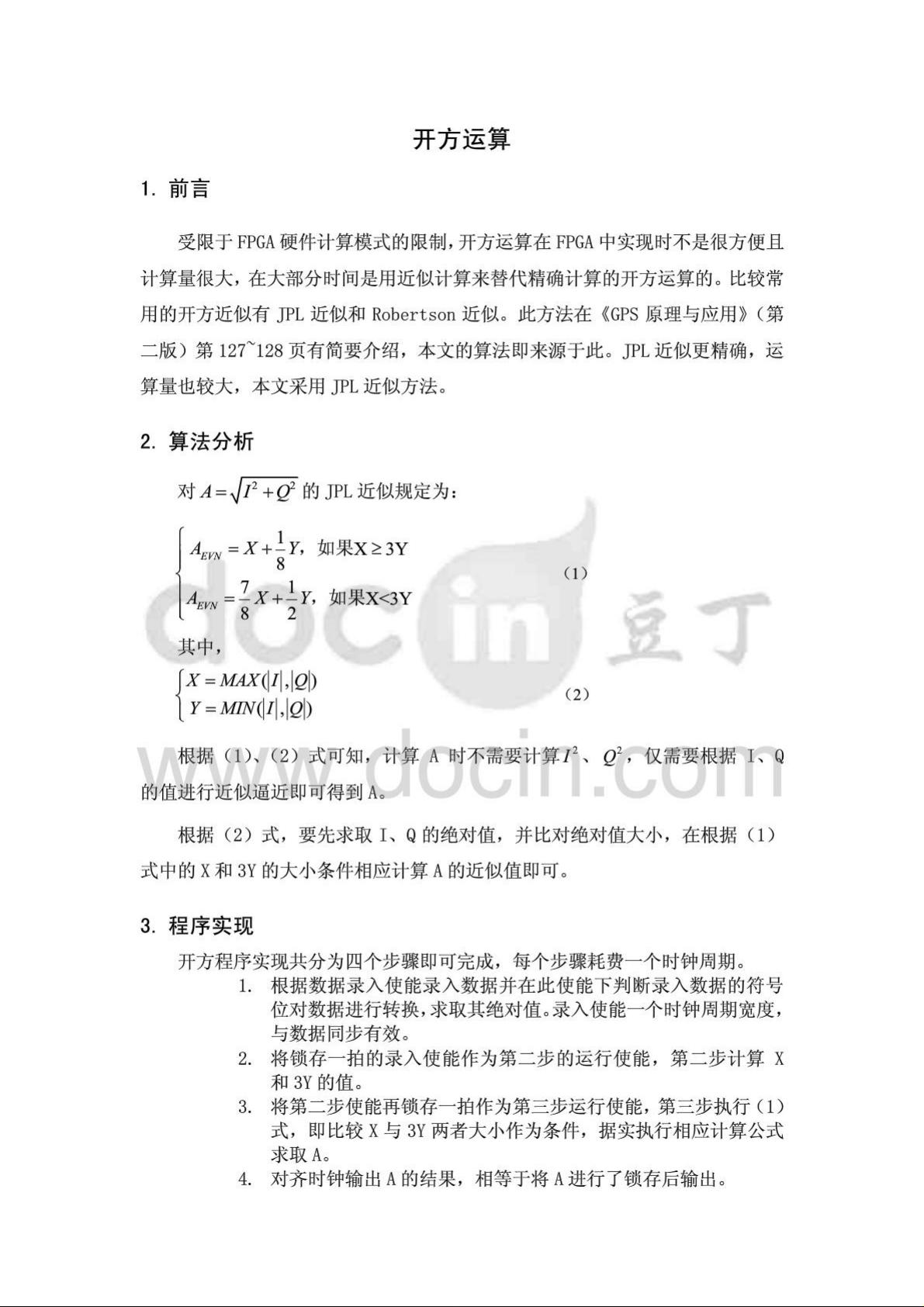

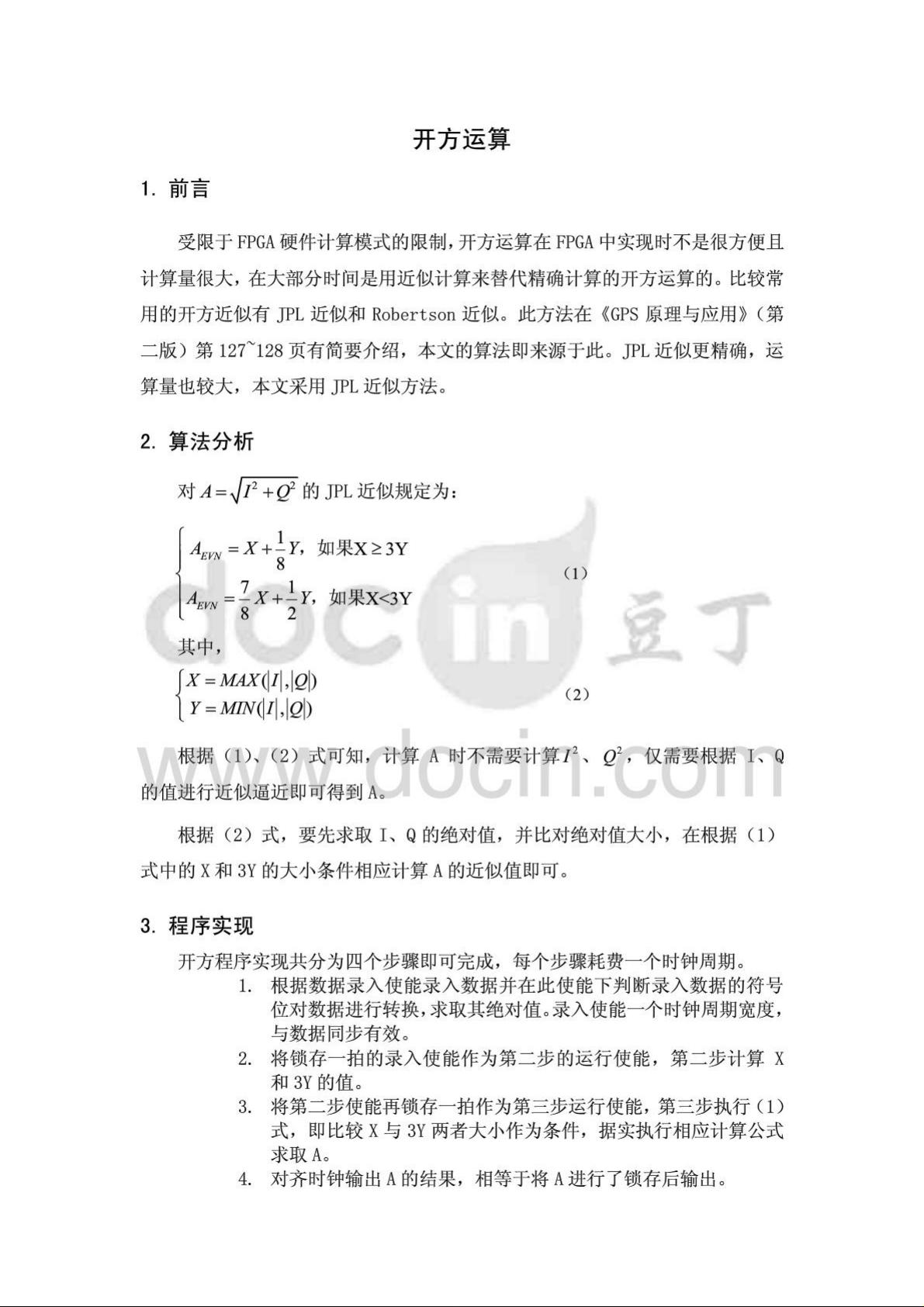

在数字信号处理和高速计算领域,FPGA(Field-Programmable Gate Array)因其灵活性和高性能而被广泛应用。本文将详细探讨如何在FPGA上实现复数开方运算,特别是基于JPL(Jet Propulsion Laboratory)算法的近似运算方法。 复数开方运算在通信系统、信号分析和控制系统中具有重要应用,它涉及到对复数形式的数据进行平方根提取。复数由实部和虚部组成,表示为`z = a + bi`,其中`a`是实部,`b`是虚部,`i`是虚数单位。复数开方的结果也是一个复数,其形式为`√z = √(a + bi) = ±(√(d/2) + i*sign(b)*√((d - a)/2))`,其中`d = a² + b²`。 JPL算法是NASA喷气推进实验室提出的一种快速、近似的浮点运算算法,特别适合硬件实现,包括在FPGA上的实现。该算法通过对数值进行一系列的位操作和简单的算术运算,有效地降低了复杂度,同时保持了较高的精度。在FPGA实现中,这种算法可以显著减少逻辑资源的消耗,提高系统的运行速度。 在"sqrt_16.vhd"文件中,很可能是用VHDL语言实现的16位复数开方单元。VHDL是一种硬件描述语言,用于描述数字逻辑系统,包括FPGA的设计。设计可能包含输入复数的实部和虚部,以及相应的输出结果。该实现可能会采用流水线结构,使得每个时钟周期可以处理一个或多个复数运算,提高系统的吞吐量。 JPL算法的实现通常会分为几个步骤: 1. **预处理**:将输入的复数转换为适合算法的标准格式,例如,可能需要将复数的绝对值转换为二进制对数。 2. **迭代过程**:通过一系列的迭代步骤,逐步逼近复数的平方根。这些迭代可能涉及位移、加法、乘法和比较等基本操作。 3. **后处理**:将迭代得到的结果转换回原复数格式,并可能进行舍入和规格化以提高精度。 " FPGA实现开方运算算法.pdf"文档应该提供了关于JPL算法的详细理论背景和具体实现细节。它可能包括算法的数学描述、误差分析、硬件资源利用率评估,以及性能比较等内容。阅读这份文档可以帮助我们深入理解复数开方运算的硬件实现原理,优化设计,以及如何在实际应用中调整算法以满足特定精度和速度需求。 FPGA上的复数开方运算通过高效的JPL算法实现,可以为数字信号处理系统提供实时、高精度的运算能力。这种实现方式对于需要大量复数运算的应用,如无线通信系统中的快速傅里叶变换(FFT)或者滤波器设计,具有重大意义。通过VHDL等硬件描述语言进行设计,开发者可以充分利用FPGA的并行处理能力,达到最优的性能与资源利用率。

fpga复数开方sqrt.rar (2个子文件)

fpga复数开方sqrt.rar (2个子文件)  sqrt_16.vhd 3KB

sqrt_16.vhd 3KB FPGA实现开方运算算法.pdf 310KB

FPGA实现开方运算算法.pdf 310KB- 1

- 粉丝: 2

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功