2

Data Sheet

2 Mbit / 4 Mbit / 8 Mbit Multi-Purpose Flash

SST39LF200A / SST39LF400A / SST39LF800A

SST39VF200A / SST39VF400A / SST39VF800A

©2001 Silicon Storage Technology, Inc. S71117-04-000 6/01 360

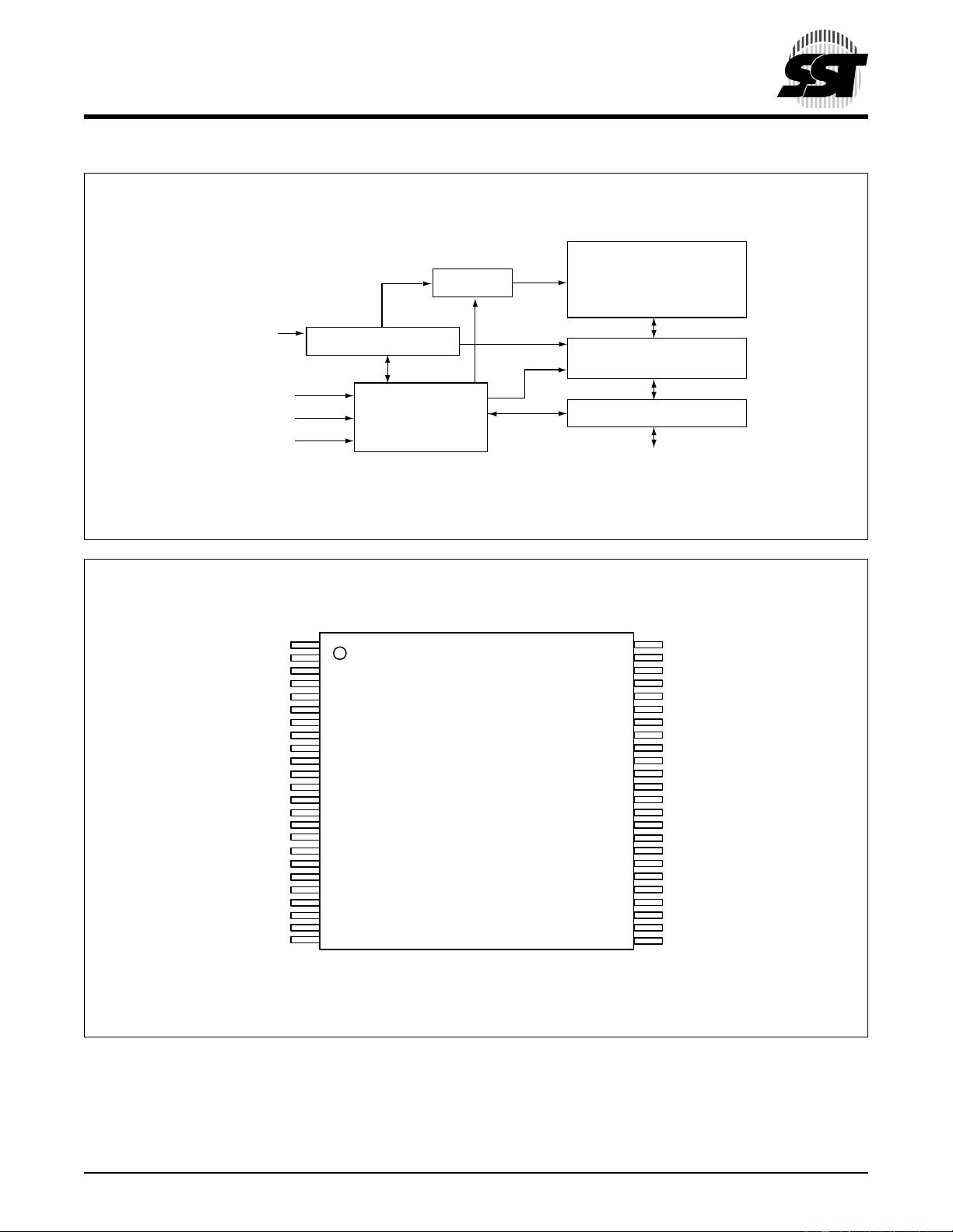

Device Operation

Commands are used to initiate the memory operation func-

tions of the device. Commands are written to the device

using standard microprocessor write sequences. A com-

mand is written by asserting WE# low while keeping CE#

low. The address bus is latched on the falling edge of WE#

or CE#, whichever occurs last. The data bus is latched on

the rising edge of WE# or CE#, whichever occurs first.

Read

The Read operation of the SST39LF200A/400A/800A and

SST39VF200A/400A/800A is controlled by CE# and OE#,

both have to be low for the system to obtain data from the

outputs. CE# is used for device selection. When CE# is

high, the chip is deselected and only standby power is con-

sumed. OE# is the output control and is used to gate data

from the output pins. The data bus is in high impedance

state when either CE# or OE# is high. Refer to the Read

cycle timing diagram for further details (Figure 3).

Word-Program Operation

The SST39LF200A/400A/800A and SST39VF200A/400A/

800A are programmed on a word-by-word basis. Before

programming, one must ensure that the sector, in which

the word which is being programmed exists, is fully erased.

The Program operation consists of three steps. The first

step is the three-byte load sequence for Software Data Pro-

tection. The second step is to load word address and word

data. During the Word-Program operation, the addresses

are latched on the falling edge of either CE# or WE#,

whichever occurs last. The data is latched on the rising

edge of either CE# or WE#, whichever occurs first. The

third step is the internal Program operation which is initi-

ated after the rising edge of the fourth WE# or CE#, which-

ever occurs first. The Program operation, once initiated, will

be completed within 20 µs. See Figures 4 and 5 for WE#

and CE# controlled Program operation timing diagrams

and Figure 16 for flowcharts. During the Program opera-

tion, the only valid reads are Data# Polling and Toggle Bit.

During the internal Program operation, the host is free to

perform additional tasks. Any commands issued during the

internal Program operation are ignored.

Sector/Block-Erase Operation

The Sector- (or Block-) Erase operation allows the system

to erase the device on a sector-by-sector (or block-by-

block) basis. The SST39LF200A/400A/800A and

SST39VF200A/400A/800A offers both Sector-Erase and

Block-Erase mode. The sector architecture is based on

uniform sector size of 2 KWord. The Block-Erase mode is

based on uniform block size of 32 KWord. The Sector-

Erase operation is initiated by executing a six-byte com-

mand sequence with Sector-Erase command (30H) and

sector address (SA) in the last bus cycle. The Block-Erase

operation is initiated by executing a six-byte command

sequence with Block-Erase command (50H) and block

address (BA) in the last bus cycle. The sector or block

address is latched on the falling edge of the sixth WE#

pulse, while the command (30H or 50H) is latched on the

rising edge of the sixth WE# pulse. The internal Erase

operation begins after the sixth WE# pulse. The End-of-

Erase operation can be determined using either Data#

Polling or Toggle Bit methods. See Figures 9 and 10 for tim-

ing waveforms. Any commands issued during the Sector-

or Block-Erase operation are ignored.

Chip-Erase Operation

The SST39LF200A/400A/800A and SST39VF200A/400A/

800A provide a Chip-Erase operation, which allows the

user to erase the entire memory array to the “1” state. This

is useful when the entire device must be quickly erased.

The Chip-Erase operation is initiated by executing a six-

byte command sequence with Chip-Erase command (10H)

at address 5555H in the last byte sequence. The Erase

operation begins with the rising edge of the sixth WE# or

CE#, whichever occurs first. During the Erase operation,

the only valid read is Toggle Bit or Data# Polling. See Table

4 for the command sequence, Figure 8 for timing diagram,

and Figure 19 for the flowchart. Any commands issued dur-

ing the Chip-Erase operation are ignored.

Write Operation Status Detection

The SST39LF200A/400A/800A and SST39VF200A/400A/

800A provide two software means to detect the completion

of a write (Program or Erase) cycle, in order to optimize the

system write cycle time. The software detection includes

two status bits: Data# Polling (DQ

7

) and Toggle Bit (DQ

6

).

The End-of-Write detection mode is enabled after the rising

edge of WE#, which initiates the internal Program or Erase

operation.

The actual completion of the nonvolatile write is asynchro-

nous with the system; therefore, either a Data# Polling or

Toggle Bit read may be simultaneous with the completion

of the write cycle. If this occurs, the system may possibly

get an erroneous result, i.e., valid data may appear to con-

flict with either DQ

7

or DQ

6

. In order to prevent spurious

rejection, if an erroneous result occurs, the software routine

should include a loop to read the accessed location an

additional two (2) times. If both reads are valid, then the

device has completed the write cycle, otherwise the rejec-

tion is valid.

demo02222013-03-25对我没多大作用

demo02222013-03-25对我没多大作用 bravecaicai2014-03-20好用的东西啊,太感谢啦

bravecaicai2014-03-20好用的东西啊,太感谢啦 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功