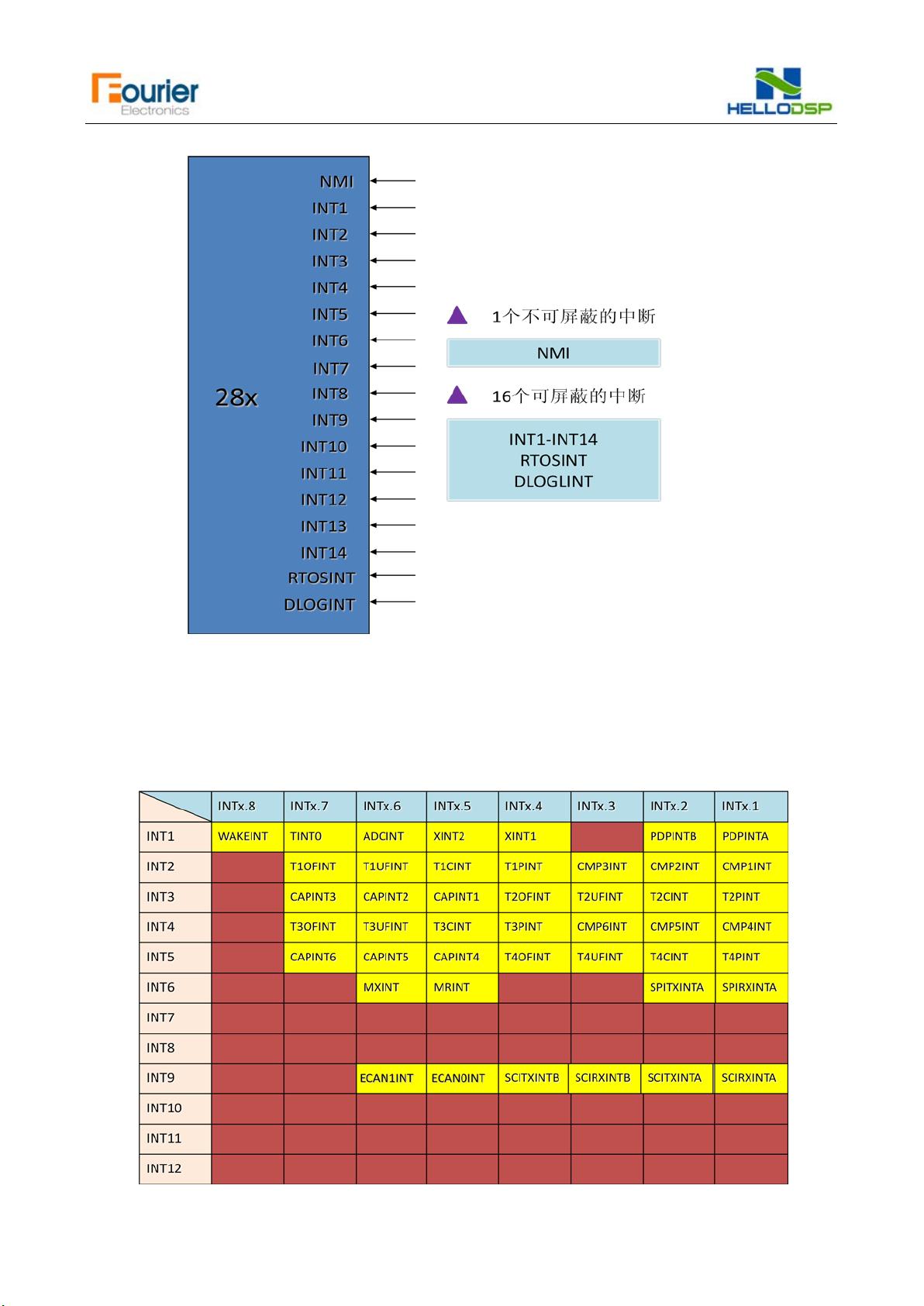

### DSP2812中断系统解析 #### 中断的基本概念 中断(Interrupt)是一种硬件或软件触发的事件,它的核心作用在于使CPU暂时停止当前正在执行的主程序,转而去执行一个预先定义好的中断服务程序(ISR)。这种机制在事件驱动型的处理器中尤为关键,因为它允许处理器实时响应外部或内部的事件,而无需一直主动查询,从而极大地提高了系统效率和响应速度。 #### DSP2812的中断系统架构 在深入探讨DSP2812的中断系统之前,我们首先来理解其基本结构。TI公司的DSP2812处理器支持一个非屏蔽中断(NMI)和16个可屏蔽中断(INT1-INT14、RTOSINT和DLOGINT)。然而,在实际应用中,我们更多关注的是可屏蔽中断中的INT1至INT12,它们构成了日常开发中最常用的中断资源。 #### 外设中断控制器PIE的作用 DSP2812的复杂性在于其内部集成了大量的外设,每个外设都有可能产生一个或多个中断请求。为了有效管理这些中断请求,DSP2812引入了外设中断控制器(PIE)的概念。PIE作为一个独立的模块,负责接收来自不同外设的中断请求,并对其进行初步的处理和筛选,最终将它们映射到CPU的中断线上,从而决定哪些中断请求会被CPU执行。 #### PIE的中断分组与管理 PIE能够管理多达96个不同的中断,这些中断被分为12个组,每组包含8个中断,共计96个中断。每一个组的中断都通过特定的方式与CPU的12条中断线之一相连,即INT1至INT12。值得注意的是,尽管PIE理论上可以管理96个中断,但在DSP2812的实际应用中,仅启用了其中的45个,其余的预留空间为将来可能添加的新功能做准备。 #### 中断执行机制 在了解了PIE的结构后,我们进一步探讨中断的执行机制。DSP2812采用了一种三层中断管理模型:外设级、PIE级和CPU级。这意味着一个中断请求要经过三个层次的检查才能最终被执行: 1. **外设级**:中断首先由外设产生,如果外设的中断允许位被设置,则中断信号被传递到PIE。 2. **PIE级**:PIE接收到中断信号后,会对中断请求进行处理。这一阶段,PIE检查中断是否被允许,如果允许,它将中断请求转发给CPU。 3. **CPU级**:CPU接收到中断请求后,检查CPU的中断允许状态。如果CPU的中断允许位被设置,那么中断服务程序将被执行;否则,中断将被忽略。 #### 结论 在DSP2812中,中断系统的高效管理和执行是确保系统实时性和响应性的关键。通过合理配置外设中断控制器PIE,开发者可以灵活地控制中断的优先级和响应顺序,从而使DSP2812能够在复杂的实时应用环境中发挥其最佳性能。理解并掌握中断系统的工作原理,对于利用DSP2812进行高效编程至关重要。

剩余7页未读,继续阅读

- 粉丝: 1

- 资源: 7

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 创建一个Flutter todolist应用

- 2025年销售工作计划.docx

- 厦门大学大数据团队详述:大模型技术及其在多领域的应用与展望

- script2.ipynb

- TEMU官方API文档资源包(2025/03/10)

- 公司人事管理信息系统小程序

- js微信小程序花麻将胡牌分数计算器源码!

- 管家婆辉煌ERP H3 13.11.zip

- 管家婆辉煌ERP H5 V1311.zip

- 管家婆辉煌ERP V13.02.zip

- 水火箭————————————————————————

- elastcsearch-7.10.2 docker镜像压缩包

- 教育管理教研组全维发展蓝图:全景学术成长体系优化与命名策略设计 这篇文章详细分析并优化了原有的“全景学术成长体系”名称,旨在创建一个更具吸引力且准确反

- 姓名+新员工花名册.xlsx

- 5G接入网架构基础及其相关部署方法

- kernel-uek-3.8.13-44.1.1.el6uek.x86_64.rpm

信息提交成功

信息提交成功