没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Published Specifications QSFP-DD MSA Hardware Rev 7.1

© QSFP-DD MSA

Page 1 June 25, 2024

1

2

QSFP-DD MSA 3

4

5

QSFP-DD/QSFP-DD800/QSFP-DD1600 Hardware Specification 6

7

for 8

9

QSFP DOUBLE DENSITY 8X PLUGGABLE TRANSCEIVERS 10

11

12

Revision 7.1 13

14

15

June 25, 2024 16

17

18

Abstract: This specification defines: the electrical and optical connectors, electrical signals and power supplies, 19

mechanical and thermal requirements of the pluggable QSFP Double Density (QSFP-DD/QSFP-DD800/QSFP-20

DD1600) connector and cage system. QSFP-DD MSA family of modules and cages remain fully backward 21

compatible with the classic QSFP+ formfactor. This document provides a common specification for systems 22

manufacturers, system integrators, and suppliers of modules. 23

24

25

POINTS OF CONTACT: 26

Ali Ghiasi (Technical Editor)

Ghiasi Quantum

19947 Lindenbrook Lane

Cupertino, CA 95014

ali at ghiasiquantum dot com

Mark Nowell (Co-Chair)

Cisco

170 West Tasman Dr

San Jose, CA 95134

mnowell at cisco dot com

Scott Sommers (Co-Chair)

Molex

2222 Wellington Court

Lisle, IL 60532-1682

scott.sommers at molex dot com

27

Website: 28

www.QSFP-DD.com

29

30

Limitation on use of Information: 31

This specification is provided "AS IS" with NO WARRANTIES whatsoever and therefore the provision of this 32

specification does not include any warranty of merchantability, noninfringement, fitness for a particular 33

purpose, or any other warranty otherwise arising out of any proposal, specification or sample. The authors 34

further disclaim all liability, including liability for infringement of any proprietary rights, relating to use of 35

information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual 36

property rights is granted herein. 37

38

Permissions: 39

You are authorized to download, reproduce and distribute this document. All other rights are reserved. The 40

provision of this document should not be construed as the granting of any right to practice, make, use or 41

otherwise develop products that are based on the document. Any and all IP rights related to this document 42

and the designs disclosed within, except for the rights expressly mentioned above, are reserved by the 43

respective owners of those IP rights. 44

45

Published Specifications QSFP-DD MSA Hardware Rev 7.1

© QSFP-DD MSA

Page 2 June 25, 2024

Dedication: 1

The members of the QSFP-DD MSA would like to acknowledge the contributions of Mr. Edmund Poh. He was 2

an excellent engineer; his technical skills and collaborative attitude will be missed. 3

4

The following are Promoter member companies of the QSFP-DD MSA. 5

Broadcom

Foxconn Interconnect Technology

Lumentum

Cisco

Huawei

Nvidia

Corning

Intel

Molex

Coherent

Juniper Networks

TE Connectivity

6

The following are contributing member companies of the QSFP-DD MSA. 7

Accelink

Hakusan

Nokia

ACON

Hewlett Packard Enterprise

Panduit

Alibaba Group

Hisense Broadband

PHY-SI

Amphenol

Hitachi Metals

Ranovus

Applied Optoelectronics

H3C

Samtec

Apresia

Infinera

Semtech

Celestica

InnoLight

Senko

Ciena

JPC

Sicoya

CIG

Keysight Technologies

The Siemon Company

ColorChip

Leoni

Skorpios

Credo

Lorom Cable Connection

Source Photonics

Dell Technologies

Luxshare ICT

Spectra7 Microsystems

Delta Products

Macom

Spirent

Dust Photonics

Marvell

Sumitomo Electric

Eoptolink

MaxLinear

US Conec

Fourte

MultiLane

Xilinx

Fujitsu Optical Components

NEC Corporation

Yamaichi

Genesis Connected Solutions

8

9

Published Specifications QSFP-DD MSA Hardware Rev 7.1

© QSFP-DD MSA

Page 3 June 25, 2024

1

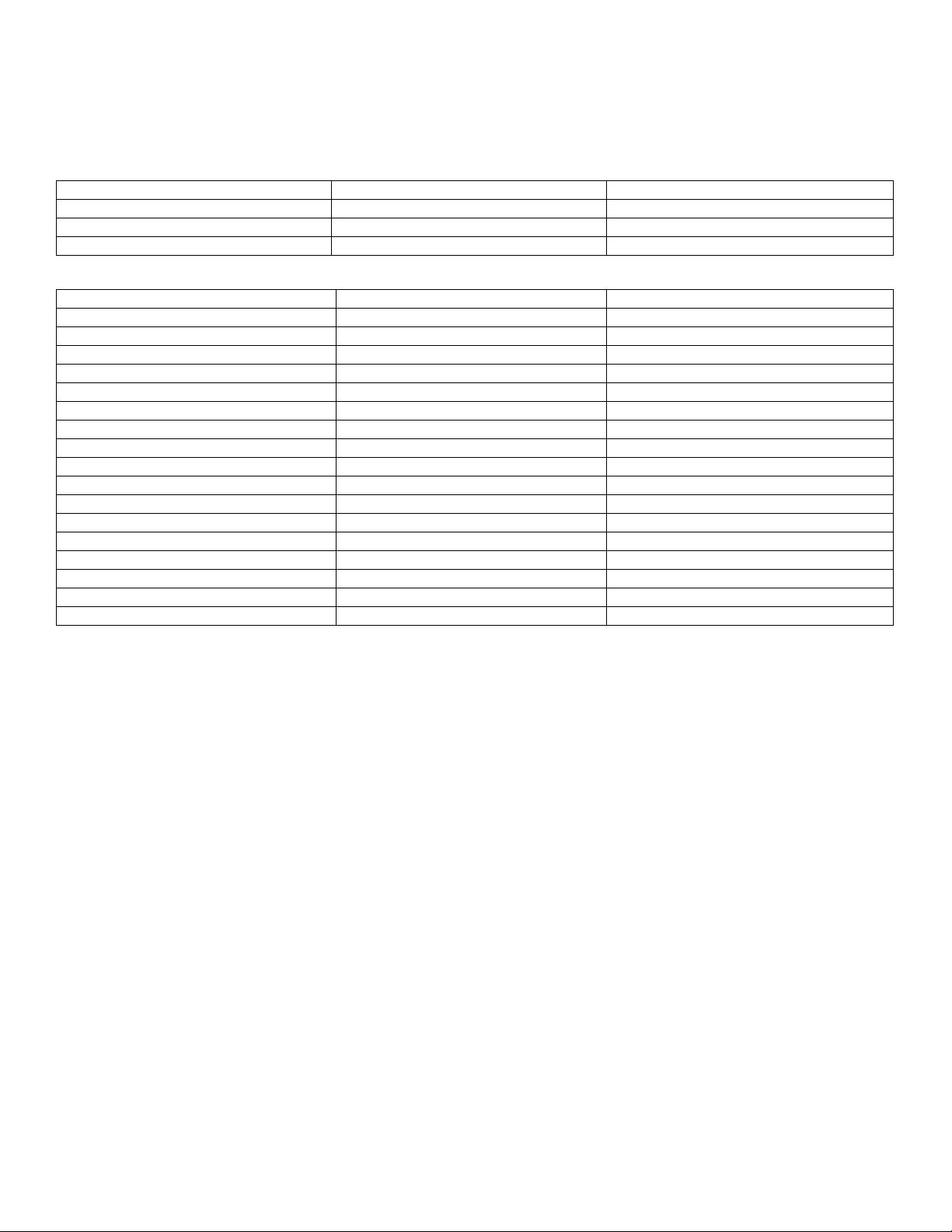

Change History: 2

Revision

Date

Changes

1.0

Sept 19, 2016

First public release

2.0

March 13, 2017

Second public release

3.0

Sept 19, 2017

Third public release

4.0

Sept 18, 2018

Fourth public release, Additions of thermal section, synchronous clocking in 4.9,

Mechanical updates.

5.0

July 9, 2019

Fifth public release, Added Module type 2A, changes to latch and cage drawings, added

ePPS contact, updated power supply testing, added BiDi optical port assignments.

5.1

August 7, 2020

6

th

public release, Chapter 7-Management Interface is now part of CMIS [5]. Port

mapping, optical connectors, and module color coding moved into a new Chapter 5.

6.0

May 20, 2021

7

th

public release, chapters for QSFP-DD800 and QSFP112 Mechanical and Board

Definitions are added. Chapter for QSFP112 Electrical and management timing added.

Updated power supply test method. Module power contacts rating increased from 1 A to

1.5 A and max module power dissipation increased to at least 25 W.

Programmable/Vendor specifics and ePPS/Clock contacts defined. Normative

connector performance Appendix A added.

6.01

May 28, 2021

8

th

public release, reinstated text inadvertently deleted in PCB notes in section 6.3 and

7.3, inadvertent change to a dimension in Figure 45 corrected.

6.2

March 11, 2022

9

th

public release, defined a new improved power supply test method, squelch level

reduced to 50 mV for 112G operation, press hole separation increased to 3.1 mm in

Figure 68. TWI bus timing removed from chapter 4 as identical timing diagram already

included in CMIS [5].

6.3

July 26, 2022

10

th

public release, updated termination definition for P/VSx and ePPS/Clock signals,

Figure 51 bezel opening height adjusted for consistency, updated Figure 75 glue zone.

7.0

Sept. 29, 2023

QSFP112 specifications were forwarded to SFF SNIA and are removed from this

specifications, see [35] and [36]. Missing ModSelL signal is added to the QSFP-DD

example circuit. QSFP-DD1600 mechanical specifications defined in chapter 8. Current

rating for each of QSFP-DD1600 contacts are increased to 2 A with feasibility of at least

40 W module power dissipation. Appendix F

defines QSFP-DD1600 enhanced thermal

design with bottom heat sink.

7.1

June 25, 2024

Updated module noise output measurement, see 4.7.5. Added alternate method to test

module noise tolerance, see 4.7.7. Figure 63 module stop changed to 3.6 mm. New

improved paddle card design for QSFP-DD1600, see 8.3. New 2x1 QSFP-DD1600 cage

system, see 8.5. Added optional high power module monitoring approach, see 9.4

.

QSFP-DD1600 module 2C defined, see Appendix C.

3

Foreword 4

The development work on this specification was done by the QSFP-DD MSA, an industry group. The 5

membership of the committee since its formation on Feb 2016 has included a mix of companies which are 6

leaders across the industry. 7

8

Published Specifications QSFP-DD MSA Hardware Rev 7.1

© QSFP-DD MSA

Page 4 June 25, 2024

1

TABLE of CONTENTS 2

3

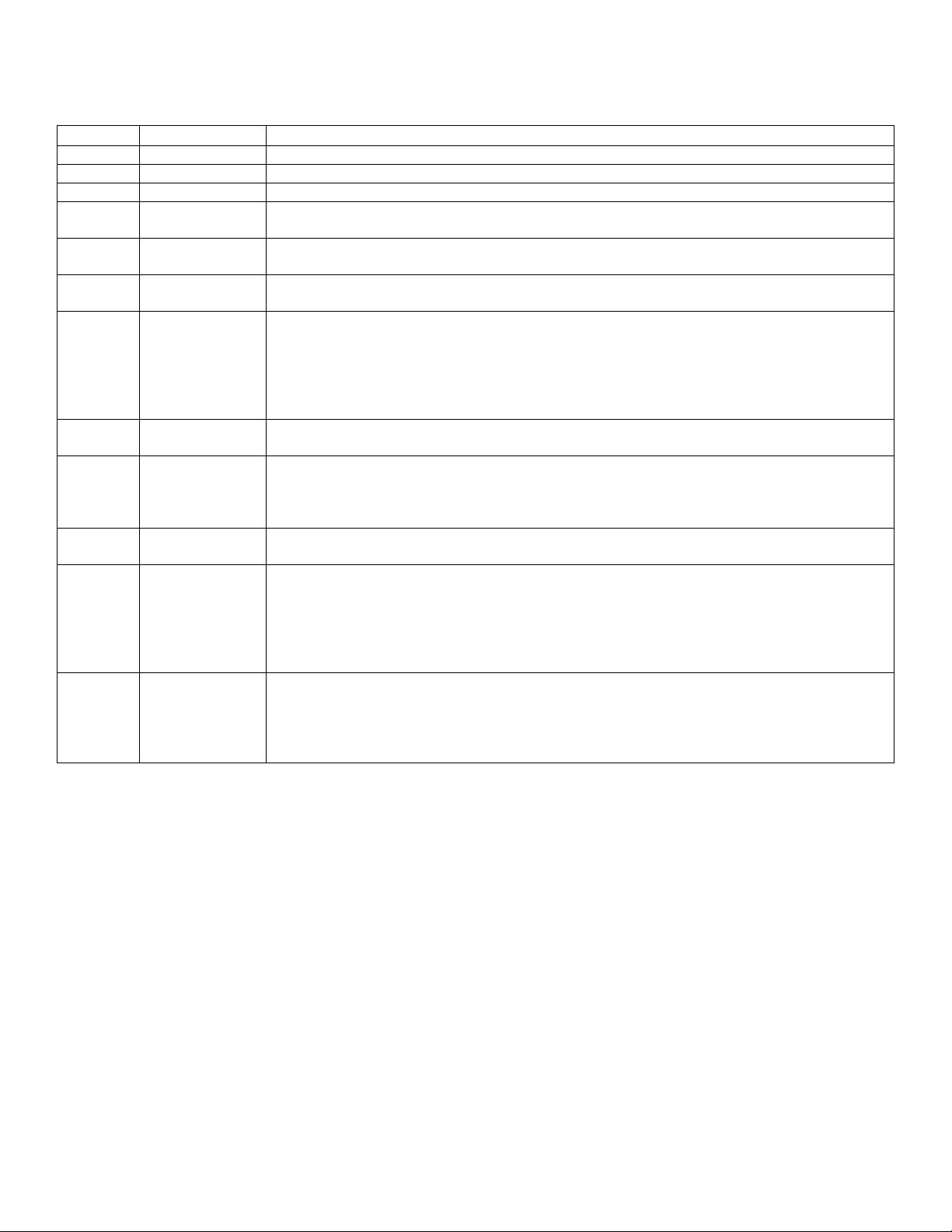

1 SCOPE .............................................................................................................................................................................. 10 4

1.1 DESCRIPTION OF CHAPTERS ................................................................................................................................................. 10 5

2 REFERENCES AND ACRONYMS .................................................................................................................................. 11 6

2.1 REFERENCE STANDARDS AND SPECIFICATIONS ................................................................................................................... 11 7

2.2 SFF SPECIFICATIONS: ........................................................................................................................................................... 12 8

2.3 ACRONYMS AND ABBREVIATIONS ........................................................................................................................................... 12 9

2.4 DOCUMENT SOURCE .............................................................................................................................................................. 12 10

3 INTRODUCTION ............................................................................................................................................................... 13 11

3.1 DOCUMENT OVERVIEW AND ORGANIZATION ......................................................................................................................... 13 12

3.2 APPLICATIONS ........................................................................................................................................................................ 14 13

3.3 MODULE MANAGEMENT AND CONTROL .................................................................................................................................. 14 14

4 QSFP-DD FORMFACTOR ELECTRICAL AND MANAGEMENT INTERFACE SPECIFICATIONS ........................... 15 15

4.1 ELECTRICAL CONNECTOR ...................................................................................................................................................... 15 16

4.2 LOW SPEED ELECTRICAL HARDWARE SIGNALS .................................................................................................................... 19 17

4.2.1 ModSelL ............................................................................................................................................................................ 19 18

4.2.2 ResetL ............................................................................................................................................................................... 19 19

4.2.3 LPMode/TxDis ................................................................................................................................................................. 19 20

4.2.4 ModPrsL............................................................................................................................................................................ 20 21

4.2.5 IntL/RxLOSL ..................................................................................................................................................................... 20 22

4.2.6 Programmable/Vendor Specific (Optional) .................................................................................................................. 20 23

4.2.7 ePPS/Clock PTP Reference Clock (Optional) ............................................................................................................ 20 24

4.3 EXAMPLES OF QSFP-DD MODULE FORMFACTOR HOST BOARD SCHEMATIC .................................................................... 22 25

4.4 LOW SPEED ELECTRICAL SPECIFICATION ............................................................................................................................. 26 26

4.4.1 TWI Logic Levels and Bus Loading .............................................................................................................................. 26 27

4.5 MANAGEMENT INTERFACE ..................................................................................................................................................... 27 28

4.5.1 Management Interface Timing Specification ............................................................................................................... 28 29

4.5.2 TWI Bus Pull Up Resistor ............................................................................................................................................... 28 30

4.5.3 Timing for soft control and status functions ................................................................................................................. 31 31

4.6 HIGH SPEED ELECTRICAL SPECIFICATION ............................................................................................................................ 34 32

4.6.1 Rx(n)(p/n) .......................................................................................................................................................................... 34 33

4.6.2 Tx(n)(p/n) .......................................................................................................................................................................... 34 34

4.7 POWER REQUIREMENTS ........................................................................................................................................................ 35 35

4.7.1 Power Classes and Maximum Power Consumption .................................................................................................. 35 36

4.7.2 Host Board Power Supply Filtering ............................................................................................................................... 36 37

4.7.3 Module Power Supply Specification ............................................................................................................................. 36 38

4.7.4 Host Board Power Supply Noise Output ...................................................................................................................... 38 39

4.7.5 Module Power Supply Noise Output ............................................................................................................................. 39 40

4.7.6 Module Power Supply Noise Tolerance Methods ...................................................................................................... 40 41

4.7.6.1 Module Power Supply Noise Tolerance with OpAmp ........................................................................................................... 40 42

4.7.6.2 Module Power Supply Noise Tolerance with Commercial Injector Probe .......................................................................... 42 43

4.8 ESD ........................................................................................................................................................................................ 44 44

4.9 CLOCKING CONSIDERATIONS ................................................................................................................................................. 44 45

4.9.1 Data Path Description ..................................................................................................................................................... 44 46

4.9.2 TX Clocking Considerations .......................................................................................................................................... 44 47

4.9.3 Rx Clocking Considerations ........................................................................................................................................... 44 48

5 OPTICAL PORT MAPPING AND OPTICAL INTERFACES .......................................................................................... 45 49

5.1 ELECTRICAL DATA INPUT/OUTPUT TO OPTICAL PORT MAPPING ............................................................................................. 45 50

5.2 OPTICAL INTERFACES ............................................................................................................................................................ 45 51

Published Specifications QSFP-DD MSA Hardware Rev 7.1

© QSFP-DD MSA

Page 5 June 25, 2024

5.2.1 MPO Optical Cable connections ................................................................................................................................... 48 1

5.2.2 Duplex LC Optical Cable connection ............................................................................................................................ 51 2

5.2.3 Dual CS Optical Cable connection ............................................................................................................................... 51 3

5.2.4 Quad SN Optical Cable connections ............................................................................................................................ 52 4

5.2.5 Quad MDC Optical Cable connection .......................................................................................................................... 52 5

5.2.6 Dual SN Optical Cable connections ............................................................................................................................. 53 6

5.2.7 Dual MDC Optical Cable connection ............................................................................................................................ 53 7

5.2.8 Dual Duplex LC Optical Cable connection .................................................................................................................. 54 8

5.2.9 Dual MPO-12 Optical Cable connection ...................................................................................................................... 55 9

5.3 MODULE COLOR CODING AND LABELING .............................................................................................................................. 56 10

6 QSFP-DD MECHANICAL AND BOARD DEFINITION ................................................................................................... 57 11

6.1 INTRODUCTION TO QSFP-DD/QSFP-DD800/QSFP-DD1600 MODULES ......................................................................... 57 12

6.2 DATUMS, DIMENSIONS AND COMPONENT ALIGNMENT.......................................................................................................... 59 13

6.3 MODULE FORM FACTORS FOR QSFP-DD/QSFP-DD800/QSFP-DD1600 ....................................................................... 61 14

6.4 MODULE FLATNESS AND ROUGHNESS .................................................................................................................................. 70 15

6.5 QSFP-DD MODULE PADDLE CARD DIMENSIONS NOTES ....................................................................................................... 71 16

6.6 MODULE EXTRACTION AND RETENTION FORCES .................................................................................................................. 73 17

6.7 QSFP-DD 2X1 STACKED ELECTRICAL CONNECTOR MECHANICAL ..................................................................................... 73 18

6.7.1 QSFP-DD 2x1 Connector and Cage host PCB layout ............................................................................................... 78 19

6.8 QSFP-DD SURFACE MOUNT ELECTRICAL CONNECTOR MECHANICAL ............................................................................... 81 20

6.8.1 QSFP-DD Surface mount connector and cage host PCB layout ............................................................................. 87 21

7 QSFP-DD800 MECHANICAL AND BOARD DEFINITION ............................................................................................. 89 22

7.1 INTRODUCTION ....................................................................................................................................................................... 89 23

7.2 QSFP-DD800 MODULE MECHANICAL DIMENSIONS .............................................................................................................. 89 24

7.3 QSFP-DD800 IMPROVED MODULE PADDLE CARD DIMENSIONS ........................................................................................... 94 25

7.4 QSFP-DD800 1X1 SMT CONNECTOR/CAGE ....................................................................................................................... 97 26

7.4.1 Surface mount connector and cage host PCB layout ................................................................................................ 97 27

7.5 2X1 SURFACE MOUNT TECHNOLOGY (SMT) CONNECTOR/CAGE ....................................................................................... 98 28

7.5.1 2x1 SMT Connector/Cage System ............................................................................................................................... 98 29

7.5.2 2x1 SMT Connector and Cage host PCB layout ...................................................................................................... 103 30

8 QSFP-DD1600 MECHANICAL AND BOARD DEFINITION......................................................................................... 107 31

8.1 INTRODUCTION ..................................................................................................................................................................... 107 32

8.2 QSFP-DD1600 MODULE MECHANICAL DIMENSIONS .......................................................................................................... 107 33

8.3 QSFP-DD1600 IMPROVED MODULE PADDLE CARD DIMENSIONS ...................................................................................... 109 34

8.4 QSFP-DD1600 1X1 SMT CONNECTOR/CAGE SYSTEM ..................................................................................................... 112 35

8.4.1 Surface mount connector and cage host PCB layout .............................................................................................. 112 36

8.4.2 QSFP-DD1600 Host Pad Assignment ....................................................................................................................... 113 37

8.4.3 QSFP-DD1600 Surface Mount Electrical Connector Mechanical .......................................................................... 114 38

8.4.4 QSFP-DD1600 Cage Flap ........................................................................................................................................... 115 39

8.5 2X1 SURFACE MOUNT TECHNOLOGY (SMT) CONNECTOR/CAGE ..................................................................................... 116 40

8.5.1 2x1 SMT Connector/Cage System ............................................................................................................................. 116 41

8.5.2 2x1 SMT Connector and Cage host PCB layout ...................................................................................................... 123 42

9 MODULE ENVIRONMENTAL AND THERMAL REQUIREMENTS ............................................................................. 126 43

9.1 THERMAL REQUIREMENTS ................................................................................................................................................... 126 44

9.2 THERMAL REQUIREMENTS – TIGHTER CONTROLLED ENVIRONMENTS ................................................................................ 126 45

9.3 EXTERNAL CASE AND HANDLE TOUCH TEMPERATURE ...................................................................................................... 126 46

9.4 SUPPLEMENTAL THERMAL CHARACTERISTICS FOR HIGH POWER MODULES (OPTIONAL) .................................................. 127 47

9.4.1 Example procedure to implement high power module monitoring ......................................................................... 127 48

APPENDIX A NORMATIVE MODULE AND CONNECTOR PERFORMANCE REQUIREMENTS ............................... 129 49

A.1 QSFP-DD/QSFP-DD800/QSFP-DD1600 PERFORMANCE TABLES ............................................................................... 129 50

剩余156页未读,继续阅读

资源评论

bingyuxxlove

- 粉丝: 6

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于springboot+Vue的在线互动学习网站设计(Java毕业设计,附源码,部署教程).zip

- 基于SpringBoot+Vue的的信息技术知识竞赛系统的设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于JSP的乡镇自来水收费系统+jsp(Java毕业设计,附源码,数据库,教程).zip

- 基于SSM的毕业论文管理系统+vue(Java毕业设计,附源码,数据库,教程).zip

- 基于SSM的安徽新华学院实验中心管理系统的设计与实现+jsp(Java毕业设计,附源码,数据库,教程).zip

- 基于SSM的班主任助理系统的设计与实现+jsp(Java毕业设计,附源码,数据库,教程).zip

- 基于SpringBoot+Vue的的网络海鲜市场系统的设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于SSM的毕业生就业信息统计系统+vue(Java毕业设计,附源码,数据库,教程).zip

- 基于springboot+Vue的医疗挂号管理系统(Java毕业设计,附源码,部署教程).zip

- 基于SSM的博客系统的设计与实现+vue(Java毕业设计,附源码,数据库,教程).zip

- 基于springboot+Vue的疫情信息管理系统2(Java毕业设计,附源码,部署教程).zip

- 基于springboot+Vue的疫情信息管理系统(Java毕业设计,附源码,部署教程).zip

- 基于SpringBoot+Vue的的农商对接系统的设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于SpringBoot+Vue的的失物招领平台的设计与实现(Java毕业设计,附源码,部署教程).zip

- 基于SSM的大学生兼职平台的设计与开发+jsp(Java毕业设计,附源码,数据库,教程).zip

- 基于SpringBoot+Vue的的实习管理系统(Java毕业设计,附源码,部署教程).zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功