TMS320F28335时钟(1) -----PLL倍频器的初始化详解.docx

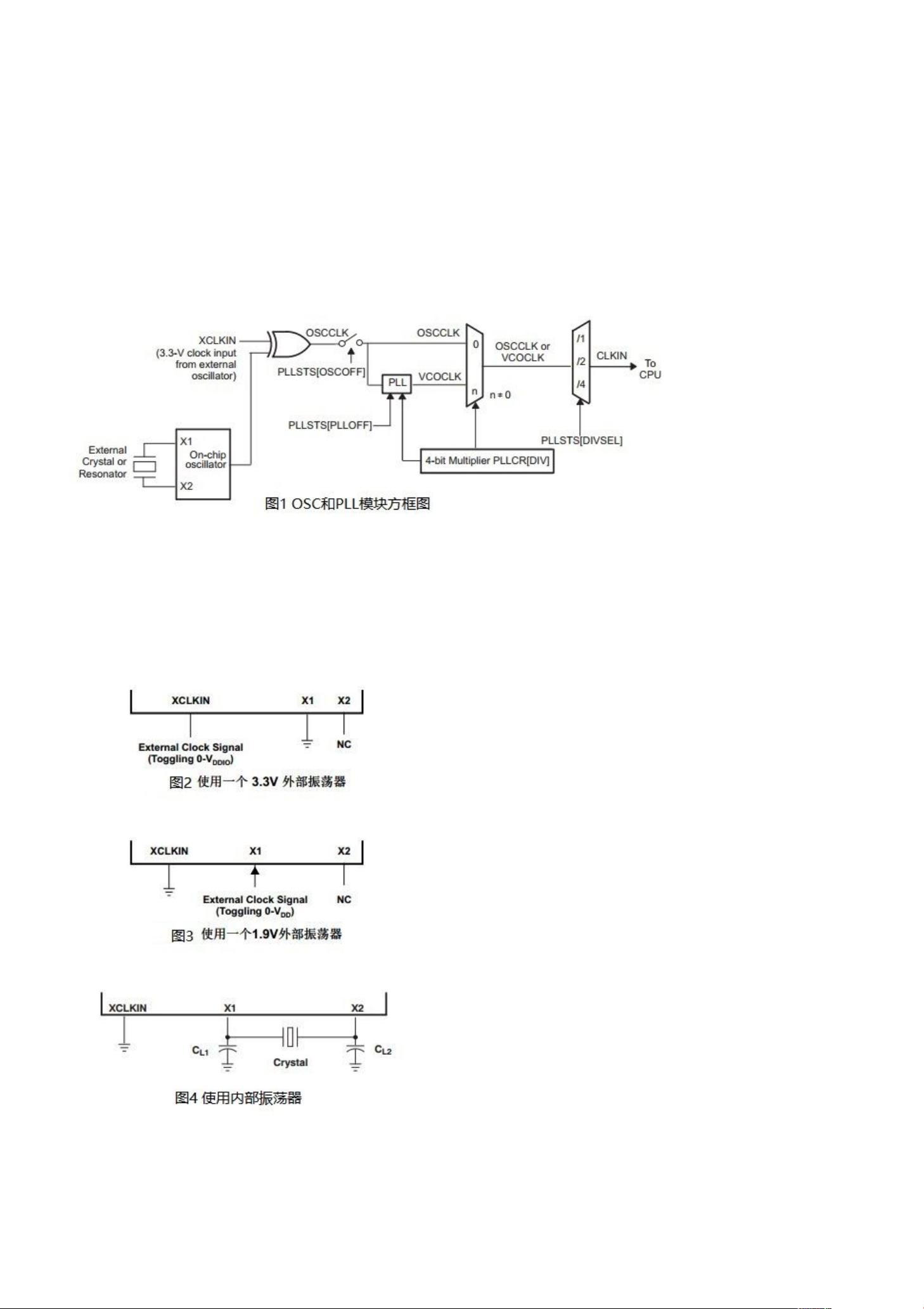

TMS320F28335时钟PLL倍频器的初始化详解 在本文中,我们将详细介绍TMS320F28335时钟PLL倍频器的初始化过程。PLL(Phase Locked Loop)倍频器是时钟模块的重要组成部分,它可以将外部时钟信号倍频到高频信号,以满足系统对时钟信号的需求。 PLL倍频器的主要功能是将外部时钟信号倍频到高频信号,以满足系统对时钟信号的需求。PLL倍频器的初始化过程包括两个寄存器:PLL状态寄存器PLLSTS和PLL控制寄存器PLLCR。 PLLSTS寄存器用于判断PLL的工作状态,而PLLCR寄存器用于配置PLL的倍频系数。在PLL初始化过程中,需要检测PLL的工作状态,并根据不同的工作状态对PLL进行配置,以产生合适的时钟信号。 PLL倍频器的配置包括选择时钟源、选择倍频系数、选择分频系数等步骤。在PLL初始化过程中,需要注意PLL的工作状态、时钟信号的稳定性等问题,以确保PLL倍频器的正确配置。 在本文中,我们将详细介绍PLL倍频器的初始化过程,并对PLL相关寄存器的使用进行分析。同时,我们还将介绍PLL倍频器的配置原则和注意事项,以帮助读者更好地理解PLL倍频器的初始化过程。 PLL相关寄存器包括PLL状态寄存器PLLSTS和PLL控制寄存器PLLCR。PLLSTS寄存器用于判断PLL的工作状态,而PLLCR寄存器用于配置PLL的倍频系数。 PLLSTS寄存器的主要位域包括MCLKSTS位和PLLLOCKS位。MCLKSTS位用于判断PLL的工作状态,而PLLLOCKS位用于判断PLL的锁定状态。 PLLCR寄存器的主要位域包括DIV位和LOCK位。DIV位用于选择PLL的倍频系数,而LOCK位用于判断PLL的锁定状态。 PLL倍频器的配置原则包括选择时钟源、选择倍频系数、选择分频系数等步骤。在PLL初始化过程中,需要注意PLL的工作状态、时钟信号的稳定性等问题,以确保PLL倍频器的正确配置。 PLL倍频器的注意事项包括在改变PLLCR[DIV]倍频系数前,必须满足两个条件:PLLSTS[DIVSEL]必须为0,而PLLSTS[MCLKSTS]必须为0。同时,在写入PLLCR寄存器之前,安全装置模块(看门狗)应该被禁用。 PLL倍频器的初始化过程是TMS320F28335时钟模块的重要组成部分。正确配置PLL倍频器可以确保系统对时钟信号的需求,而PLL相关寄存器的使用和配置原则是PLL倍频器初始化过程的关键部分。

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Matlab根据flac、pfc或其他软件导出的坐标及应力、位移数据再现云图 案例包括导出在flac6.0中导出位移的fish代码(也可以自己先准备软件导出的坐标数据及对应点的位移或应力数据,可根据需

- 拳皇97.exe拳皇972.exe拳皇973.exe

- 捕鱼达人1.exe捕鱼达人2.exe捕鱼达人3.exe

- 医疗骨折摄像检测29-YOLO(v5至v9)、COCO、CreateML、Darknet、Paligemma数据集合集.rar

- ks滑块加密算法与源代码

- 医护人员检测23-YOLOv8数据集合集.rar

- 1.电力系统短路故障引起电压暂降 2.不对称短路故障分析 包括:共两份自编word+相应matlab模型 1.短路故障的发生频次以及不同类型短路故障严重程度,本文选取三类典型的不对称短路展开研究

- C#连接sap NCO组件 X64版

- 开源基于51单片机的多功能智能闹钟设计,课设毕设借鉴参考

- 深度强化学习电气工程复现文章,适合小白学习 关键词:能量管理 深度学习 强化学习 深度强化学习 能源系统 优化调度 编程语言:python平台 主题:用于能源系统优化调度的深度强化学习算法的性能比较

信息提交成功

信息提交成功