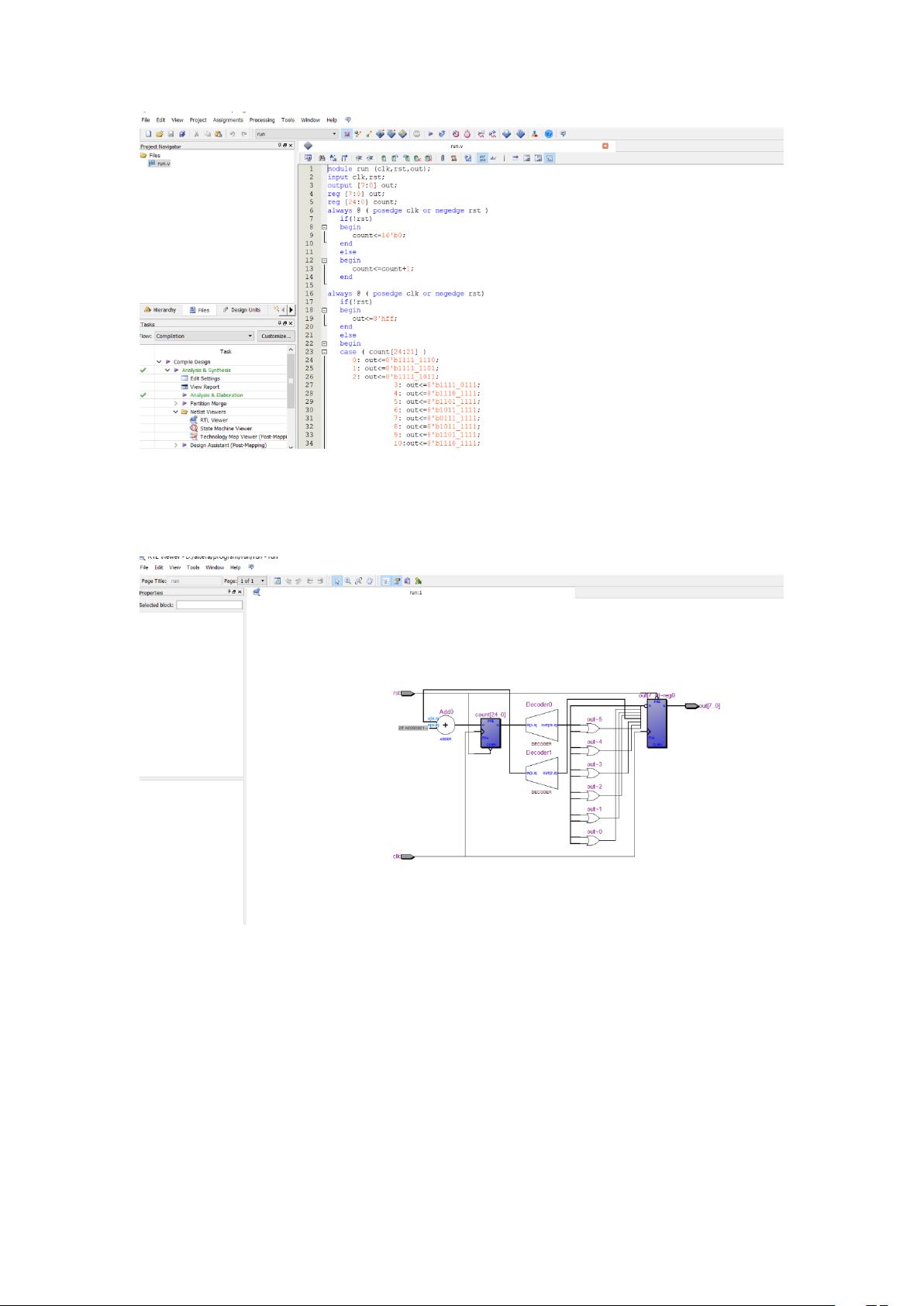

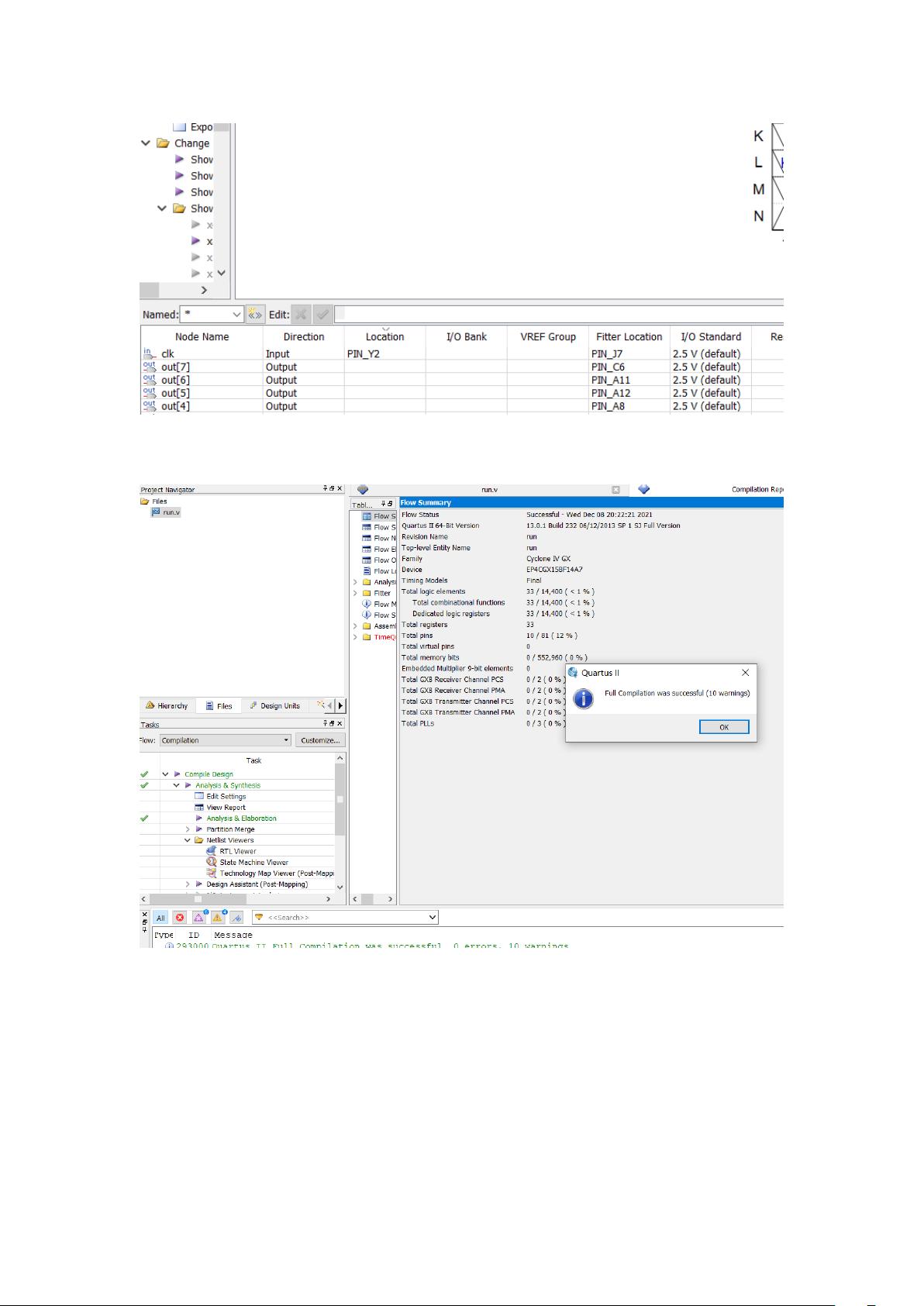

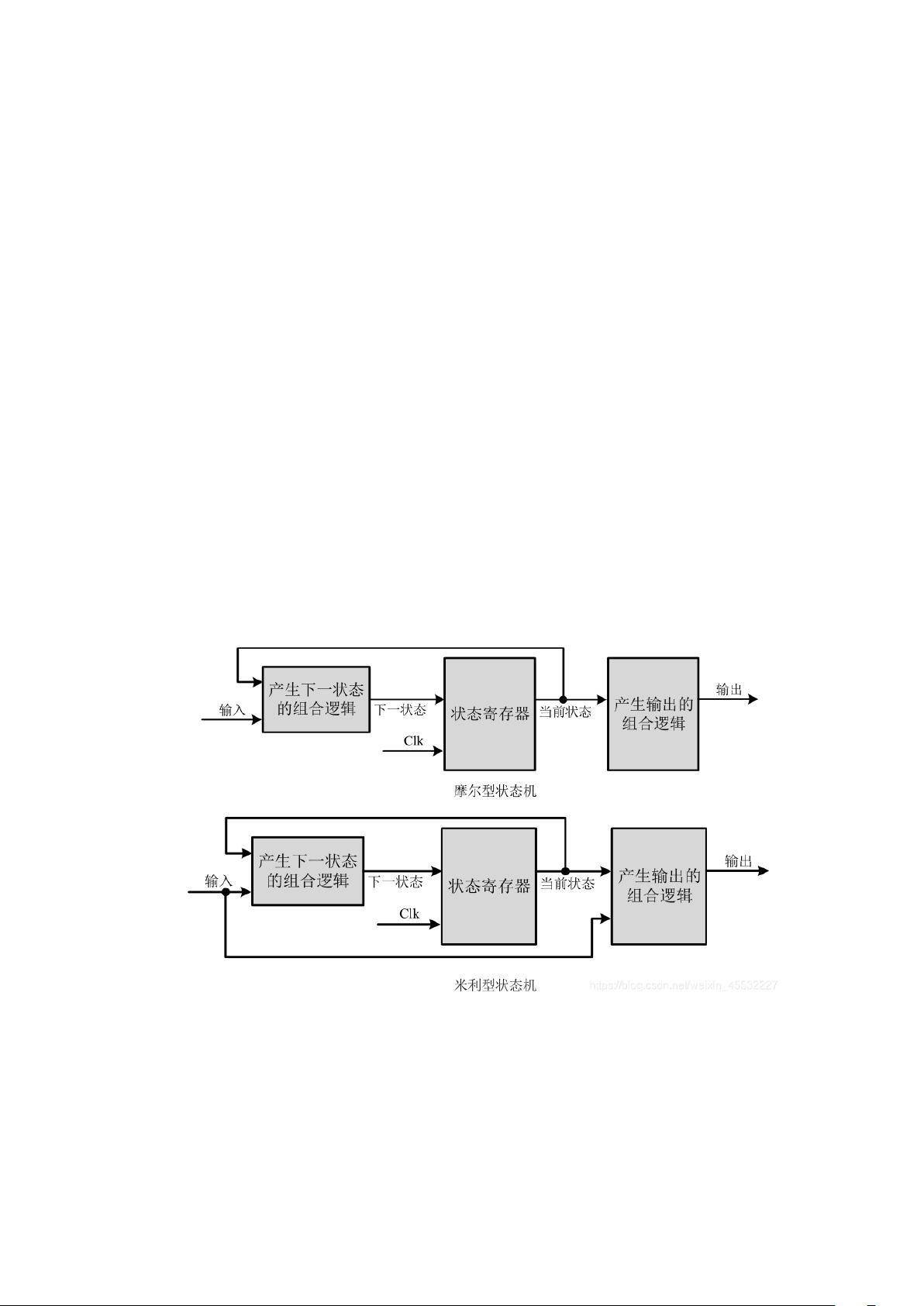

西工大计算机学院计算机数字逻辑实验报告,最近发现之前上传的部分资源下载,这里给出实验四的报告供同学们参考,报告中给出实验截图还有相关设计, 供各位同学参考 下面给出部分的实验内容: 掌握可综合Verilog语言进行状态机设计及测试验证; 2. 学习如何在FPGA进行设计实现。 安装开发工具ModelSim、Quartus的PC机、Altera DEII-115实验箱 1. 跑马灯设计及FPGA实现(run.v) 2. 有限状态机设计(教材Figure 6.86) 1.Quatusll使用流程 Quatusll的使用我们需要完成的是前面的七个步骤,分别是 第一步:编码 用文本编辑器正确编写源文件(本例run.v),并经modelsim仿真确认该电路设计正确. 第二步:新建工程 新建工程New project (注意工程名和设计文件的module名保持一致),选择和开发板一致的FPGA器件型号(本课程为Cyclone IV E系列EP4CE115F29C7) 第三步:添加文件 Add to project,将全部源文件 (本例run.v)添加到工程中 第四步:编译 Start 【知识点详解】 1. Verilog 语言:Verilog 是一种硬件描述语言(HDL),用于设计和描述数字系统的逻辑,包括集成电路和FPGA(Field-Programmable Gate Array)。在本实验中,学生需要掌握使用Verilog进行状态机的设计,并进行仿真验证,确保设计的正确性。 2. 状态机设计:状态机是描述电路行为的一种重要方法,它能够表示电路在不同时间点的行为变化。实验中涉及两种类型的状态机设计:跑马灯设计和基于教材Figure 6.86的有限状态机设计。状态机设计通常包括状态变量、输出和输入条件。学生需要理解状态机的基本要素,包括状态、输出和输入,并学会区分摩尔型和米勒型状态机。 3. FPGA 实现:FPGA是可编程逻辑器件,允许用户根据需要配置其内部逻辑。在实验中,学生需要学习如何在FPGA上实现Verilog设计,包括选择合适的器件型号(如Cyclone IV E系列EP4CE115F29C7),使用开发工具(如Quartus)进行工程创建、源文件添加、编译、电路结构查看、管脚绑定以及全编译生成可下载文件(*.sof)。 4. Quartus 使用流程:Quartus是Altera公司(现Intel FPGA部门)的开发软件,实验详细介绍了Quartus的使用步骤,包括编码、新建工程、添加文件、编译、查看电路结构、管脚绑定和全编译。学生需要熟练掌握这些操作,以便在实际设计中有效地实现和验证逻辑设计。 5. ModelSim仿真:ModelSim是一款常用的HDL仿真工具,学生需使用它来仿真Verilog代码,确认设计的功能正确性。在编码阶段,需要通过ModelSim进行仿真,确保电路设计符合预期。 6. FPGA 开发流程:实验详细描述了FPGA开发的一般流程,包括源代码编写、工程创建、器件选择、文件添加、编译、查看 RTL 视图、管脚绑定和全编译。这些步骤对于理解和实践FPGA设计至关重要。 7. 跑马灯设计:跑马灯是一种常见的FPGA入门设计,通常涉及LED灯的顺序点亮。学生需要利用状态机原理设计跑马灯的逻辑,实现LED灯的循环点亮效果。 8. 状态机描述方式:除了Verilog代码描述,状态机还可以通过状态转移图和状态转移列表来表示。状态转移图直观展示状态之间的转换,而状态转移列表则以表格形式列出状态、输入和输出关系。 通过这个实验,学生不仅能深入理解Verilog语言和状态机设计,还能熟悉FPGA开发流程和相关工具的使用,提升他们的数字逻辑设计和实践能力。

剩余15页未读,继续阅读

- 粉丝: 1970

- 资源: 10

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功