没有合适的资源?快使用搜索试试~ 我知道了~

SSD2832 ICdatasheet

需积分: 0 20 下载量 160 浏览量

2023-09-28

11:13:16

上传

评论 2

收藏 9.13MB PDF 举报

温馨提示

试读

178页

MIPI 2832中文版手册

资源推荐

资源详情

资源评论

SOLOMON SYSTECH

SEMICONDUCTOR TECHNICAL DATA

This document contains information on a new product. Specifications and information herein are subject to change

without notice.

http://www.solomon-systech.com

SSD2832

Rev 1.5

P 1/178

Aug. 2020

Copyright 2020 Solomon Systech Limited

Advanced Information

MIPI C&D-PHY TX Bridge Chip

SSD2832

Solomon Systech

Aug. 2020

2/178

Rev 1.5

SSD2832

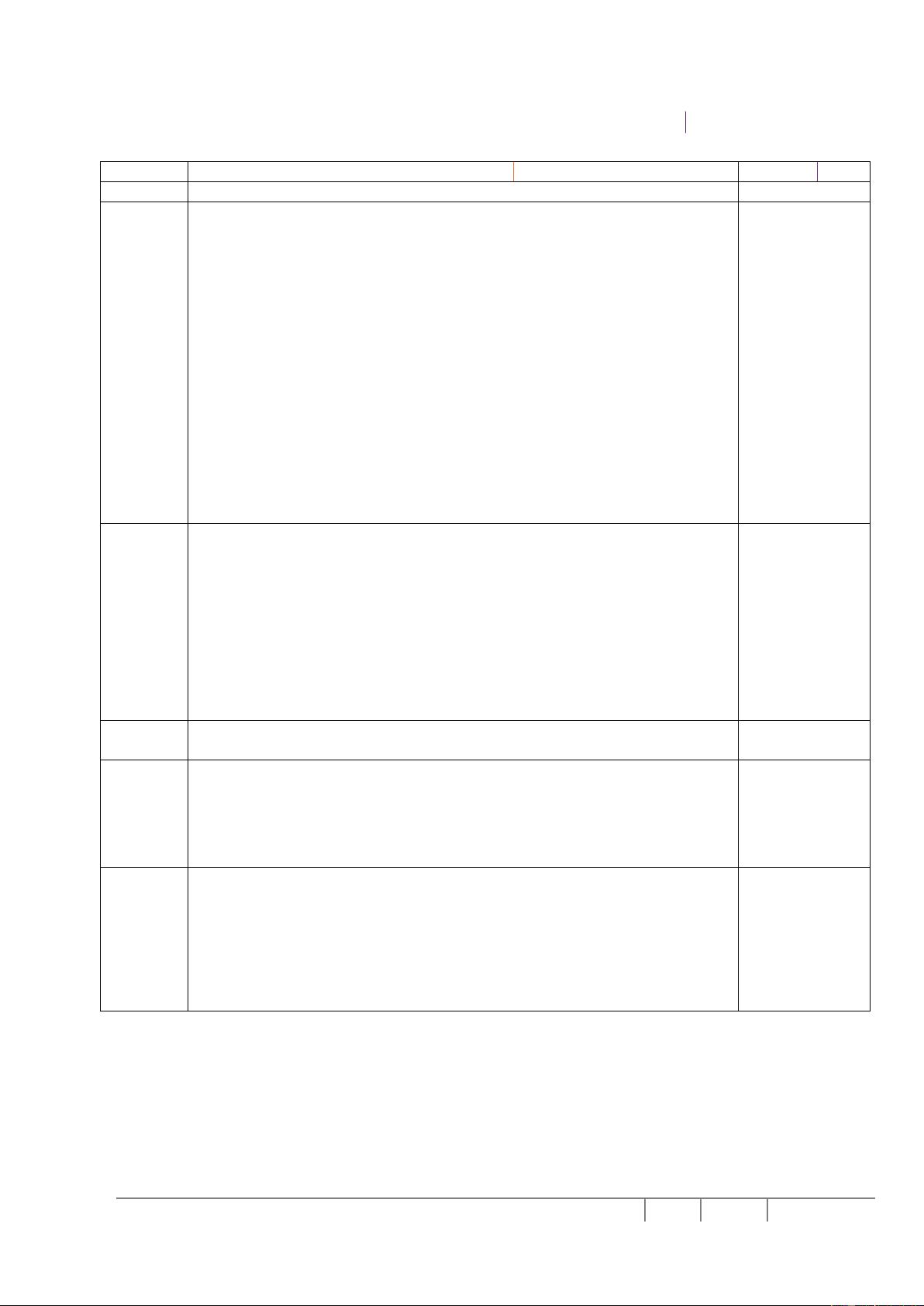

APPENDIX: IC REVISION HISTORY OF SSD2832 SPECIFICATION

Version

Change Items

Effective Date

1.0

1

st

Release

22-Sep-2017

1.1

1. Modified the following pin assignment

H19 changed from NC to VSS

H20 changed from NC to VSS

B14 changed from NC to Data0_12

H18 changed from HSYNC2 to NC

A1 changed from HSYNC3 to NC

H8 changed from VSYNC3 to NC

D22 changed from VSYNC 2 to NC

K16 changed from DEN2 to NC

E6 changed from DEN3 to NC

A2 changed from PCLK3 to NC

E10 changed from PCLK2 to NC

H2 changed from DATA0_60 to NC

H1 changed from DATA0_61 to NC

J3 changed fromDATA0_62 to NC

K2 changed from DATA0_63 to NC

N1 changed from CSX1 to NC

2. changed TX0_B1 to TXA_B1

18-Oct-2017

1.2

1. Added 4 lane mode in 0xDE

2. Revised 0xBA bit[15:14] from PEN to FR

3. Added mipi timing description on local(APB) register CPHY_TX_GR1

4. Added mipi timing description on local(APB) register CPHY_TX_GR4

5. Added mipi timing description on local(APB) register CPHY_TX_GR5

6. Added 0xC9

7. Added 0xCA

8. Added 0xCB

9. Added 0xCC

10. Added 0xCD

11. Added 0xCE

02-Mar-2018

1.3

1. Modified ball name of N16 from IF_SEL1 to VSS

17-Jan-2019

1.4

1. Removed all information about quad-pixel

2. Removed 0x22h and 0x32h packet type description

3. Modified power pin AVDD_CDR to AVDD

4. Corrected typo of 0xB7h register bit 6 description

5. Modified minimum horizontal porch values

6. Added note for COP usage

28-Mar-2019

1.5

1. Corrected DCS command descriptions of 0x09, 0x19, 0x29 according to the

MIPI Spec.

2. Removed the byte offset markings in VBist Mode description.

3. Added timing configuration equations for RGB input.

4. Corrected the LP clock calculation formula.

5. Rearranged section 5 functional description and section 15 application

reference.

6. Corrected the “Color Order” register description.

01-Sep-2020

SSD2832

Rev 1.5

3/178

Aug. 2020

Solomon Systech

CONTENTS

1 GENERAL DESCRIPTION ............................................................................................ 9

2 FEATURES........................................................................................................................ 9

2.1 GENERAL ................................................................................................................................................. 9

3 ORDERING INFORMATION ...................................................................................... 10

4 BLOCK DIAGRAM ....................................................................................................... 11

5 FUNCTIONAL DESCRIPTION ................................................................................... 12

5.1 RGB INTERFACE ................................................................................................................................... 12

5.2 COMMAND INTERFACE .......................................................................................................................... 12

5.2.1 SPI Interface ................................................................................................................................. 13

5.2.2 MCU Interface .............................................................................................................................. 17

5.3 DATA BUFFER ....................................................................................................................................... 25

5.4 COMMAND BUFFER ............................................................................................................................... 25

5.5 MIPI DSI-TX ........................................................................................................................................ 25

5.5.1 PHY controller .............................................................................................................................. 28

5.5.2 Contention Detection and Timer Operation ................................................................................. 28

5.6 XTAL OSC ........................................................................................................................................... 29

5.6.1 Clock Source Example .................................................................................................................. 29

5.7 PLL ....................................................................................................................................................... 30

5.8 PMU ..................................................................................................................................................... 31

5.9 PIXEL PEEK ........................................................................................................................................... 31

5.10 IMAGE FLIPPING (HORIZONTAL) ............................................................................................................ 32

6 PIN ARRAGEMENT ...................................................................................................... 33

7 POWER SUPPLY PIN ................................................................................................... 39

7.1 POWER SUPPLY PIN ............................................................................................................................... 39

7.2 MIPI PIN ............................................................................................................................................... 39

7.3 CONTROL SIGNAL PIN ........................................................................................................................... 40

7.4 INTERFACE LOGIC PIN ........................................................................................................................... 41

8 COMMAND TABLE ...................................................................................................... 43

8.1 LOCAL REGISTERS (NON-APB) DESCRIPTIONS ...................................................................................... 43

8.1.1 RGB Interface Control Register 1 ................................................................................................. 43

8.1.2 RGB Interface Control Register 2 ................................................................................................. 44

8.1.3 RGB Interface Control Register 3 ................................................................................................. 46

8.1.4 RGB Interface Control Register 4 ................................................................................................. 47

8.1.5 RGB Interface Control Register 5 ................................................................................................. 48

8.1.6 RGB Interface Control Register 6 ................................................................................................. 49

8.1.7 Configuration Register ................................................................................................................. 52

8.1.8 Virtual Channel Control Register ................................................................................................. 55

8.1.9 PLL Control Register .................................................................................................................... 56

8.1.10 PLL Configuration Register .......................................................................................................... 57

8.1.11 Clock Control Register ................................................................................................................. 58

8.1.12 Packet Size Control Register 1 ..................................................................................................... 59

8.1.13 Packet Size Control Register 2 ..................................................................................................... 61

8.1.14 Packet Size Control Register 3 ..................................................................................................... 62

8.1.15 Packet Drop Register .................................................................................................................... 63

8.1.16 Operational Control Register ....................................................................................................... 64

8.1.17 Maximum Return Size Register ..................................................................................................... 65

8.1.18 Return Data Count Register.......................................................................................................... 66

8.1.19 Acknowledge Response Status Register ........................................................................................ 67

Solomon Systech

Aug. 2020

4/178

Rev 1.5

SSD2832

8.1.20 Line Control Register.................................................................................................................... 68

8.1.21 Interrupt Control Register ............................................................................................................ 71

8.1.22 Interrupt Status Register ............................................................................................................... 74

8.1.23 Error Status Register .................................................................................................................... 78

8.1.24 Delay Adjustment Register 1 ......................................................................................................... 81

8.1.25 Delay Adjustment Register 2 ......................................................................................................... 82

8.1.26 Delay Adjustment Register 3 ......................................................................................................... 83

8.1.27 Delay Adjustment Register 4 ......................................................................................................... 84

8.1.28 Delay Adjustment Register 5 ......................................................................................................... 85

8.1.29 Delay Adjustment Register 6 ......................................................................................................... 86

8.1.30 HS TX Timer Register 1 ................................................................................................................ 87

8.1.31 HS TX Timer Register 2 ................................................................................................................ 88

8.1.32 TE Status Register ......................................................................................................................... 89

8.1.33 SPI Read Register ......................................................................................................................... 91

8.1.34 PLL Lock Register ........................................................................................................................ 92

8.1.35 Test Register ................................................................................................................................. 93

8.1.36 TE Count Register ......................................................................................................................... 95

8.1.37 Analog Control Register 1 ............................................................................................................ 96

8.1.38 RGB Interface Control Register 7 ................................................................................................. 98

8.1.39 INOUT Configuration Control Register ..................................................................................... 100

8.1.40 APB Write Register ..................................................................................................................... 102

8.1.41 APB Read Register...................................................................................................................... 103

8.2 LOCAL (APB) REGISTER DESCRIPTIONS .............................................................................................. 104

8.2.1 SCM Registers Descriptions ....................................................................................................... 105

8.2.2 CPHY Analog Front End Registers Descriptions ....................................................................... 109

8.2.3 Video BIST Register Descriptions .............................................................................................. 117

8.2.4 Pixel Peek Registers Descriptions .............................................................................................. 124

9 MAXIMUM RATING .................................................................................................. 128

10 DC OPERATION CONDICTION .............................................................................. 129

10.1 DC CHARACTERISTIC .................................................................................................................... 130

11 AC CHARACTERISTIC ............................................................................................. 131

11.1 POWER UP TIMING .............................................................................................................................. 131

11.2 RESET TIMING ................................................................................................................................... 131

11.3 INTERFACE TIMING .............................................................................................................................. 131

11.3.1 MCU Interface (Type A) Timing ................................................................................................. 131

11.3.2 MCU Interface (Type B) Timing ................................................................................................. 133

11.3.3 SPI Interface Timing ................................................................................................................... 135

11.3.4 RGB Interface Timing ................................................................................................................. 136

12 POWER UP SEQUENCE ............................................................................................ 137

13 POWER OFF SEQUENCE .......................................................................................... 138

14 MIPI CHARACTERISTIC .......................................................................................... 139

14.1 MIPI CPHY CHARACTERISTIC ...................................................................................................... 139

14.1.1 MIPI CPHY HS CHARACTERISTICS ........................................................................................ 140

14.1.2 MIPI CPHY LP CHARACTERISTICS ........................................................................................ 141

14.2 MIPI DPHY CHARACTERISTIC ..................................................................................................... 143

14.21 MIPI DPHY HS CHARACTERISTICS ........................................................................................ 145

15 APPLICATION REFERENCE ................................................................................... 148

15.1 CONTROLLING AND PROGRAMMING .................................................................................................... 148

15.1.1 Access Local (non-APB) Registers ............................................................................................. 149

15.1.2 Access Local (APB) Registers for Write ..................................................................................... 150

15.1.3 Access Local (APB) Registers for Read ...................................................................................... 152

15.2 VIDEO MODE USE CASES .................................................................................................................... 154

SSD2832

Rev 1.5

5/178

Aug. 2020

Solomon Systech

15.2.1 Interleaving Non-Video Packets with Video Packets .................................................................. 157

15.2.2 Video Bandwidth Consideration (RGB Parallel Interface) ........................................................ 157

15.3 COMMAND MODE USE CASES ............................................................................................................. 159

15.3.1 Programming Sequence .............................................................................................................. 160

15.3.2 Partition Mode ............................................................................................................................ 161

15.4 VIDEO TO COMMAND MODE................................................................................................................ 162

15.4.1 Example of switching sequence .................................................................................................. 163

15.5 MIPI PACKET CONTROL ...................................................................................................................... 163

15.5.1 Write Operation .......................................................................................................................... 164

15.5.2 Read Operation ........................................................................................................................... 165

15.5.3 Internal Buffer Status .................................................................................................................. 166

15.6 INTERRUPT OPERATION ....................................................................................................................... 168

15.7 STATE MACHINE OPERATION ............................................................................................................... 170

15.8 ACKNOWLEDGEMENT OPERATION....................................................................................................... 170

15.9 TEARING EFFECT (TE) OPERATION ..................................................................................................... 172

15.9.1 Using IO Pins ............................................................................................................................. 172

15.9.2 Using MIPI Escape Mode ........................................................................................................... 172

15.10 VIDEO BIST ........................................................................................................................................ 173

16 PACKAGE INFORMATION ...................................................................................... 177

16.1 373 BALLS TFBGA ............................................................................................................................... 177

剩余177页未读,继续阅读

资源评论

YYY141480

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功