没有合适的资源?快使用搜索试试~ 我知道了~

创龙带您解密TI、Xilinx异构多核SoC处理器核间通讯-20200327.pdf

需积分: 50 13 下载量 55 浏览量

2020-03-27

15:35:41

上传

评论

收藏 2.11MB PDF 举报

温馨提示

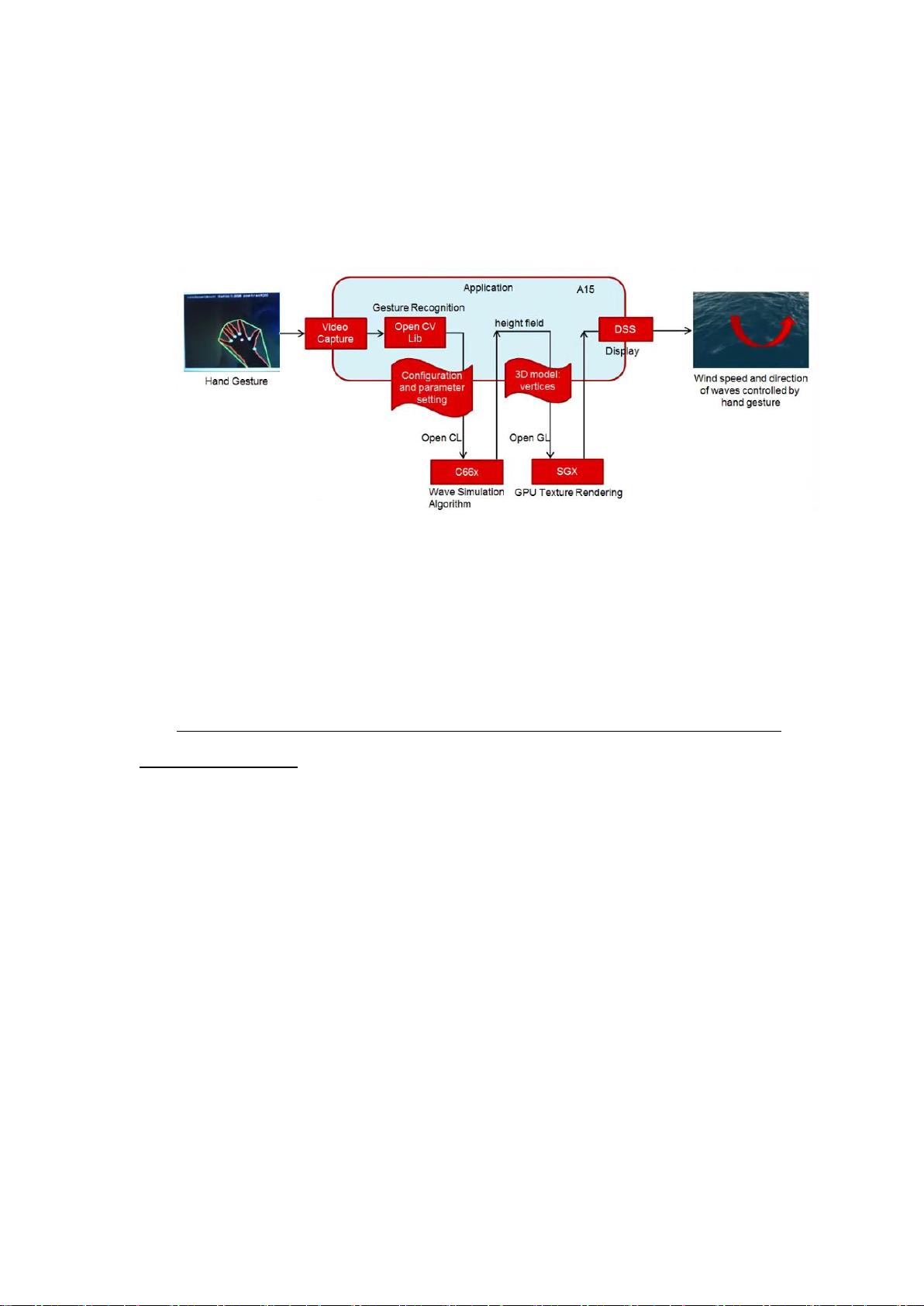

1什么是异构多核SoC处理器 顾名思义,单颗芯片内集成多个不同架构处理单元核心的SoC处理器,我们称之为异构多核SoC处理器,比如: TI的OMAP-L138(DSP C674x + ARM9)、AM5708(DSP C66x + ARM Cortex-A15)SoC处理器等; Xilinx的ZYNQ(ARM Cortex-A9 + Artix-7/Kintex-7可编程逻辑架构)SoC处理器等。

资源推荐

资源详情

资源评论

创龙带您解密 TI、Xilinx 异构多核 SoC 处理器核间通讯

1 什么是异构多核 SoC 处理器

顾名思义,单颗芯片内集成多个不同架构处理单元核心的 SoC 处理器,我们

称之为异构多核 SoC 处理器,比如:

TI 的 OMAP-L138(DSP C674x + ARM9)、AM5708(DSP C66x + ARM Cortex-

A15)SoC 处理器等;

Xilinx 的 ZYNQ(ARM Cortex-A9 + Artix-7/Kintex-7 可编程逻辑架构)So

C 处理器等。

2 异构多核 SoC 处理器有什么优势

相对于单核处理器,异构多核 SoC 处理器能带来性能、成本、功耗、尺寸等

更多的组合优势,不同架构间各司其职,各自发挥原本架构独特的优势。比如:

ARM 廉价、耗能低,擅长进行控制操作和多媒体显示;

DSP 天生为数字信号处理而生,擅长进行专用算法运算;

FPGA 擅长高速、多通道数据采集和信号传输。

同时,异构多核 SoC 处理器核间通过各种通信方式,快速进行数据的传输和共享,

可完美实现 1+1>2 的效果。

3 常见核间通信方式

要充分发挥异构多核 SoC 处理器的性能,除开半导体厂家对芯片的硬件封装

外,关键点还在于核间通信的软硬件机制设计,下面介绍几种在 TI、Xilinx 异

构多核 SoC 处理器上常见的核间通信方式。

(1) OpenCL

OpenCL(全称 Open Computing Language,开放运算语言)是第一个面向异

构系统通用目的并行编程的开放式、免费标准,也是一个统一的编程环境,便于

软件开发人员编写高效轻便的代码,而且广泛适用于多核心处理器(CPU)、图形

处理器(GPU)、Cell 类型架构以及数字信号处理器(DSP)等其他并行处理器,在

能源电力、轨道交通、工业自动化、医疗、通信、军工等应用领域都有广阔的发

展前景。

在异构多核 SoC 处理器上,OpenCL 将其中一个可编程内核视为主机,将其

他内核视为设备。在主机上运行的应用程序(即主机程序)管理设备上的代码(内

核)的执行,并且还负责使数据可用于设备。设备由一个或多个计算单元组成。

比如,在 TI AM5728 异构多核 SoC 处理器中,每个 C66x DSP 都是一个计算单元。

OpenCL 运行时,一般包含如下两个组件:

(1)主机程序创建和提交内核以供执行的 API。

(2)用于表达内核的跨平台语言。

参考开发资料:

http://downloads.ti.com/mctools/esd/docs/opencl

https://training.ti.com/sites/default/files/docs/Introduction_to_

OpenCL_slides.pdf

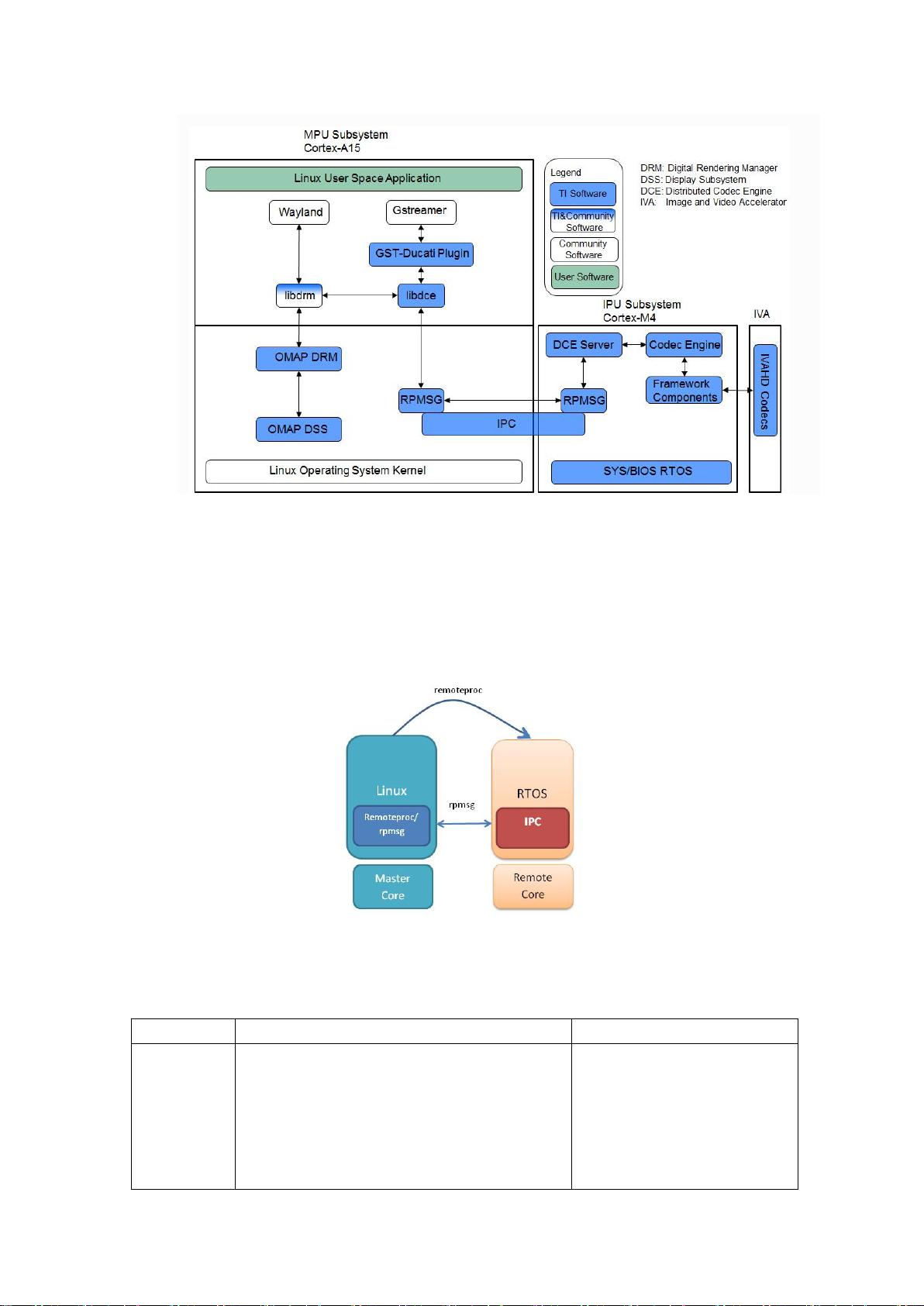

(2) DCE

DCE(Distributed Codec Engine)分布式编解码器引擎,是 TI 基于 AM57x

异构多核 SoC 处理器的视频处理框架,提供的完整 Gstreamer 插件框架。

DCE 由三部分硬件模块组成,分别为 MPU 核心、IPU2 核心以及 IVA-HD 硬件

加速器,其主要功能如下:

MPU:基于 ARM 用户空间 Gstreamer 应用,控制 libdce 模块。libdce 模块

在 ARM RPMSG 框架上实现与 IPU2 的 IPC 通信。

IPU2:构建 DCE server,基于 RPMSG 框架与 ARM 实现通信,使用编解码器

引擎和帧组件控制 IVA-HD 加速器。

IVA-HD:实现视频/图像编解码的硬件加速器。

(3) IPC

IPC(Inter-Processor Communication)是一组旨在促进进程间通信的模块。

通信包括消息传递、流和链接列表。这些模块提供的服务和功能可用于异构多核

SoC 处理器中 ARM 和 DSP 核心之间的通信。

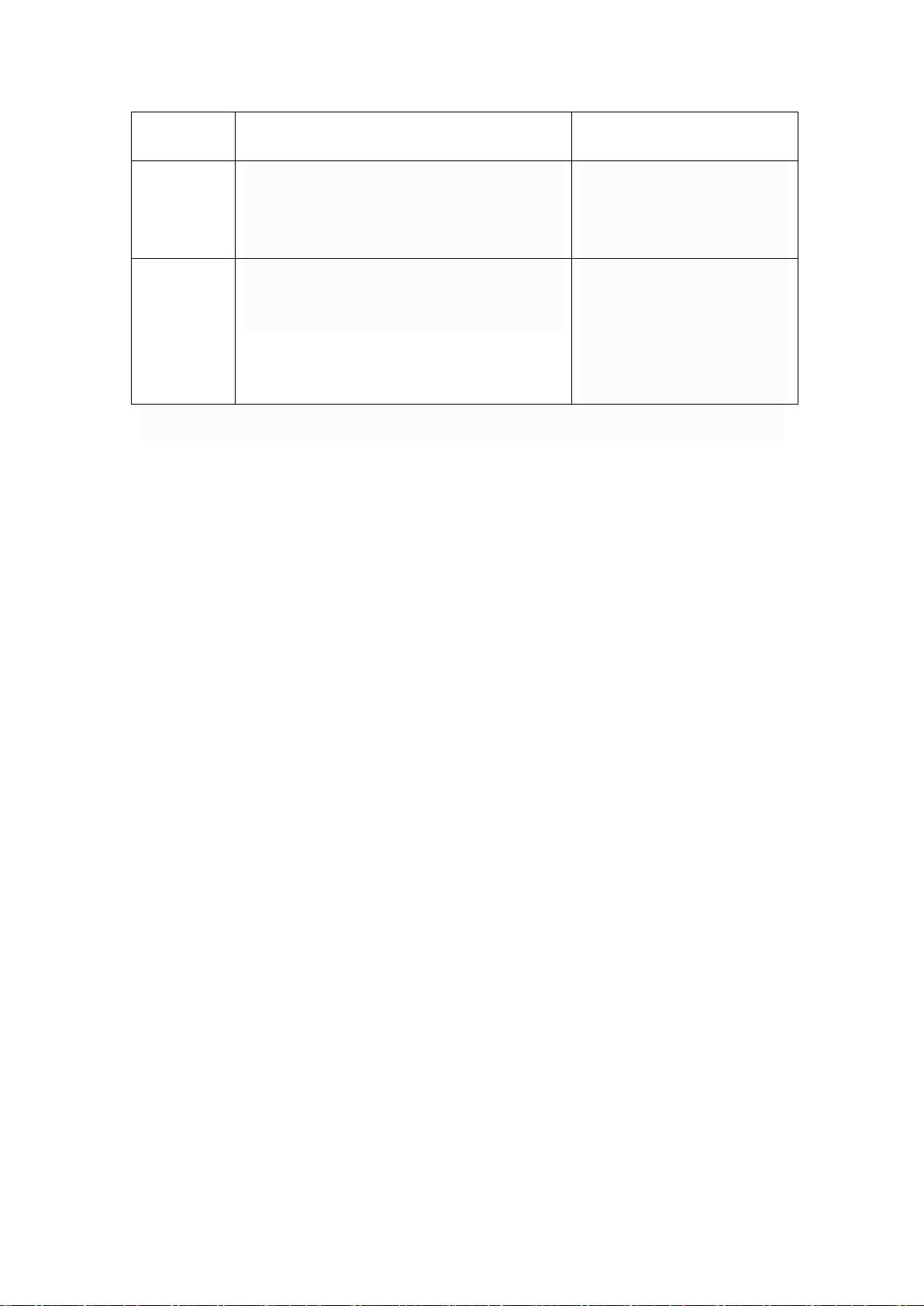

如下为 TI 异构多核 SoC 处理器常用的核间通信方式的优缺点比较:

方式

优点

缺点

OpenCL

易于在设备之间移植

无需了解内存架构

无需担心 MPAX 和 MMU

无需担心一致性

无需在 ARM 和 DSP 之间构建/配置/

使用 IPC

无法控制系统内存布

局等以处理优化的

DSP 代码

无需成为 DSP 代码、架构或优化方

面的专家

DEC

加速多媒体编解码处理

在与 Gstreamer 和 TI Gstreamer 插

件连接时简化多媒体应用程序的开

发

不适合非编解码算法

需要努力添加新的编

解码算法

需要 DSP 编程知识

IPC

完全控制 DSP 配置

能够进行 DSP 代码优化

在多个 TI 平台上支持相同的 API

需要了解内存架构

需要了解 DSP 配置和

编程

仅限于小型消息(小于

512 字节)

TI 专有 API

(4) AXI

AXI(Advanced eXtensible Interface)是由 ARM 公司提出的一种总线协议,

Xilinx 从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4 版本。

剩余21页未读,继续阅读

资源评论

Tronlong_

- 粉丝: 285

- 资源: 166

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 1732669747878.jpg

- 8613985ec49eb8f757ae6439e879bb2a_holmes_logindex

- 使用Spring Boot处理大文件上传有哪些技巧?

- GRE隧道是Openwrt系统的常用功能之一,在两台Openwrt设备之间建立GRE隧道,可通过两台设备在公网上建立一个虚拟局域网

- 机器学习领域中的Iris数据集探索与分析技术解析及建模流程

- 本科毕业设计-Java Web学院的实验课选课及实验室管理系统.zip

- MySQL在Linux安装和集群搭建-一主一备

- Python中检查文件是否存在的几种方法

- 02b97e6de561b351e3db753f4abedc7b.rar

- java JDK11版本安装包

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功