电子设计自动化实验

——基于 STEP-CYC10 开发板

第 1 章 实验-----------------------------------------------------------------1

第 2 章 附图(STEP-CYC10 部分电路图)---------------------------------------7

第 3 章 STEP-CYC10 信号名与芯片引脚编号对照表---------------------------------9

附录 1 实验中用到的代码------------------ ----- ---- ----------- -- ------- 11

2020.2

- 1 -

第 1 章 实验

1. 基本电路设计

(1) 实验目的:熟悉 Quartus Prime 的 VHDL文本设计流程全过程,学习简单组合电路、时序电路的设计、仿真和硬

件测试。

(2) 实验内容

➢ 学习 Quartus Prime 的使用方法

按照课件(1.8、ALTERA 开发工具 Quartus Prime lite)给出的步骤,熟悉并掌握 Quartus Prime 的基本使用方法。

➢ 组合电路的设计

首先利用 Quartus Prime 完成 4 选 1 多路选择器(例 1)的文本编辑输入(mux41.vhd)和编译、综合、仿真测试等步骤,

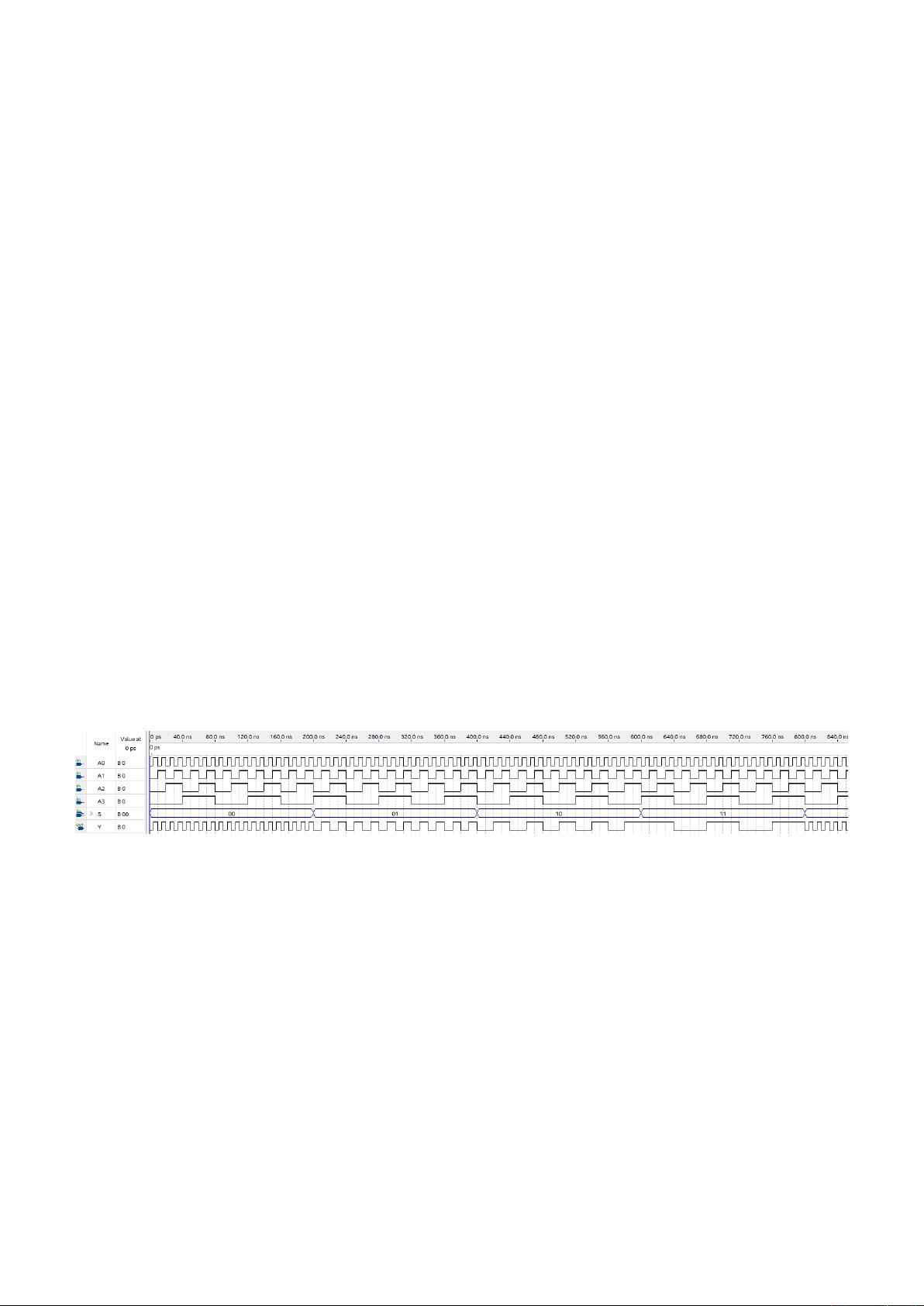

给出图 1 所示的仿真波形。

【例 1】

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX41 IS

PORT(A0,A1,A2,A3 : IN STD_LOGIC;

S : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

Y : OUT STD_LOGIC);

END MUX41;

ARCHITECTURE DATAFLOW OF MUX41 IS

BEGIN

Y<=A0 WHEN S="00" ELSE

A1 WHEN S="01" ELSE

A2 WHEN S="10" ELSE

A3;

END DATAFLOW;

图1 mux41功能时序波形

➢ 时序电路的设计

根据组合电路的设计的步骤和要求,设计触发器(例 2)。

【例 2】

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DFF1 IS

PORT ( CLK : IN STD_LOGIC ;

D : IN STD_LOGIC ;

Q : OUT STD_LOGIC );

END ;

ARCHITECTURE BHV OF DFF1 IS

SIGNAL Q1 : STD_LOGIC ; --类似于在芯片内部定义一个数据的暂存节点

BEGIN

PROCESS (CLK,D)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN

Q1 <= D ;

END IF;

END PROCESS ;

- 2 -

Q <= Q1 ; --将内部的暂存数据向端口输出

END BHV;

(3) 实验报告:根据以上的实验内容写出实验报告,包括实验目的、实验原理、实验程序;给出程序分析报告、RTL

电路图、仿真波形图(截图打印,贴在试验报告上)及其分析报告。

(4) 附加内容:设计 1 位全加器。首先用Quartus Prime 完成教材 3.2 和 3.4.1 小节(第 4 版 3.1.4 和 3.1.4 小节)

给出的半加器和全加器的设计、编译及综合;其次,对半加器及全加器进行波形仿真,验证设计的正确性。

2. 8 段数码显示译码器设计

(1) 实验目的:学习计数器及 8 段数码显示译码器的设计、仿真和硬件测试;进一步熟悉 VHDL 设计技术。

(2) 实验内容

➢ 设计含异步清 0 和同步时钟使能的十进制加法计数器电路

实验程序见例 3,设计流程参考实验 1。

【例 3】

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT ( CLK,RST,EN : IN STD_LOGIC;

CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : OUT STD_LOGIC );

END CNT10;

ARCHITECTURE BEHAV OF CNT10 IS

BEGIN

PROCESS(CLK, RST, EN)

VARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);

VARIABLE CO : STD_LOGIC;

BEGIN

IF RST = '0' THEN CQI := (OTHERS => '0') ; --( )

ELSIF CLK'EVENT AND CLK='1' THEN --( )

IF EN = '1' THEN --( )

IF CQI < 9 THEN --( )

CQI := CQI + 1;

ELSE --( )

CQI := (OTHERS => '0');

END IF;

END IF;

END IF;

IF CQI = 9 THEN --( )

CO := '1';

ELSE

CO := '0';

END IF;

CQ <= NOT CQI; COUT <= NOT CO; --为什么取反输出?

END PROCESS;

END BEHAV;

针对以上例程完成以下步骤。

⚫ 在 Quartus Prime 上对上例进行编辑、编译、综合、适配、仿真。说明例中各语句的作用(填入括号内),详细

描述示例的功能特点,给出其所有信号的时序仿真波形(截图打印,贴在试验报告上)。

⚫ 由于 STEP CYC10 的 CLK(CLK_12M、CLK_50M)的频率过高,无法直接使用,需通过分频电路接入,分

频电路代码见附录 1(使用输入频率 12MHz,即接入信号 CLK_12M)。

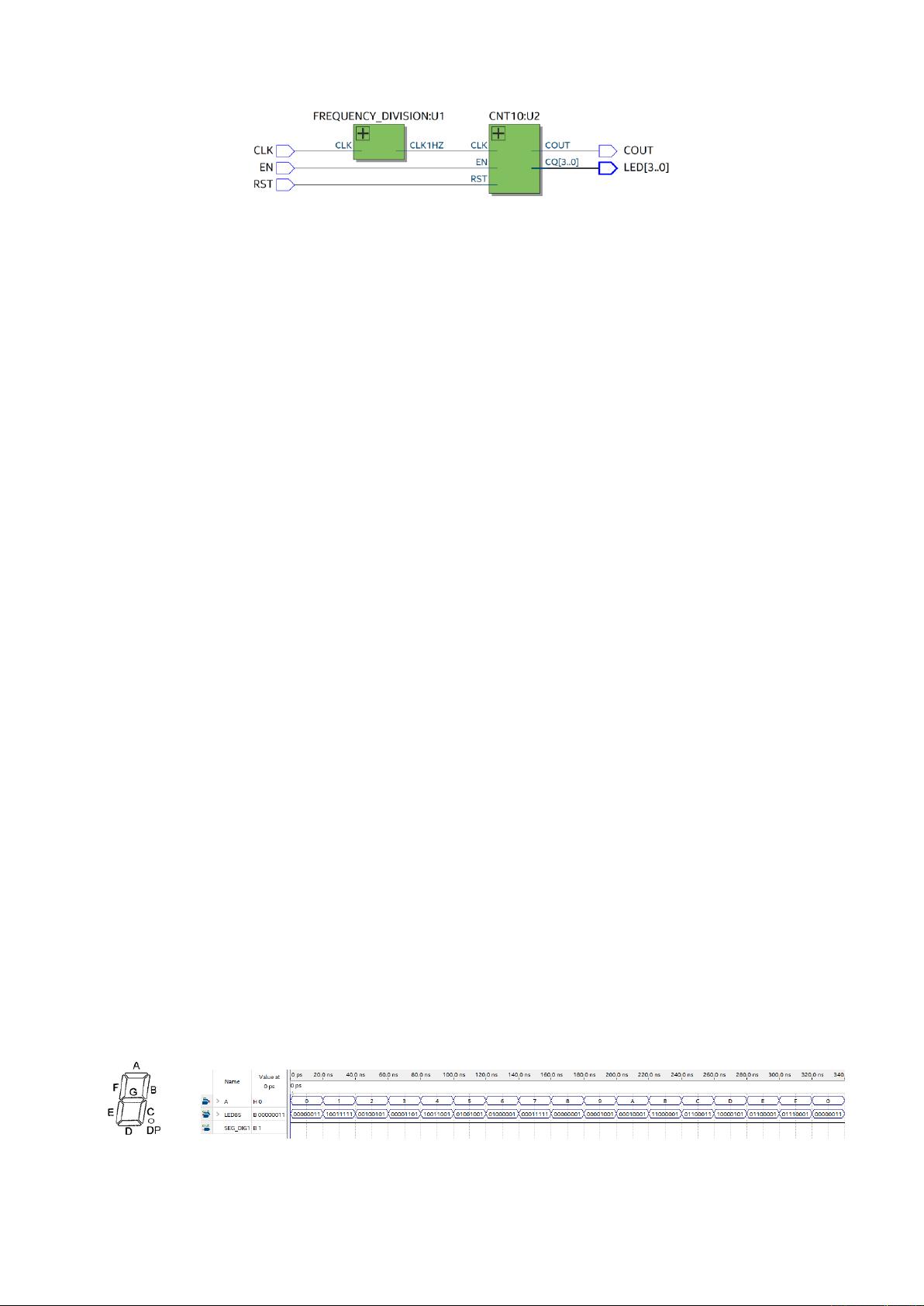

⚫ 引脚锁定以及硬件下载测试。引脚锁定后进行编译、下载和硬件测试实验。按图 2 的方式连接成顶层设计电路

(用 VHDL 表述),图中的分频电路代码见附录 1,CNT10 即例 3 所示的 10 进制加法计数器(可将此 10 进制

计数器改成 16 进制计数器)。建议选择 STEP CYC10 系统的如下引脚配置:CLK 接 CLK_12M,EN 接拨码开

关 SW1~SW8 其中之一,RST 接五向开关(5D 摇杆)KEY_L 、KEY_R、KEY_C、KEY_U、KEY_D 其中

之一(例如中键 KEY_C),COUT 接发光二极管 LED1,LED[3..0]接发光二极管 LED2~LED5。将实验过程和

实验结果写进实验报告。

- 3 -

图 2 分频器与计数器连接电路的顶层文件原理图

(3) 思考题:在上例中是否可以不定义信号 CQI,而直接用输出端口信号完成加法运算,即:

CQ <= CQ + 1?为什么?

➢ 设计 8 段数码显示译码器电路

实验原理:8 段数码管是纯组合电路,通常的小规模专用 IC,如 74 系列或 4000 系列的器件只能作十进制 BCD 码

译码,然而数字系统中的数据处理和运算都是 2 进制的,所以输出表达都是 16 进制的,为了满足 16 进制数的译码显示,

最方便的方法就是利用译码程序在 FPGA/CPLD 中来实现。例 4 作为 8 段译码器,输出信号 LED8S 的 8 位分别接数码

管的 8 个段,见图 3 所示。例如当 LED8S 输出为“01001001”时,数码管的 8 个段:A、B、C、D、E、F、G、H(DP)

分别接 0、1、0、0、1、0、0、1;接有 0(低电平)的段发亮(即数码管是共阳极设计),于是数码管显示“5”。

【例 4】

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DECL8S IS

PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SEG_DIG1 : OUT STD_LOGIC;

LED8S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)) ;

END ;

ARCHITECTURE ONE OF DECL8S IS --板子上的数码管为共阳极

BEGIN

SEG_DIG1 <= '1';

PROCESS( A )

BEGIN

CASE A IS -- "ABCDEFGH"

WHEN "0000" => LED8S <= "00000011" ;--0

WHEN "0001" => LED8S <= "10011111" ;--1

WHEN "0010" => LED8S <= "00100101" ;--2

WHEN "0011" => LED8S <= "00001101" ;--3

WHEN "0100" => LED8S <= "10011001" ;--4

WHEN "0101" => LED8S <= "01001001" ;--5

WHEN "0110" => LED8S <= "01000001" ;--6

WHEN "0111" => LED8S <= "00011111" ;--7

WHEN "1000" => LED8S <= "00000001" ;--8

WHEN "1001" => LED8S <= "00001001" ;--9

WHEN "1010" => LED8S <= "00010001" ;--A

WHEN "1011" => LED8S <= "11000001" ;--B

WHEN "1100" => LED8S <= "01100011" ;--C

WHEN "1101" => LED8S <= "10000101" ;--D

WHEN "1110" => LED8S <= "01100001" ;--E

WHEN "1111" => LED8S <= "01110001" ;--F

WHEN OTHERS => NULL ;

END CASE ;

END PROCESS ;

END ;

针对以上例程完成以下步骤。

⚫ 在 Quartus Prime 上对该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。提示:用输

入总线的方式给出输入信号仿真数据,仿真波形如图 4 所示。

图 3 数码管结构 图4 8 段译码器仿真波形

⚫ 引脚锁定及硬件测试。建议选择 STEP CYC10 系统的如下引脚配置:A[3..0]接 SW1~SW8 中的连续的 4 个( 例