《模拟 COMS 集成电路设计_作业 2》

课程名称

模拟 COMS 集成电路设计

姓 名

学 号

学 院

电子与通信工程学院

专 业

21 级电子信息

任课教师

教师评阅意见:

作业成绩

评阅日期

作业提交时间:2022 年 6 月 6 日

目录

1 预期目标:................................................................................................................................. 3

2 设计原理及流程:..................................................................................................................... 3

3 ADS 设计仿真步骤: ................................................................................................................ 4

3.1 晶体管的 DC 仿真以及参数设计 .................................................................................. 4

3.1.1 N 型晶体管的参数测量设计 ............................................................................... 4

3.1.2 设计 N 型晶体管宽长以及 m .............................................................................. 5

3.1.3 P 型晶体管的参数测量设计 ............................................................................... 6

3.1.4 设计 P 型晶体管宽长以及 m .............................................................................. 7

3.2 放大器半边电路仿真设计.............................................................................................. 8

3.3 放大器整个电路仿真设计............................................................................................ 10

3.4 考虑衬底偏置效应以及 AC 仿真 ................................................................................ 14

3.4.1 考虑衬底偏置效应的放大器电路优化设计..................................................... 14

3.4.2 考虑衬底偏置效应的放大器 AC 仿真 ............................................................. 17

4 总结........................................................................................................................................... 18

运算放大器的设计及 ADS 仿真设计—作业 2

1 预期目标:

1) 差动输出摆幅=1.6V

2) 功耗=3.6mW

3) 电压增益=500

4) 电源电压=1.8V

2 设计原理及流程:

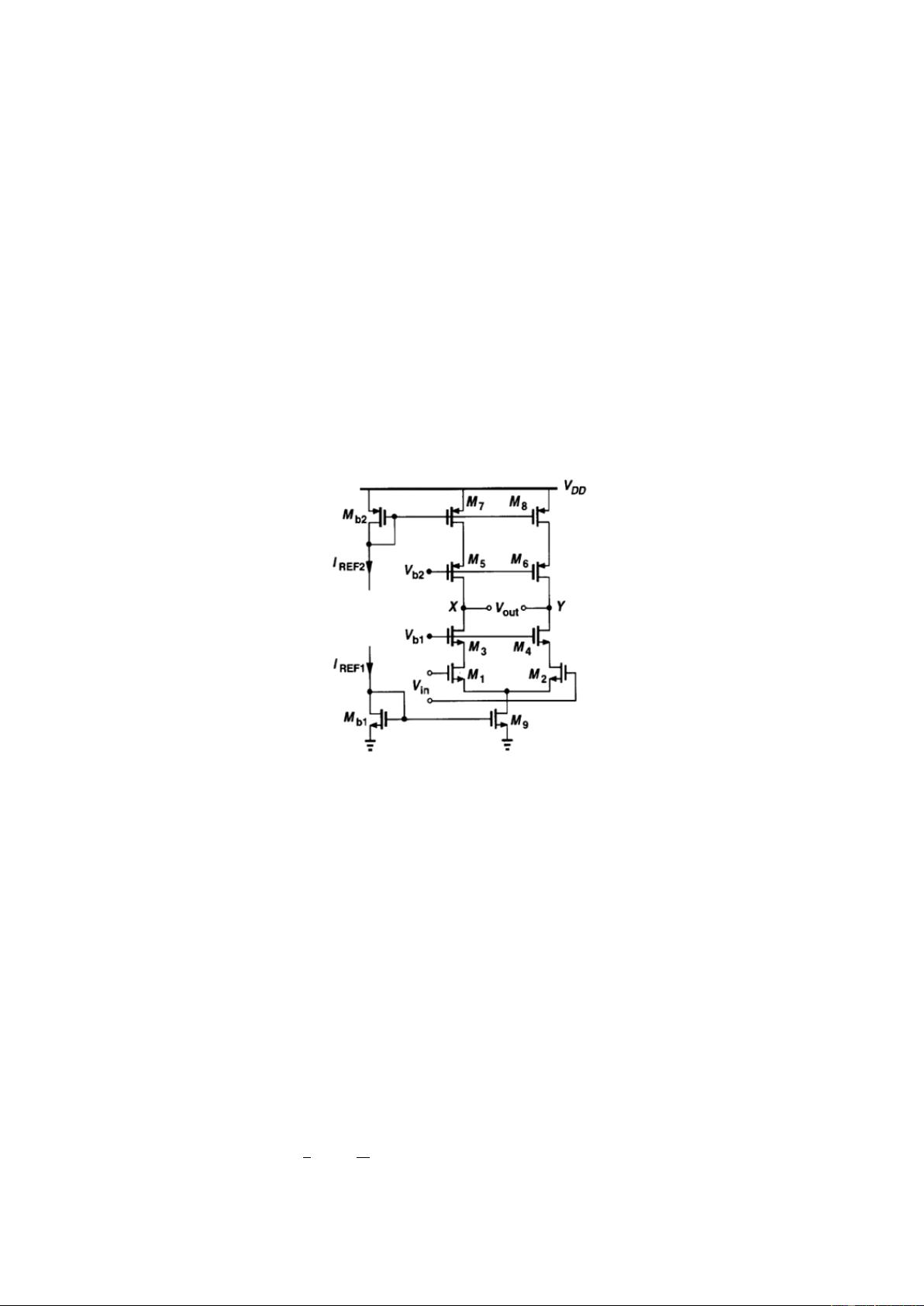

设计原理图如下图所示:

图 2-1 设计原理图

参数计算

1) 偏置电流:最大功耗为最大功耗=3.6mW,电源电压=1.8V,由 I=P/U,可得偏置电流

=2mA;

2) 电源分配:每个 cascode 支路分配 0.95mA(差动放大器的两个支路电流之和为 1.9 mA),

剩下的 0.1mA 分配给偏置电路;

3) 过驱动电压分配:5 个晶体管的过驱动电压的和=1V(VDD-1/2 最大电压摆幅);理论

上流过 M9 电流大,因此分配的 VOD9 应该大一点,但是为了简单起见,初步设计将 5 个晶

体管的过驱动电压都设成一样,即分配的方式为:

VOD9=0.2V;

VOD1=0.2V;VOD3=0.2V;VOD5=0.2V;VOD7=0.2V。

4) 理论上是依据I

D

=

1

2

μCox

W

L

(V

GS

−V

TH

)

2

,计算各管的尺寸。但是由于工艺不一样,

需要预先给定 VTH 、Cox、μ才能进行计算,如果给定一个不知道任何参数的晶体管,一般

来说通过仿真来确定其参数。下面通过仿真计算 VTH 以及各管的尺寸。

3 ADS 设计仿真步骤:

3.1 晶体管的 DC 仿真以及参数设计

3.1.1 N 型晶体管的参数测量设计

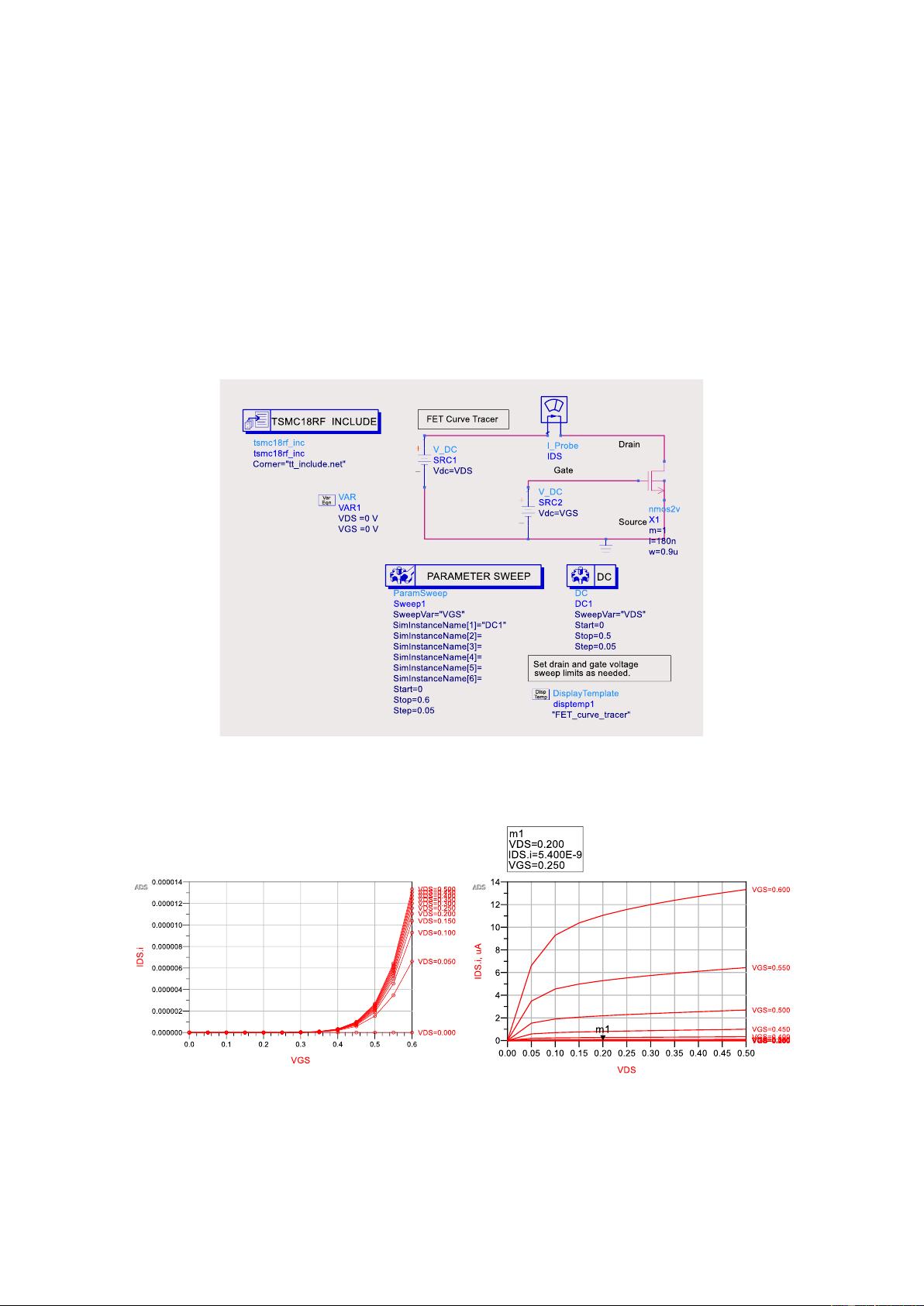

插入 FET_curve_tracer DC 测试模型,放置 nmos2v 晶体管以及模型到电路图中,按如图

所示连接原理图,并修改管子参数和 DC 动态范围。

图 3-1 N 型晶体管 DC 仿真原理图 1

仿真结果如下图所示:

图 3-2 NMOS 晶体管的 DC 仿真参数设计结果 1

从图中可以看到 V

th,n

=0.25V,此时晶体管开始导通,开始有电流通过。

将 IDS.i*1000,放置一个点在 VGS=0.5V,VDS=0.2V 的位置,选择 VGS 为 0.5V,所以

Vth=0.25V,VGS=0.5V。添加方程式,观测 Wr 的比值如图所示,可以看到 Wr 为 391.93。

图 3-3 NMOS 晶体管的 DC 仿真参数设计结果 2

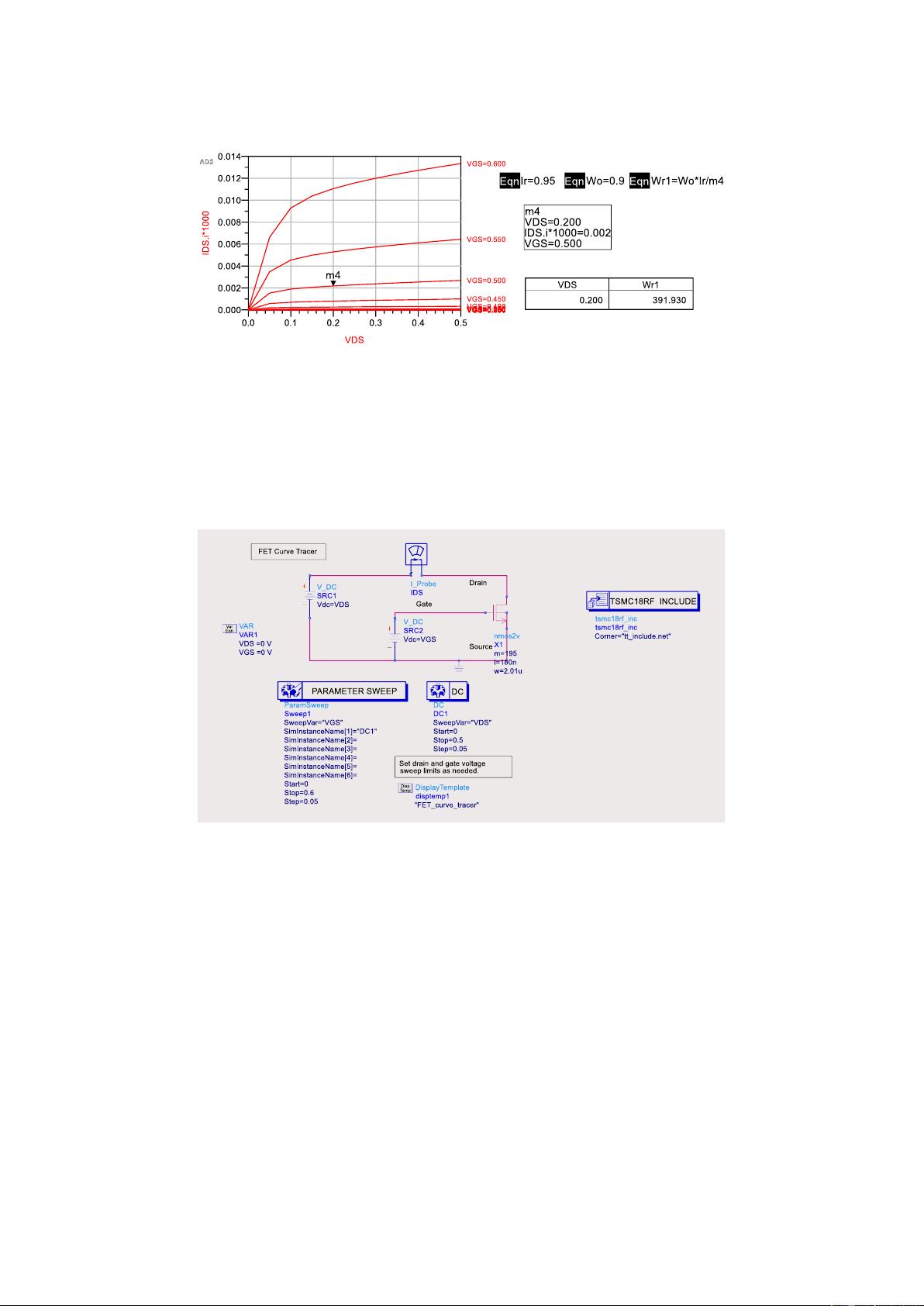

3.1.2 设计 N 型晶体管宽长以及 m

设计宽长以及 m(表示并联相同晶体管的个数),使得电流为 0.95mA。

由于电流 I 与 W , m 成正比,与 L 成 反 比 。 现 在 使 得 L 不变,m=195 ,则

W=391.93/195=2.01,修改参数如下图所示。

图 3-4 N 型晶体管 DC 仿真原理图 2

进行仿真后,得到以下结果,放置 m1 点在 VDS=0.2,VGS=0.5 的位置,发现电流为

1.115mA 比预期的 0.95mA 要大,这是由于晶体管的内部结构以及其他因素的影响,继续修

改 W 与 m 使得 I=0.95。

评论0