TPS56C215 3.8V 至 17V 输入、12A 同步降压 SWIFT™ 转换器

1 特性

• 集成式 13.5mΩ 和 4.5mΩ MOSFET

• 支持 12A 持续 I

OUT

• 4.5V 启动(没有 5.0V 外部偏置)

• 整个温度范围内的基准电压为 0.6V ±1%

• 0.6V 至 5.5V 输出电压范围

• 支持陶瓷输出电容器

• D-CAP3

™

控制模式,用于快速瞬态响应

• 可选强制持续导通模式 (FCCM),用于实现窄输出

电压纹波,或自动跳跃 Eco-Mode,用于实现高轻

负载效率

• 400kHz、800kHz 和 1.2MHz 的可选 F

SW

• 单调启动至预偏置输出

• 具有断续重启功能的两个可调节电流限制设置

• 可选 5V 外部偏置,可提升效率

• 可调节软启动,默认软启动时间为 1ms

• –40°C 至 150°C 的工作结温范围

• 小型 3.5mm x 3.5mm HotRod

™

QFN 封装

• 在 WEBENCH

®

设计工具中受支持

2 应用

• 服务器、云计算、存储

• 电信和网络、负载点 (POL)

• IPC、工厂自动化、PLC、测试测量

• 高端 DTV

3 说明

TPS56C215 是 TI 旗下最小的一款单片 12A 同步降压

转换器,具有自适应导通时间 D-CAP3 控制模式。该

器件集成了低 R

DS

(on) 功率 MOSFET,简单易用且高

效,只需极少的外部组件,适合空间受限的电源系统。

具有竞争力的特性包括非常精确的基准电压、快速负载

瞬态响应、自动跳跃模式运行以实现轻负载效率、可调

节的电流限制和无需外部补偿。强制持续导通模式有助

于满足高性能 DSP 和 FPGA 的严格电压调节精度要

求。TPS56C215 采用热增强型 18 引脚 HotRod QFN

封装,并且设计为在 -40°C 至 150°C 的结温范围内运

行。

器件信息

器件型号

封装

(1)

封装尺寸(标称值)

TPS56C215 VQFN (18) 3.5mm x 3.5mm

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

录。

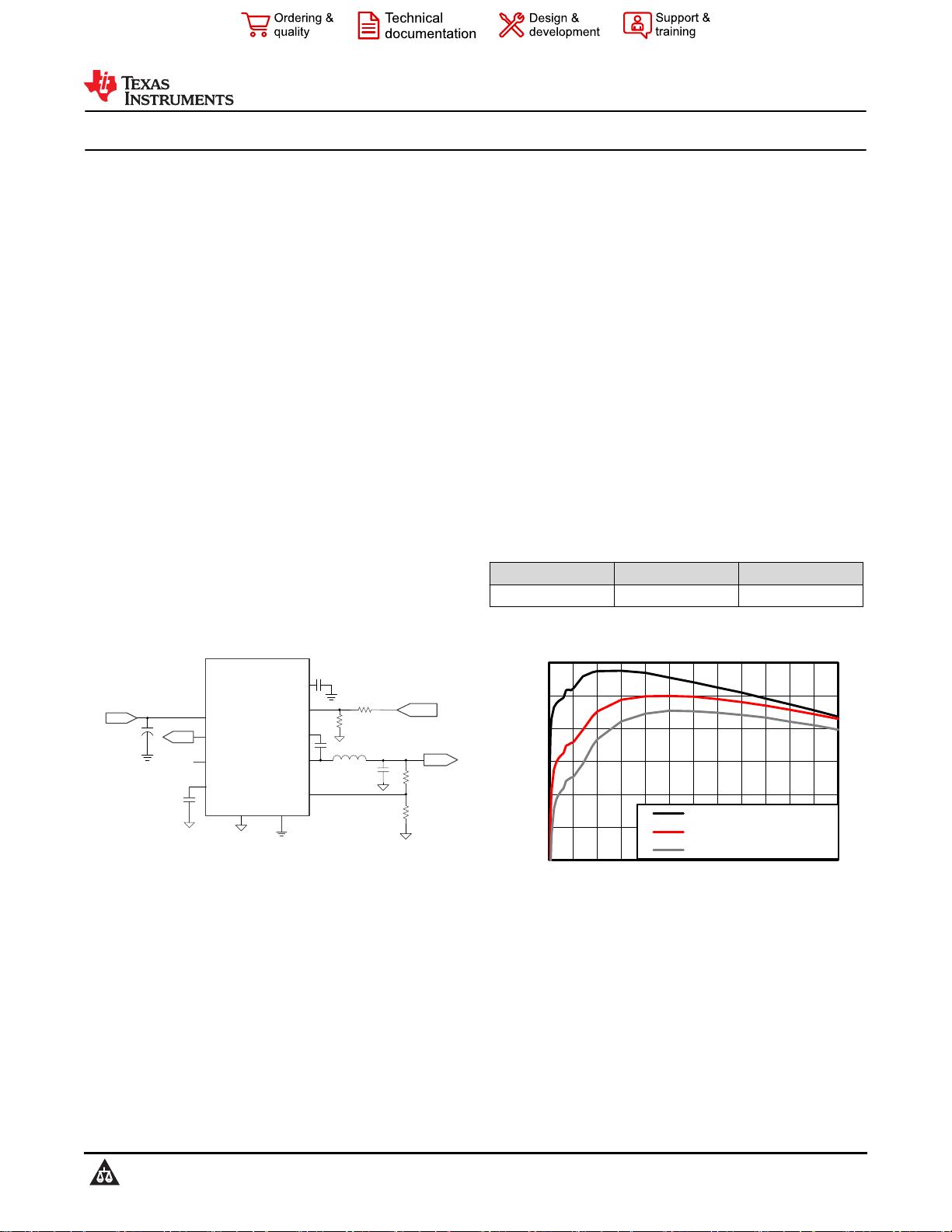

PGNDAGND

FB

SW

BOOT

MODE

VREG5

PGOOD

SS

VIN

EN

TPS56C215

V

IN

V

OUT

VREG5

PGOOD

R

M_H

R

M_L

C

SS

R

UPPER

R

LOWER

L

OUT

C

OUT

C

IN

典型应用

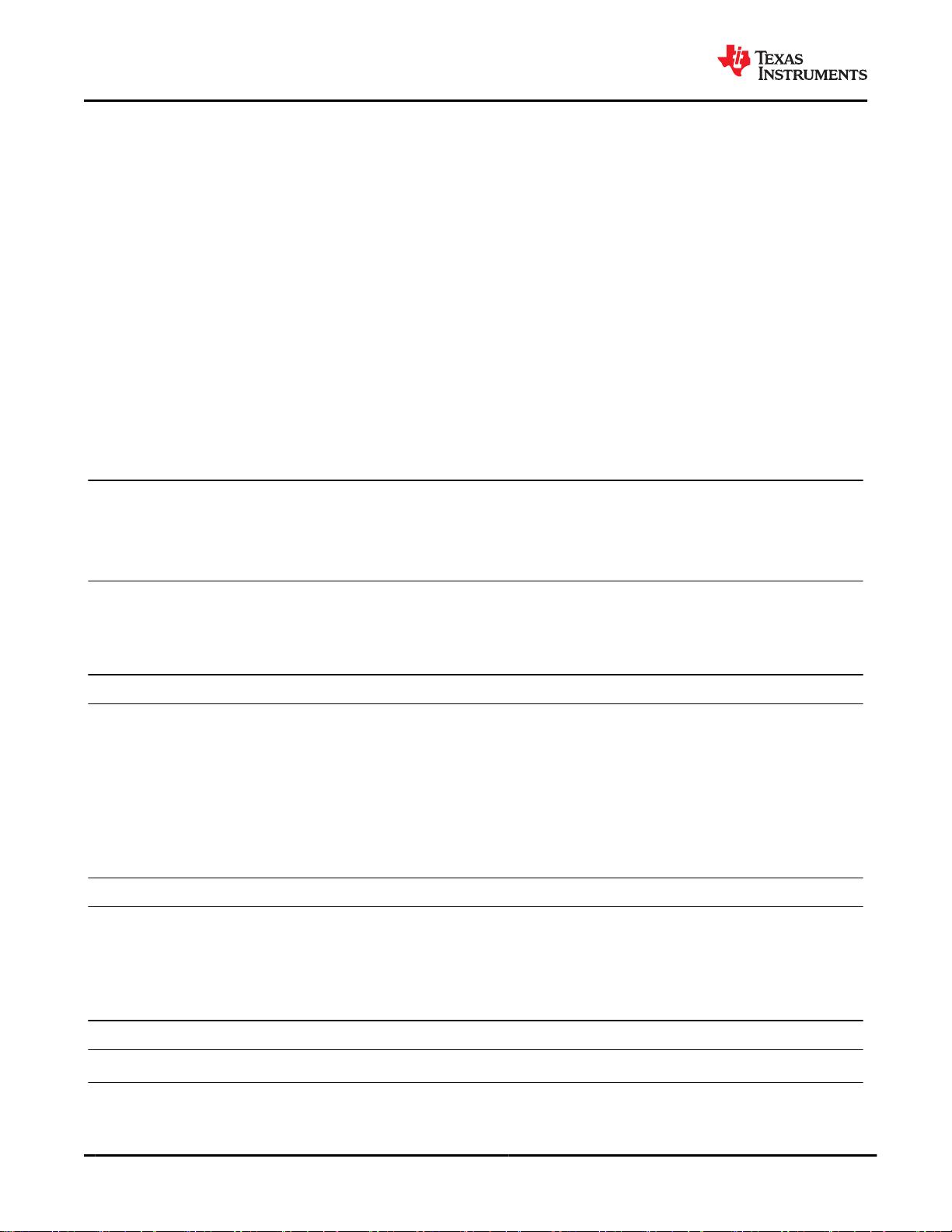

65

70

75

80

85

90

95

0 1 2 3 4 5 6 7 8 9 10 11 12

Efficiency(%)

Output Current(A)

V =4.5V,V =1.2V,400kHz

V =12V, V =1.2V, 400kHz

V =17V, V =1.2V, 400kHz

C001

IN

OUT

IN

OUT

OUT

IN

效率与输出电流间的关系

TPS56C215

ZHCSEU8D – MARCH 2016 – REVISED FEBRUARY 2021

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。有关适用的官方英文版本的最新信息,请访问

www.ti.com,其内容始终优先。TI 不保证翻译的准确性和有效性。在实际设计之前,请务必参考最新版本的英文版本。

English Data Sheet: SLVSD05

Table of Contents

1 特性................................................................................... 1

2 应用................................................................................... 1

3 说明................................................................................... 1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................3

6 Specifications.................................................................. 4

6.1 Absolute Maximum Ratings........................................ 4

6.2 ESD Ratings............................................................... 4

6.3 Recommended Operating Conditions.........................4

6.4 Thermal Information....................................................5

6.5 Electrical Characteristics.............................................5

6.6 Timing Requirements.................................................. 6

6.7 Typical Characteristics................................................ 7

7 Detailed Description......................................................12

7.1 Overview................................................................... 12

7.2 Functional Block Diagram......................................... 13

7.3 Feature Description...................................................13

7.4 Device Functional Modes..........................................19

8 Application and Implementation.................................. 20

8.1 Application Information............................................. 20

8.2 Typical Application.................................................... 20

9 Power Supply Recommendations................................25

10 Layout...........................................................................26

10.1 Layout Guidelines................................................... 26

10.2 Layout Example...................................................... 26

11 Device and Documentation Support..........................29

11.1 Device Support........................................................29

11.2 接收文档更新通知................................................... 30

11.3 支持资源..................................................................30

11.4 Trademarks............................................................. 30

11.5 静电放电警告...........................................................30

11.6 术语表..................................................................... 30

12 Mechanical, Packaging, and Orderable

Information.................................................................... 31

12.1 Package Marking.................................................... 31

4 Revision History

注:以前版本的页码可能与当前版本的页码不同

Changes from Revision C (November 2017) to Revision D (February 2021) Page

• 更新了整个文档的表、图和交叉参考的编号格式。.............................................................................................1

• 更正了整个文档中的拼写和语法错误.................................................................................................................. 1

• Added V

IN

-SW, V

IN

-SW, and BOOT –SW (10-ns transient)..............................................................................4

• Changed SW (10-ns transient) min value from -3 V to -5 V............................................................................... 4

Changes from Revision B (July 2016) to Revision C (November 2017) Page

• 添加了特性项“4.5V 启动(没有 5.0V 外部偏置)”......................................................................................... 1

• 添加了特性项“4.5V 启动(没有 5.0V 外部偏置)”......................................................................................... 1

• 更改了 典型应用 图像中的 VREG5 引脚处的接地符号。....................................................................................1

• Changed from "5% resistors" to "1% resistors" in the 节 7.3.4 description ......................................................15

• Changed Power-Up Sequence image for 图 7-2.............................................................................................. 15

• Changed Adjustable VIN Undervoltage Lock Out image for 图 7-3. ................................................................17

• Added I

h

term to 方程式 5 Definition List ......................................................................................................... 17

• Added 节 12.1 information................................................................................................................................ 31

Changes from Revision A (March 2016) to Revision B (May 2016) Page

• 将

节

1 从“支持 14A 持续 I

OUT

”更改为“支持 12A 持续 I

OUT

”......................................................................1

• 向典型应用原理图添加了组件名称......................................................................................................................1

• Deleted I

OCL

spec for "ILIM+1 option, Valley Current" condition.........................................................................5

• Changed From: "...up to 14 A" To: "...up to 12 A" in first sentence of

节

7.1.................................................... 12

• Deleted four rows in Mode Pin Resistor Settings table for I

OUT

of 14 A........................................................... 15

Changes from Revision * (March 2016) to Revision A (March 2016) Page

• 添加了完整量产数据表的内容............................................................................................................................. 1

TPS56C215

ZHCSEU8D – MARCH 2016 – REVISED FEBRUARY 2021

www.ti.com.cn

2 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS56C215

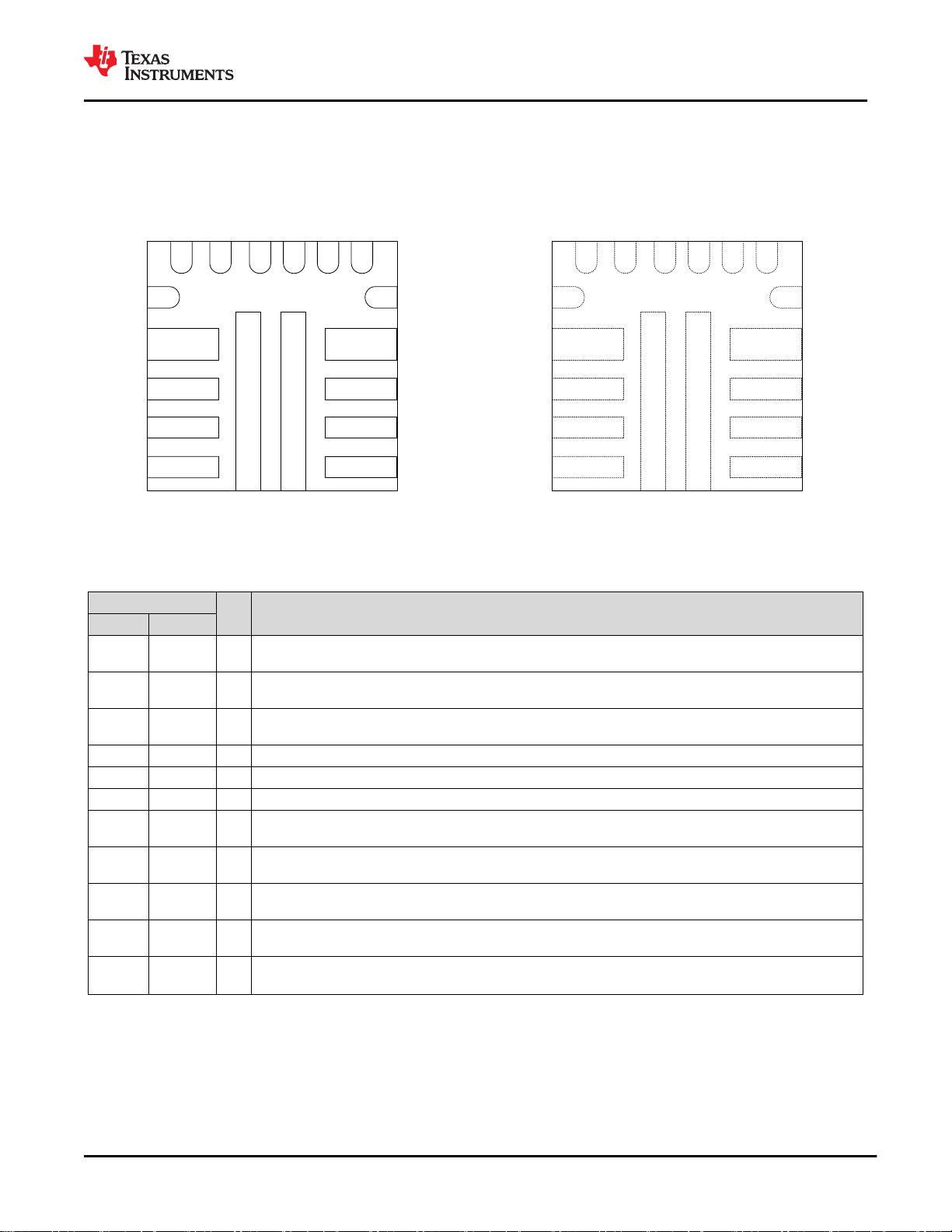

5 Pin Configuration and Functions

1 BOOT

2 VIN

3 PGND

4 PGND

5 PGND

AGND 12

VIN 11

PGND 10

PGND 9

PGND 8

13 FB

14 SS

15 EN

16 PGOOD

17 VREG5

18 MODE

BOTTOM VIEW TOP VIEW

BOOT 1

VIN 2

PGND 3

PGND 4

PGND 5

12 AGND

11 VIN

10 PGND

9 PGND

8 PGND

13 FB

14 SS

15 EN

16 PGOOD

17 VREG5

18 MODE

7 6

SW

7 6

SW

图 5-1. RNN Package 18-Pin VQFN

表 5-1. Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

BOOT 1 I

Supply input for the gate drive voltage of the high-side MOSFET. Connect the bootstrap capacitor between

BOOT and SW.

VIN 2,11 P

Input voltage supply pin for the control circuitry. Connect the input decoupling capacitors between VIN and

PGND.

PGND

3, 4, 5,

8, 9, 10

G Power GND terminal for the controller circuit and the internal circuitry. Connect to AGND with a short trace.

SW 6, 7 O Switch node terminal. Connect the output inductor to this pin.

AGND 12 G Ground of internal analog circuitry. Connect AGND to PGND plane with a short trace.

FB 13 I Converter feedback input. Connect to the center tap of the resistor divider between output voltage and AGND.

SS 14 O

Soft-Start time selection pin. Connecting an external capacitor sets the soft-start time and if no external

capacitor is connected, the converter starts up in 1 ms.

EN 15 I

Enable input control, leaving this pin floating enables the converter. It can also be used to adjust the input

UVLO by connecting to the center tap of the resistor divider between VIN and EN.

PGOOD 16 O

Open-drain power good indicator, it is asserted low if output voltage is out of PGOOD threshold, overvoltage,

or if the device is under thermal shutdown, EN shutdown or during soft start.

VREG5 17 I/O

4.7-V internal LDO output which can also be driven externally with a 5-V input. This pin supplies voltage to the

internal circuitry and gate driver. Bypass this pin with a 4.7-µF capacitor.

MODE 18 I

Switching frequency, current limit selection and light load operation mode selection pin. Connect this pin to a

resistor divider from VREG5 and AGND for different MODE options shown in 表 7-3.

www.ti.com.cn

TPS56C215

ZHCSEU8D – MARCH 2016 – REVISED FEBRUARY 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

3

Product Folder Links: TPS56C215

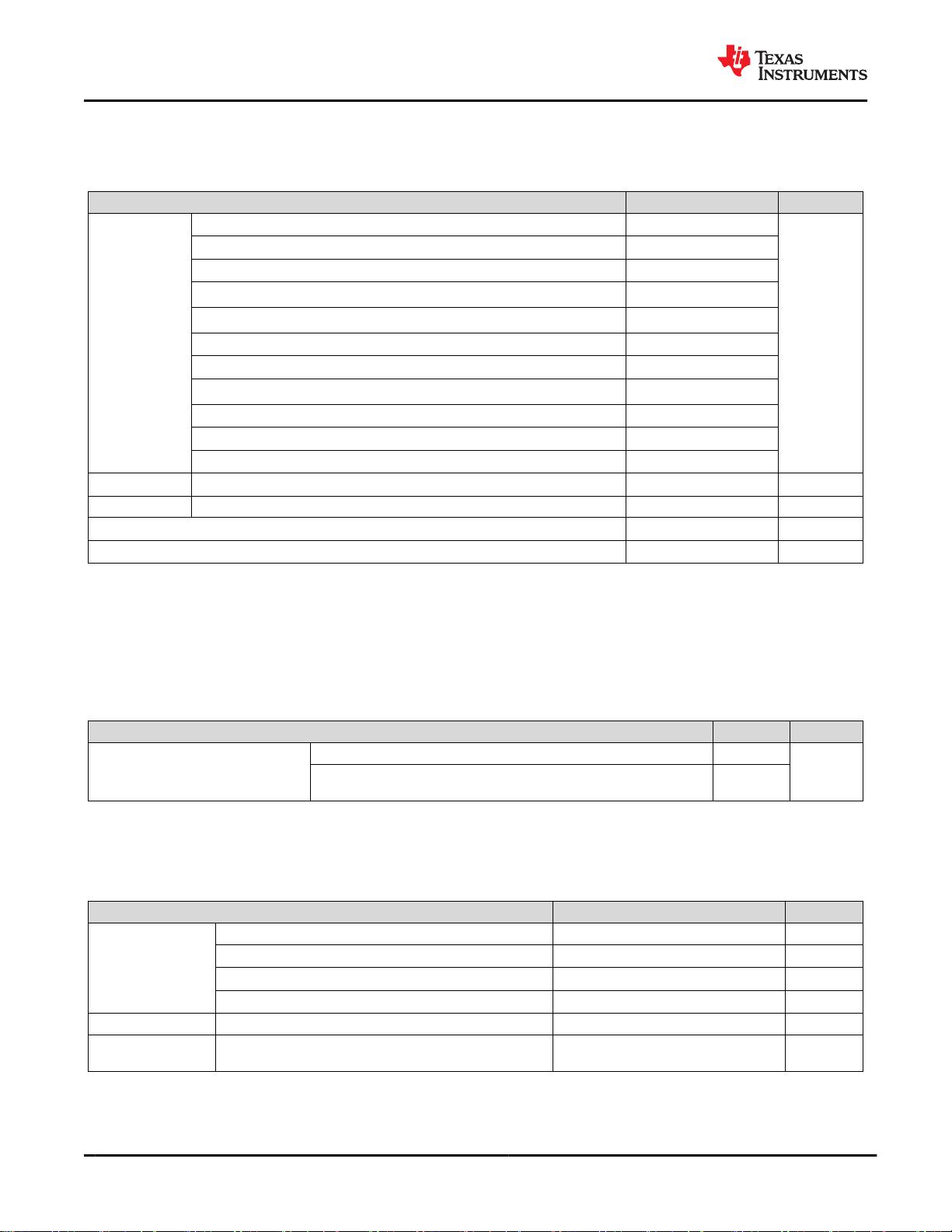

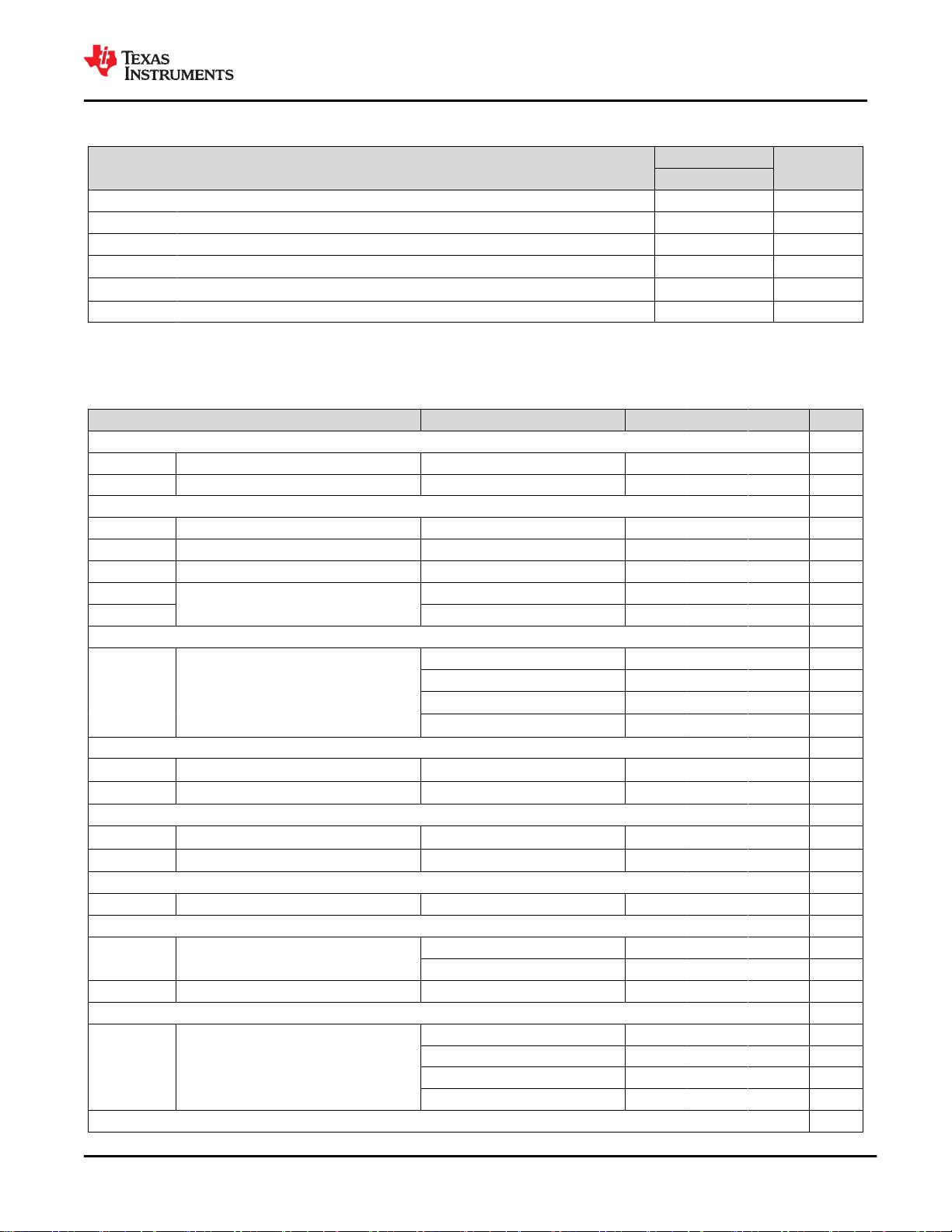

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

MIN MAX UNIT

Input Voltage

V

IN

–0.3

20

V

SW

–2

19

SW (10-ns transient)

–5

25

V

IN

-SW 22

V

IN

-SW (10-ns transient) 25

EN

–0.3

6.5

BOOT –SW –0.3

6.5

BOOT –SW (10 ns transient) –0.3

7.5

BOOT

–0.3

25.5

SS, MODE, FB

–0.3

6.5

VREG5

–0.3

6

Output Voltage PGOOD

–0.3

6.5 V

Output Current

(2)

I

OUT

14 A

T

J

Operating junction temperature

–40

150 °C

T

stg

Storage temperature

–55

150 °C

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under

Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

(2) In order to be consistent with the TI reliability requirement of 100k Power-On-Hours at 105°C junction temperature, the output current

should not exceed 14A continuously under 100% duty operation as to prevent electromigration failure in the solder. Higher junction

temperature or longer power-on hours are achievable at lower than 14A continuos output current.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

±2000

V

Charged-device model (CDM), per JEDEC specification JESD22-

C101

(2)

±500

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

Input Voltage

V

IN

3.8 17 V

SW

–1.8

17 V

BOOT

–0.1

23.5 V

VREG5

–0.1

5.2 V

Output Current I

LOAD

0 12 A

Operating junction

temperature

T

J

-40 150 °C

TPS56C215

ZHCSEU8D – MARCH 2016 – REVISED FEBRUARY 2021

www.ti.com.cn

4 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: TPS56C215

6.4 Thermal Information

THERMAL METRIC

(1)

RNN PACKAGE

UNIT

18 PINS

R

θJA

Junction-to-ambient thermal resistance 29.5 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 17.0 °C/W

R

θJB

Junction-to-board thermal resistance 8.6 °C/W

ψ

JT

Junction-to-top characterization parameter 0.4 °C/W

ψ

JB

Junction-to-board characterization parameter 8.6 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance 0.5 °C/W

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

6.5 Electrical Characteristics

T

J

= –40°C to 150°C, V

IN

=12V (unless otherwise noted)

PARAMETER CONDITIONS MIN TYP MAX UNIT

SUPPLY CURRENT

I

IN

VIN supply current T

J

= 25°C, V

EN

=5 V, non switching 600 700 µA

I

VINSDN

VIN shutdown current T

J

= 25°C, V

EN

=0 V 7 µA

LOGIC THRESHOLD

V

ENH

EN H-level threshold voltage 1.175 1.225 1.3 V

V

ENL

EN L-level threshold voltage 1.025 1.104 1.15 V

V

ENHYS

0.121 V

I

ENp1

EN pull-up current

V

EN

= 1.0 V 0.35 1.91 2.95 µA

I

ENp2

V

EN

= 1.3 V 3 4.197 5.5 µA

FEEDBACK VOLTAGE

V

FB

FB voltage

T

J

= 25°C 598 600 602 mV

T

J

= 0°C to 85°C 597.5 600 602.5 mV

T

J

= –40°C to 85°C

594 600 602.5 mV

T

J

= –40°C to 150°C

594 600 606 mV

LDO VOLTAGE

VREG5 LDO Output voltage

T

J

= –40°C to 150°C

4.58 4.7 4.83 V

ILIM5 LDO Output Current limit

T

J

= –40°C to 150°C

100 150 200 mA

MOSFET

R

DS(on)H

High side switch resistance T

J

= 25°C, V

VREG5

= 4.7 V 13.5

mΩ

R

DS(on)L

Low side switch resistance T

J

= 25°C, V

VREG5

= 4.7 V 4.5

mΩ

SOFT START

I

ss

Soft start charge current T

J

= -40°C to 150°C 4.9 6 7.1 µA

CURRENT LIMIT

I

OCL

Current Limit (Low side sourcing)

ILIM-1 option, Valley Current 9.775 11.5 13.225 A

ILIM option, Valley Current 11.73 13.8 15.87 A

Current Limit (Low side negative) Valley Current 4 A

POWER GOOD

V

PGOODTH

PGOOD threshold

V

FB

falling (fault) 84%

V

FB

rising (good) 93%

V

FB

rising (fault) 116%

V

FB

falling (good) 107%

OUTPUT UNDERVOLTAGE AND OVERVOLTAGE PROTECTION

www.ti.com.cn

TPS56C215

ZHCSEU8D – MARCH 2016 – REVISED FEBRUARY 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

5

Product Folder Links: TPS56C215