Verilog 冒泡排序.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

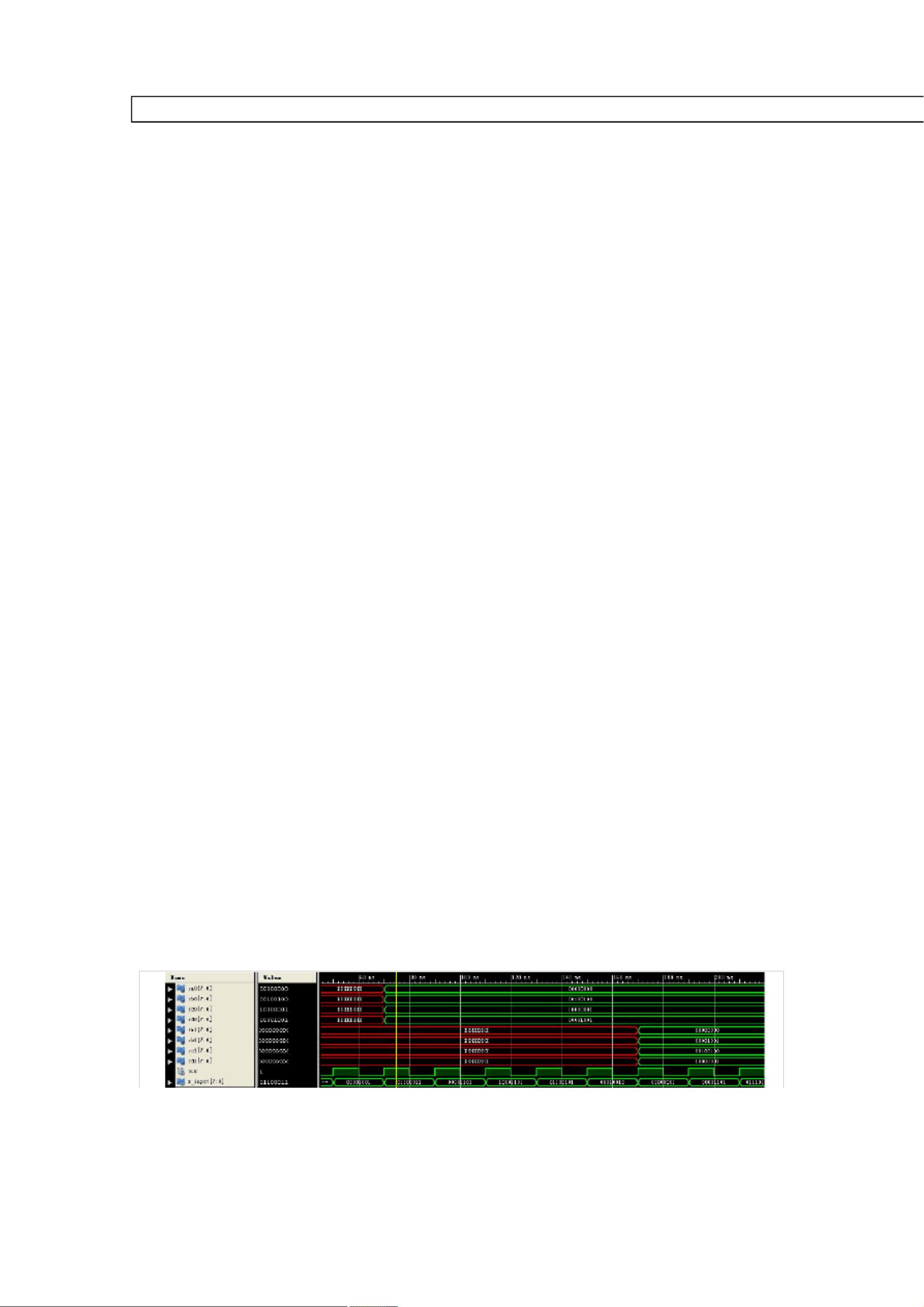

【冒泡排序】是一种简单的排序算法,通过重复遍历待排序的数据序列,比较相邻元素的大小,如果顺序错误则交换,直到所有元素均有序。在Verilog中实现冒泡排序,主要是利用硬件描述语言来构建逻辑电路,实现数据的排序功能。 在本实验中,设计了一个名为`Rank`的Verilog模块,它接受四个8位2进制输入数据,并通过时钟触发的任务执行法进行冒泡排序。模块包含一个内部状态机,用于控制排序过程的各个步骤。时钟边沿检测器(`posedge clk`)触发状态机的更新,确保在每个时钟周期内完成一次数据交换操作。 状态机的实现通常包括一个状态寄存器(`state`)和一个基于当前状态的条件语句(`casex`或`casez`)。在这个例子中,状态机有多个状态,如`IDLE0`到`IDLE3`,以及`A`、`B`、`C`、`D`和`E`,每个状态代表排序过程的一个阶段。例如,`IDLE`状态可能是等待新数据输入,而`A`、`B`、`C`、`D`和`E`可能代表不同的数据比较和交换操作。 `sort2`是一个任务,用于实现两个8位数据的比较和交换。如果输入数据`x`大于`y`,则将它们交换。任务的使用使得代码更易于阅读和理解,同时也便于复用。 在测试代码中,使用了一个时钟信号生成器(`always #10 clk=~clk`)模拟时钟的上升沿,并通过`$random`函数生成随机的8位输入数据。`Test`模块实例化了`Rank`模块(`uut`),并将输入和输出连接起来。仿真波形可以用于验证模块是否正确实现了冒泡排序功能。 这个实验旨在帮助学生掌握以下Verilog编程技能: 1. 在模块设计中使用任务(Task)。 2. 在电平敏感列表的`always`块中使用拼接操作、任务和阻塞赋值。 3. 利用有限状态机实现时序逻辑分析。 4. 编写可综合的有限状态机的标准模板。 5. 掌握状态机模块的测试方法。 通过这个实验,学生可以深入理解Verilog语言的特性,以及如何将其应用于实际的数字系统设计中,特别是涉及顺序处理和数据排序的场景。

剩余12页未读,继续阅读

wcwfl2024-10-30资源内容详细全面,与描述一致,对我很有用,有一定的使用价值。

wcwfl2024-10-30资源内容详细全面,与描述一致,对我很有用,有一定的使用价值。

- 粉丝: 6874

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于Spring Boot框架的博客系统.zip

- (源码)基于Spring Boot框架的博客管理系统.zip

- (源码)基于ESP8266和Blynk的IR设备控制系统.zip

- (源码)基于Java和JSP的校园论坛系统.zip

- (源码)基于ROS Kinetic框架的AGV激光雷达导航与SLAM系统.zip

- (源码)基于PythonDjango框架的资产管理系统.zip

- (源码)基于计算机系统原理与Arduino技术的学习平台.zip

- (源码)基于SSM框架的大学消息通知系统服务端.zip

- (源码)基于Java Servlet的学生信息管理系统.zip

- (源码)基于Qt和AVR的FestosMechatronics系统终端.zip

信息提交成功

信息提交成功