没有合适的资源?快使用搜索试试~ 我知道了~

多核系统的高性能并行故障仿真

0 下载量 35 浏览量

2024-02-03

16:52:27

上传

评论

收藏 400KB PDF 举报

温馨提示

试读

5页

多核系统的高性能并行故障仿真

资源推荐

资源详情

资源评论

High-Performance Parallel Fault Simulation for

Multi-Core Systems

Masoomeh Karami

∗

, Mohammad-hashem Haghbayan

∗

, Masoumeh Ebrahimi

†

, Hamid Nejatollahi

‡

,

Hannu Tenhunen

†

, and Juha Plosila

∗

∗

Department of Future Technologies, University of Turku, Turku, Finland.

†

Department of Electronics and Embedded Systems, Royal Institute of Technology (KTH), Kista, Sweden.

‡

University of California, Irvine, CA USA.

Emails:

∗

{mkaram, mohhag, juplos}@utu.fi

†

{mebr,hannu}@kth.se

‡

hnejatol@uci.edu

Abstract—Fault simulation is a time-consuming process that

requires customized methods and techniques to accelerate it.

Multi-threading and Multi-core approaches are two promising

techniques that can be exploited to accelerate the fault simulation

process by using different parts of the hardware at the same

time. However, an efficient parallelization is obtained only by the

refinement of software with respect to the hardware platform. In

this paper, a parallel multi-thread fault simulation technique is

proposed to accelerate the simulation process on multi-core plat-

forms. In this approach, the gate input values are independently

assigned to each thread. Each input value carries the information

of several parallel simulation processes. This provides a multi-

thread parallel fault simulation environment. The experimental

results show that the proposed technique can efficiently use

the hardware platform. In a single-core platform, the proposed

technique can reduce the time by 25% while in a dual-core

increasing the thread approximately halves the execution time.

Index Terms—Multi-core system, multi-threading, paralleliza-

tion, fault simulation

I. INTRODUCTION

Fault simulation (FS) plays an essential role in different

fields, such as test pattern generation, built-in-self-test, con-

trollability, and observability analysis [1], [2]. This process is

a challenging and time-consuming task in the VLSI design.

In FS, a circuit-under-test (CUT) is simulated for a given

fault model and a set of test patterns. This process is often

computationally intensive, particularly for modern systems that

require a large number of test patterns.

One of the most popular fault models for VLSI circuits is

the stuck-at fault model [2]. Several works have used parallel

and concurrent FS approaches to minimize the FS execution

time for the stuck-at fault model in single-core [2], [3] and

multi-core processors [4], [5]. They also use different methods

such as mixed-level fault simulation, parallelization, and event-

driven to accelerate the FS process. Mixed-level FS is an ap-

proach where non-faulty parts of a circuit are simulated faster

using a higher abstraction level, e.g., behavioral level [6]. As

FS has parallelizable characteristics, parallel processing has

been widely used for minimizing the execution time. One

parallelization technique is to partition the circuit into mutually

exclusive parts and simulate them in parallel [7], [8]. Other

parallelization solutions are based on simulating the circuit

in parallel for different sets of faults (data-parallel) or test

patterns (pattern-parallel) [9], [10].

There are two methods for implementing gate-level fault

simulation: time-driven FS and event-driven FS. In the time-

driven FS, the simulator calculates and updates all the gates’

input/output variables in each small time epoch. In the event-

driven FS, the gates’ input/output variables are calculated

based on the new occurred event, e.g., a change in the wire

value. The event-driven method is more efficient compared to

the time-driven method by being faster, using less memory,

and being more flexible [11], [12].

In this paper, a parallel event-driven FS technique is pro-

posed for multi-core systems to minimize the FS time. We

describe the entire process from fault injection to scheduling

tasks for parallel computing on different cores. The proposed

technique is based on parallel processing of the occurred

events in each level of the netlist.

II. PARALLEL EVENT-DRIVEN FAULT SIMULATION

In this section, we investigate two separate techniques to

reduce the fault-simulation (FS) time, i.e., parallel FS [4],

[5] and event-driven FS [13], [14], [11]. The considered fault

model in this paper is stuck-at-0 (S@0) or stuck-at-1 (S@1)

[2]. In a simple FS technique, after generating faults and

eliminating the overlapping faults, i.e., fault collapsing [2],

[15], faults are injected into the design. Then, the output of

the design is compared with the expected value, i.e., golden

output. If the output is the same as the golden output, it means

the fault is not propagated to the output, and thus it is masked.

Otherwise, it is said that the injected fault is observed and

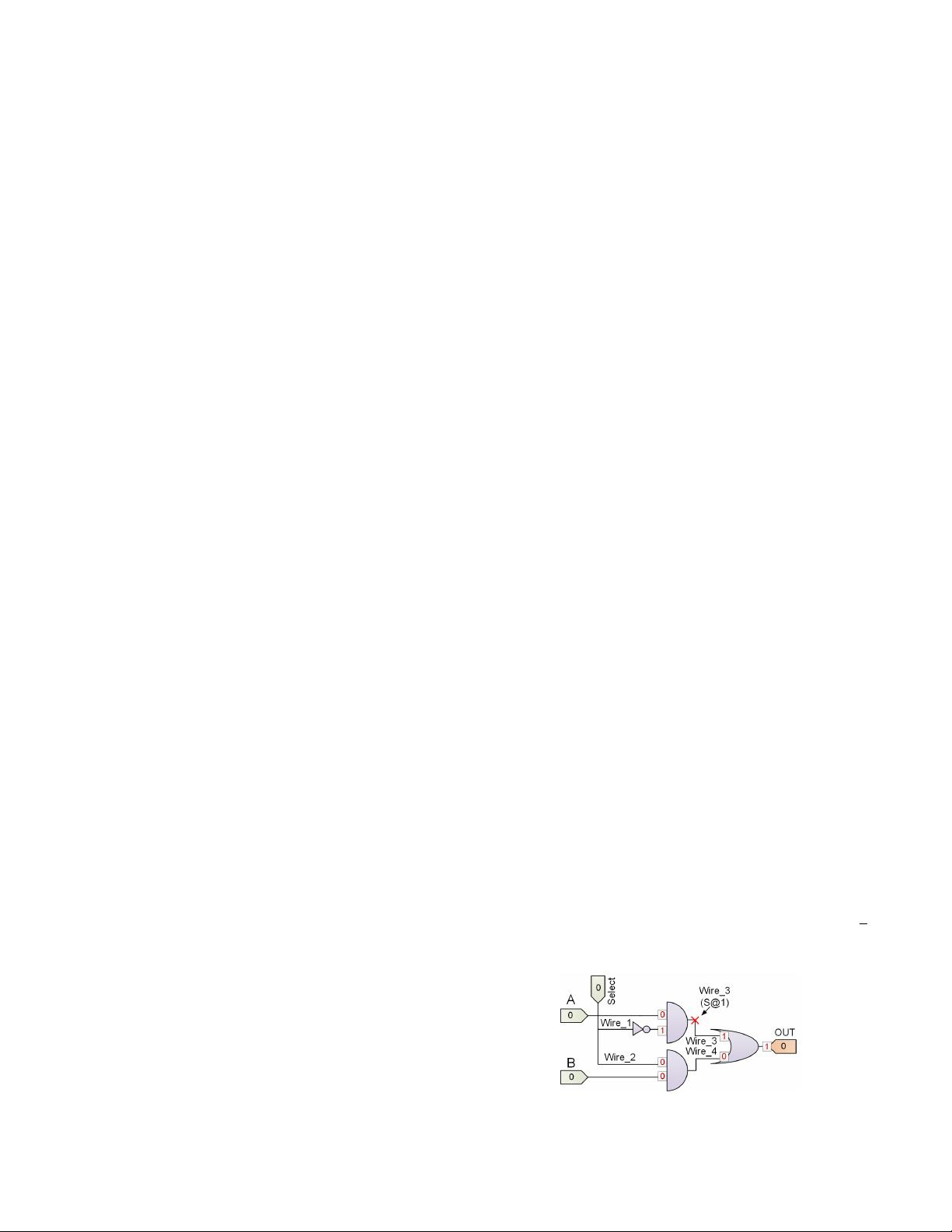

detected. For example, Figure 1 shows a 1-bit multiplexer

where the output should be 0 when the signals {A, B, and

SELECT } are {000}. However, the S@1 fault on wire 3

results in OUT =1, which is different from the golden result,

and thus a fault is detected.

Fig. 1: An example of stuck-at FS in a 1-bit multiplier

资源评论

F87523399332578_

- 粉丝: 386

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功