RAZAVI AND WOOLEY: DESIGN TECHNIQUES FOR HIGH-SPEED, HIGH-RESOLUTION COMPARATORS

1917

vi,

(b)

Fig.

1.

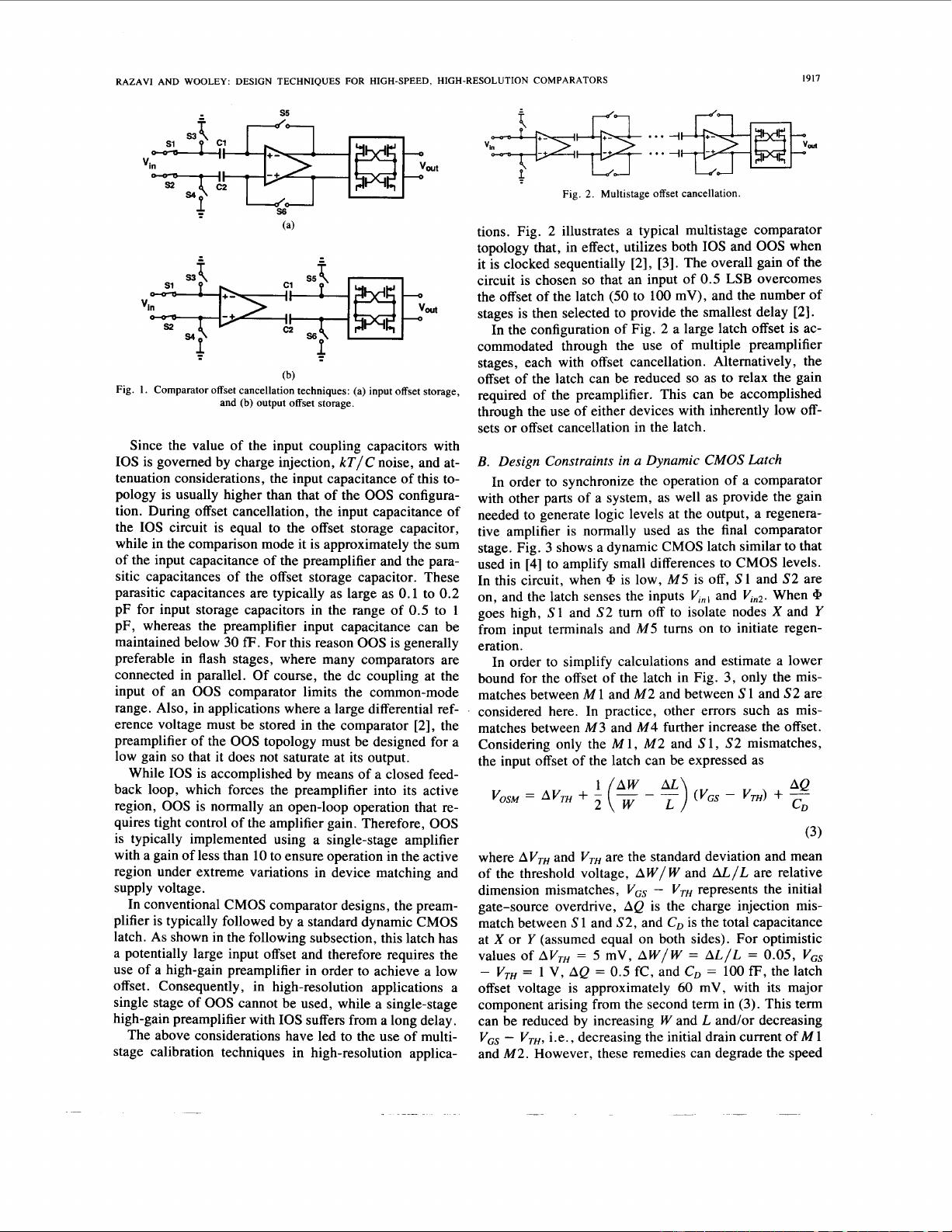

Comparator offset cancellation techniques: (a) input offset storage,

and

(b)

output offset storage.

Since the value of the input coupling capacitors with

10s

is governed by charge injection,

kT/C

noise, and at-

tenuation considerations, the input capacitance of this to-

pology is usually higher than that of the

00s

configura-

tion. During offset cancellation, the input capacitance of

the

10s

circuit is equal to the offset storage capacitor,

while in the comparison mode it is approximately the sum

of the input capacitance of the preamplifier and the para-

sitic capacitances of the offset storage capacitor. These

parasitic capacitances are typically as large as

0.1

to

0.2

pF for input storage capacitors in the range of

0.5

to

1

pF, whereas the preamplifier input capacitance can be

maintained below

30

fF.

For this reason

00s

is generally

preferable in flash stages, where many comparators are

connected in parallel.

Of

course, the dc coupling at the

input of an

00s

comparator limits the common-mode

range. Also, in applications where a large differential ref-

erence voltage must be stored in the comparator

[2],

the

preamplifier of the

00s

topology must be designed for a

low gain

so

that it does not saturate at its output.

While

10s

is accomplished by means of a closed feed-

back loop, which forces the preamplifier into its active

region,

00s

is normally an open-loop operation that re-

quires tight control of the amplifier gain. Therefore,

00s

is typically implemented using a single-stage amplifier

with a gain of less than

10

to ensure operation in the active

region under extreme variations in device matching and

supply voltage.

In conventional CMOS comparator designs, the pream-

plifier is typically followed by a standard dynamic CMOS

latch. As shown in the following subsection, this latch has

a potentially large input offset and therefore requires the

use of a high-gain preamplifier in order to achieve a low

offset. Consequently, in high-resolution applications a

single stage of

00s

cannot be used, while a single-stage

high-gain preamplifier with

10s

suffers from a long delay.

The above considerations have led to the use of multi-

stage calibration techniques in high-resolution applica-

T

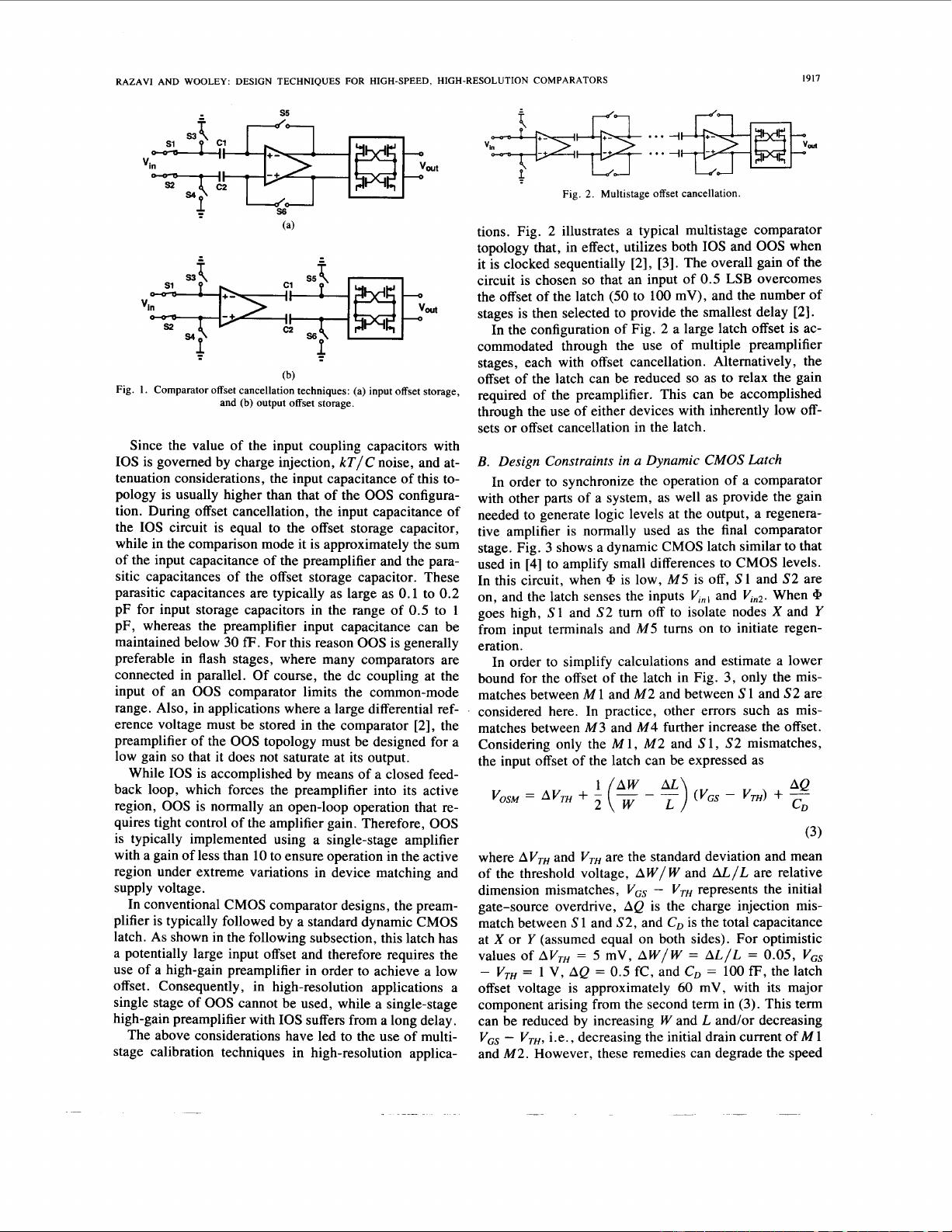

Fig.

2.

Multistage offset cancellation

tions. Fig.

2

illustrates a typical multistage comparator

topology that, in effect, utilizes both

10s

and

00s

when

it is clocked sequentially

[2],

[3].

The overall gain of the

circuit is chosen

so

that an input of

0.5

LSB

overcomes

the offset of the latch

(50

to

100

mV), and the number of

stages is then selected to provide the smallest delay

[2].

In the configuration of Fig.

2

a large latch offset

is

ac-

commodated through the use of multiple preamplifier

stages, each with offset cancellation. Alternatively, the

offset of the latch can be reduced

so

as to relax the gain

required of the preamplifier. This can be accomplished

through the use of either devices with inherently low

off-

sets or offset cancellation in the latch.

B.

Design Constraints

in

a Dynamic CMOS htch

In order to synchronize the operation of a comparator

with other parts of a system, as well as provide the gain

needed to generate logic levels at the output, a regenera-

tive amplifier is normally used as the final comparator

stage. Fig.

3

shows a dynamic CMOS latch similar to that

used in

[4]

to amplify small differences to CMOS levels.

In this circuit, when

9

is low,

M5

is off,

SI

and

S2

are

on, and the latch senses the inputs

Vjnl

and

Vjn2.

When

9

goes high,

S1

and

S2

turn off to isolate nodes

X

and

Y

from input terminals and

M5

turns on to initiate regen-

eration.

In order to simplify calculations and estimate a lower

bound for the offset of the latch in Fig.

3,

only the mis-

matches between

M

1

and

M2

and between

S

1

and

S2

are

considered here. In practice, other errors such

as

mis-

matches between

M3

and

M4

further increase the offset.

Considering only the

M1,

M2

and

S1,

S2

mismatches,

the input offset

of

the latch can be expressed as

(3)

where

AV,,

and

V,,

are the standard deviation and mean

of the threshold voltage,

AW/W

and

U/L

are relative

dimension mismatches,

VGs

-

VTH

represents the initial

gate-source overdrive,

AQ

is the charge injection mis-

match between

S

1

and

S2,

and

CD

is

the total capacitance

at

X

or

Y

(assumed equal on both sides). For optimistic

values of

AVTH

=

5

mV,

AW/W

=

AL/L

=

0.05,

VGs

-

VTH

=

1

V,

AQ

=

0.5

fC, and

CD

=

100

fF,

the latch

offset voltage is approximately

60

mV, with its major

component arising from the second term in

(3).

This term

can be reduced by increasing

W

and

L

and/or decreasing

VGs

-

VTH,

i.e., decreasing the initial drain current of

M

1

and

M2.

However, these remedies can degrade the speed

Authorized licensed use limited to: Southeast University. Downloaded on August 14,2022 at 02:01:26 UTC from IEEE Xplore. Restrictions apply.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功

评论0