宽频带数字锁相环的设计及基于 FPGA 的实现

引言

数字锁相环技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的 相比,

具有精度高、不受温度和电压影响、环路带宽和中心频率编程可调、易于构建高阶锁相环等优点。随着集成电路技术的发展,不仅能够

制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。在基于

的通信电路中,可以把全数字锁相环路作

为一个功能模块嵌入 中,构成片内锁相环。一般同步串行口通信方式的同步串行口之间的数据传输除了数据线外还必须有专门的

同步时钟线,这种连接方式不但需要增加一条线路,同步性能受环境的影响还较大。利用数字锁相环可以从串行位流数据中恢复出接收

位同步时钟。这样,串行口之间只用一根数据线就可以接收同步串行数据,简化了串行口的接口关系。本文介绍基于 数字锁相环

恢复串行数据位同步时钟的设计与实现及提高数字锁相环性能的措施。

结构及工作原理

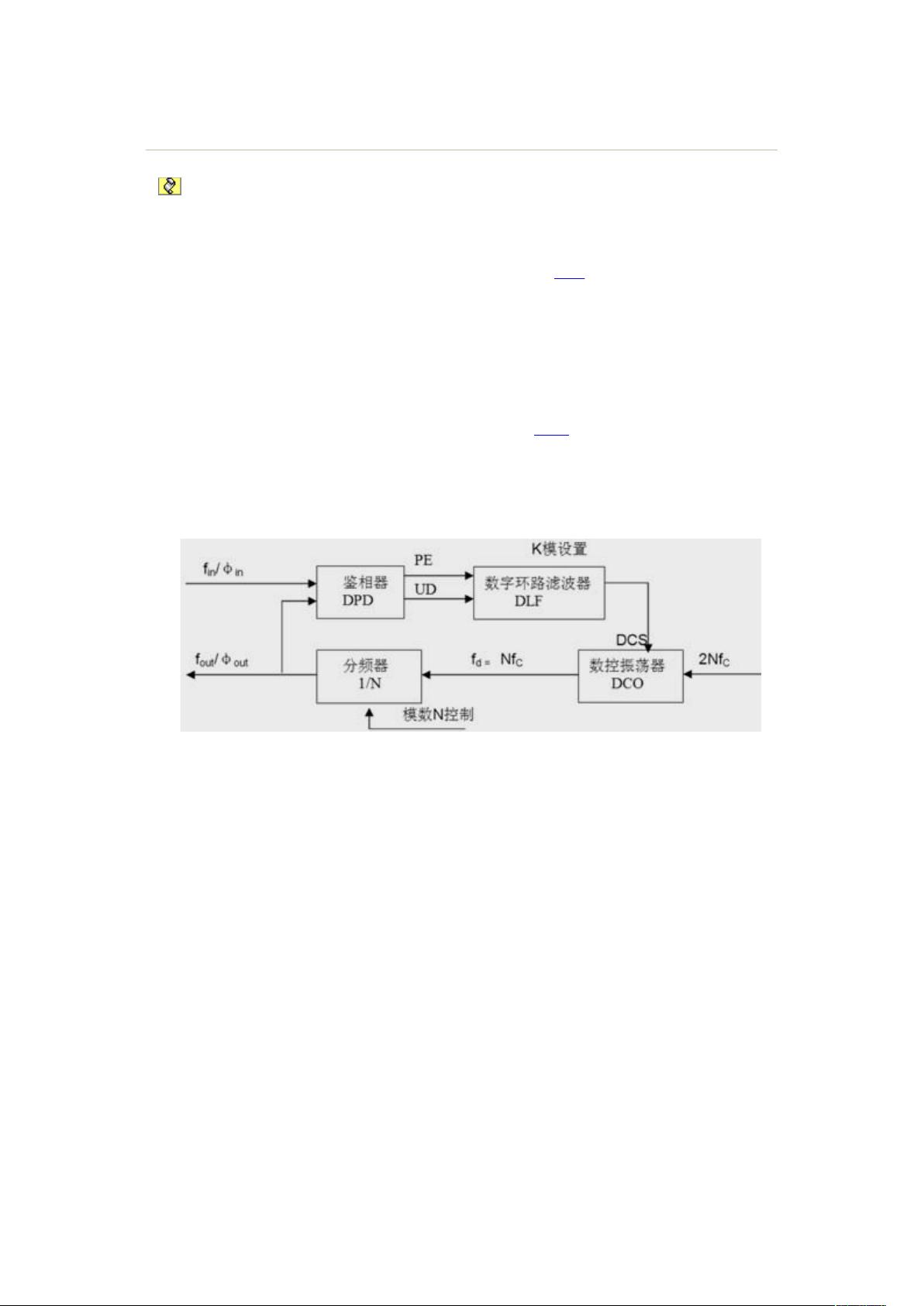

全数字锁相环路的基本结构如图 所示。主要由鉴相器 、数字环路滤波器

、脉冲加减电路数控振荡器 和分

频器可控变模 四部分构成。脉冲加减电路的时钟分别为 为环路中心频率。 是一种相位反馈控制系统。它根据输入信号

! 与本地恢复时钟 "# 之间的相位误差超前还是滞后信号送入数字环路滤波器 中对相位误差信号进行平滑滤波,并生成控制

动作的控制信号 $,根据控制信号给出的指令,调节内部高速振荡器的震荡频率,通过连续不断的反馈调节,使其输出

时钟 "# 的相位跟踪输入数据 ! 的相位。

图 全数字锁相环基本结构

环路模块具体功能及其电路实现

数字鉴相器的设计

常用的鉴相器有两种,异或门%&鉴相器和边沿控制鉴相器'。与一般 的 设计不同,位同步 的 需要

排除位流数据输入连续几位码值保持不变的不利影响。本文采用改进型异或门鉴相器,它输出一个表示本地恢复时钟超前或滞后于输入

信号的相位误差。如果本地恢复时钟超前于输入信号,则超前滞后脉冲 ( 输出为高电平,反之 ( 输出为低电平,如图 所示。

评论1

最新资源