没有合适的资源?快使用搜索试试~ 我知道了~

MTK6589规格书,详细地描述了MTK6589芯片的性能和架构,值得一看

资源推荐

资源详情

资源评论

loginid=chunping.miao@nbbsw.com,time=2012-11-23 14:49:04,ip=218.75.87.37,doctitle=MT6589_Technical_Brief_v0.2.docx,company=Bird_WCX

MT6589 HSPA+ Smartphone

Application Processor

Technical Brief

Version: 0.2

Release date: 2012-09-26

© 2011 - 2012 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Specifications are subject to change without notice.

loginid=chunping.miao@nbbsw.com,time=2012-11-23 14:49:04,ip=218.75.87.37,doctitle=MT6589_Technical_Brief_v0.2.docx,company=Bird_WCX

MT6589

HSPA+ Smartphone Application Processor

Technical Brief

Confidential A

MediaTek Confidential

© 2012 MediaTek Inc.

Page 2 of 53

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

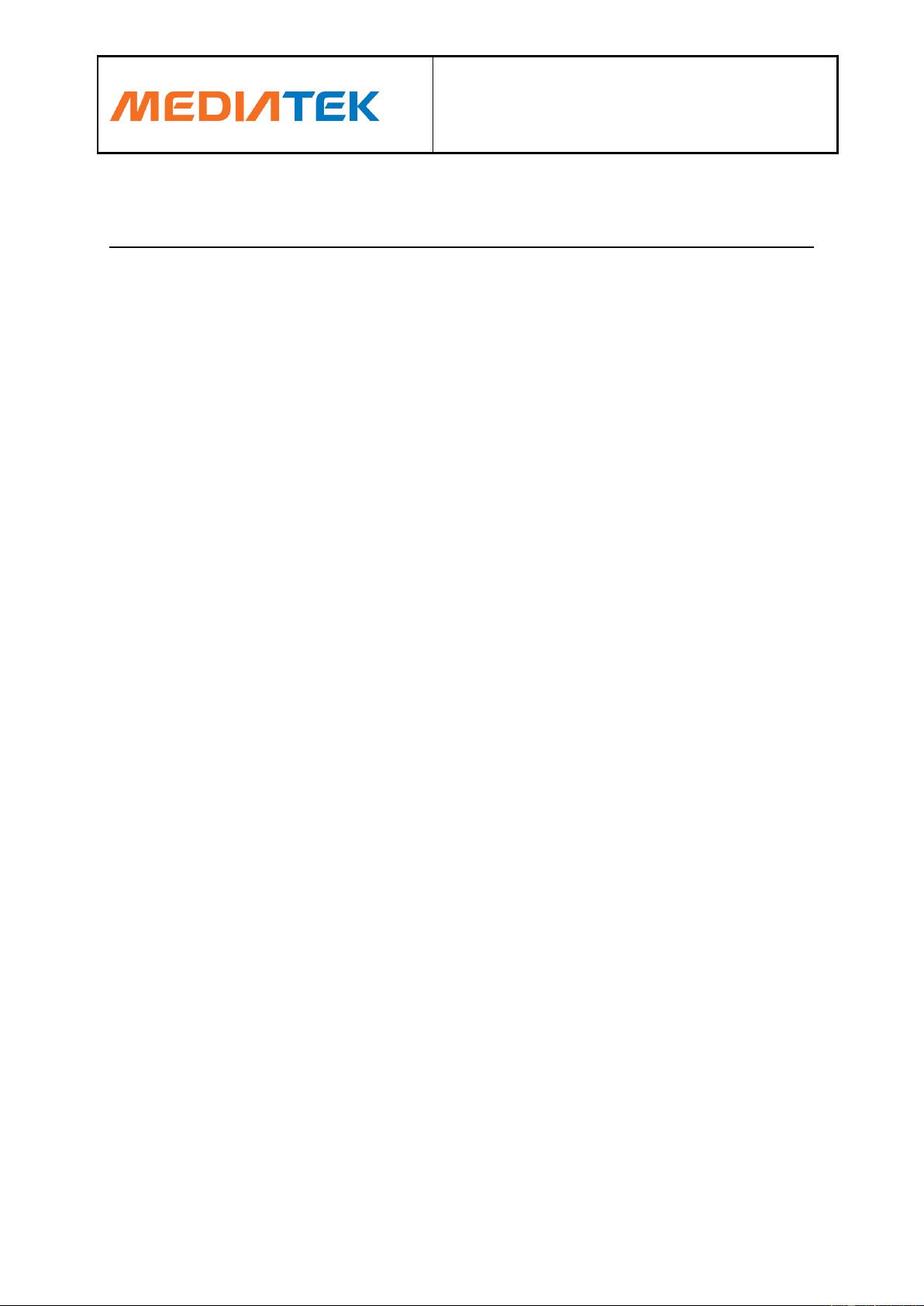

Document Revision History

Revision

Date

Author

Description

0.1

2012-09-14

YC Lai

First created by YC Lai

0.2

2012-09-26

YC Lai

Document revised.

loginid=chunping.miao@nbbsw.com,time=2012-11-23 14:49:04,ip=218.75.87.37,doctitle=MT6589_Technical_Brief_v0.2.docx,company=Bird_WCX

MT6589

HSPA+ Smartphone Application Processor

Technical Brief

Confidential A

MediaTek Confidential

© 2012 MediaTek Inc.

Page 3 of 53

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Table of Contents

Document Revision History .................................................................................................................. 2

Table of Contents ................................................................................................................................... 3

1 System Overview .......................................................................................................................... 6

1.1 Platform Features ................................................................................................................. 7

1.2 MODEM Features ................................................................................................................. 8

1.3 Multimedia Features ............................................................................................................. 9

1.4 General Descriptions .......................................................................................................... 10

2 Product Description ................................................................................................................... 12

2.1 Pin Description.................................................................................................................... 12

2.1.1 Ball Map View ..................................................................................................... 12

2.1.2 Pin Coordinate .................................................................................................... 13

2.1.3 Detailed Pin Description ..................................................................................... 17

2.2 Electrical Characteristic ...................................................................................................... 29

2.2.1 Absolute Maximum Ratings ............................................................................... 29

2.2.2 Recommended Operating Conditions ................................................................ 30

2.2.3 Storage Condition ............................................................................................... 31

2.2.4 AC Electrical Characteristics and Timing Diagram ............................................ 31

2.3 System Configuration ......................................................................................................... 34

2.3.1 Mode Selection ................................................................................................... 34

2.3.1 Constant Tie Pins ............................................................................................... 34

2.4 Power-on Sequence ........................................................................................................... 35

2.5 Analog Baseband ............................................................................................................... 36

2.5.1 BBRX .................................................................................................................. 37

2.5.2 BBTX .................................................................................................................. 39

2.5.3 2GBBTX ............................................................................................................. 41

2.5.4 APC-DAC ........................................................................................................... 42

2.5.5 VBIAS-DAC ........................................................................................................ 43

2.5.6 AUXADC ............................................................................................................ 44

2.5.7 Clock Squarer ..................................................................................................... 46

2.5.8 Phase Locked Loop............................................................................................ 46

2.5.9 Temperature Sensor .......................................................................................... 51

2.6 Package Information ........................................................................................................... 52

2.6.1 Package Outlines ............................................................................................... 52

2.6.2 Thermal Operating Specifications ...................................................................... 52

2.6.3 Lead-free Packaging .......................................................................................... 52

2.7 Ordering Information ........................................................................................................... 53

2.7.1 Top Marking Definition ....................................................................................... 53

loginid=chunping.miao@nbbsw.com,time=2012-11-23 14:49:04,ip=218.75.87.37,doctitle=MT6589_Technical_Brief_v0.2.docx,company=Bird_WCX

MT6589

HSPA+ Smartphone Application Processor

Technical Brief

Confidential A

MediaTek Confidential

© 2012 MediaTek Inc.

Page 4 of 53

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

List of Figures

Figure 1-1: Block diagram of MT6589 ................................................................................................... 11

Figure 2-1 : Ball map view of MT6589 .................................................................................................. 12

Figure 2-2: Basic timing parameter for LPDDR2 commands ................................................................ 32

Figure 2-3: Basic timing parameter for LPDDR2 write .......................................................................... 32

Figure 2-4: Basic timing parameter for LPDDR2 read .......................................................................... 33

Figure 2-8: Power on/off sequence with XTAL ...................................................................................... 35

Figure 2-9: Power on/off sequence without XTAL ................................................................................. 36

Figure 2-10: Block diagram of BBRX-ADC ........................................................................................... 38

Figure 2-11: Block diagram of 2GBBTX ................................................................................................ 41

Figure 2-12: Block diagram of APC-DAC .............................................................................................. 42

Figure 2-13: Block diagram of VBIAS-DAC .......................................................................................... 43

Figure 2-14: Block diagram of AUXADC ............................................................................................... 44

Figure 2-15: Block diagram of PLL ....................................................................................................... 47

Figure 2-16: Outlines and dimensions of FCCSP 11.8mm*11.8mm, 515-ball, 0.4mm pitch package.. 52

Figure 2-17: Top mark of MT6589 ......................................................................................................... 53

List of Tables

Table 2-1: Pin coordinate ...................................................................................................................... 13

Table 2-2: Acronym for pin type ............................................................................................................ 17

Table 2-3: Detailed pin description ........................................................................................................ 17

Table 2-4: Absolute maximum ratings for power supply ....................................................................... 29

Table 2-5: Recommended operating conditions for power supply ........................................................ 30

Table 2-6: LPDDR2 AC timing parameter table of external memory interfaces .................................... 33

Table 2-8: Mode selection of chip (PMU 6320 pin) ............................................................................... 34

Table 2-9: Constant tied pins of MT6589 .............................................................................................. 34

Table 2-10: Baseband downlink specifications ..................................................................................... 38

Table 2-11: Baseband uplink transmitter specifications ........................................................................ 40

Table 2-12: Baseband uplink transmitter specifications ........................................................................ 41

Table 2-13: APC-DAC specifications ..................................................................................................... 42

Table 2-14: VBIAS-DAC specifications ................................................................................................. 43

Table 2-15: Definitions of AUXADC channels ....................................................................................... 44

Table 2-16: AUXADC specifications ...................................................................................................... 45

Table 2-17: Clock squarer 1 & 2 specifications ..................................................................................... 46

Table 2-18: ARMPLL specifications ....................................................................................................... 47

Table 2-19: MAINPLL specifications ..................................................................................................... 48

Table 2-20: MMPLL specifications ........................................................................................................ 48

Table 2-21: ISPPLL specifications ......................................................................................................... 48

Table 2-22: UNIVPLL specifications ...................................................................................................... 49

Table 2-23: MSDCPLL specifications .................................................................................................... 49

Table 2-24: TVDPLL specifications ....................................................................................................... 49

Table 2-25: LVDSPLL specifications ..................................................................................................... 50

Table 2-26: MDPLL1 & MDPLL2 specifications .................................................................................... 50

Table 2-27: WPLL specifications ........................................................................................................... 50

Table 2-28: WHPLL specifications ........................................................................................................ 50

Table 2-29: MCUPLL1 & MCUPLL2 specifications ............................................................................... 51

Table 2-30: Temperature sensor specifications ..................................................................................... 51

Table 2-31: Thermal operating specifications ....................................................................................... 52

loginid=chunping.miao@nbbsw.com,time=2012-11-23 14:49:04,ip=218.75.87.37,doctitle=MT6589_Technical_Brief_v0.2.docx,company=Bird_WCX

MT6589

HSPA+ Smartphone Application Processor

Technical Brief

Confidential A

MediaTek Confidential

© 2012 MediaTek Inc.

Page 5 of 53

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

剩余52页未读,继续阅读

资源评论

qq_17105527

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功