没有合适的资源?快使用搜索试试~ 我知道了~

PIC16F18323数据手册

温馨提示

试读

442页

PIC16(L)F18313/18323 microcontrollers feature Analog, Core Independent Peripherals and Communication Peripherals, combined with eXtreme Low Power (XLP) for wide range of general purpose and low-power applications. The Peripheral Pin Select (PPS) functionality enables pin mapping when using the digital peripherals (CLC, CWG, CCP, PWM and communications) to add flexibility to the application design.

资源推荐

资源详情

资源评论

2015 Microchip Technology Inc. Preliminary DS40001799A-page 1

PIC16(L)F18313/18323

Description

PIC16(L)F18313/18323 microcontrollers feature Analog, Core Independent Peripherals and Communication

Peripherals, combined with eXtreme Low Power (XLP) for wide range of general purpose and low-power applications.

The Peripheral Pin Select (PPS) functionality enables pin mapping when using the digital peripherals (CLC, CWG,

CCP, PWM and communications) to add flexibility to the application design.

Core Features

• C Compiler Optimized RISC Architecture

• Only 49 Instructions

• Operating Speed:

- DC – 32 MHz clock input

- 125 ns minimum instruction cycle

• Interrupt Capability

• 16-Level Deep Hardware Stack

• Two 8-bit Timers

• One 16-bit Timer

• Low-Current Power-on Reset (POR)

• Configurable Power-up Timer (PWRTE)

• Brown-out Reset (BOR) with Fast Recovery

• Low-Power BOR (LPBOR) Option

• Extended Watchdog Timer (WDT) with Dedicated

On-chip Oscillator for Reliable Operation

• Programmable Code Protection

Memory

• 3.5 KB Flash Program Memory

• 256B Data SRAM Memory

• 256B of EEPROM

• Direct, Indirect and Relative Addressing Modes

Operating Characteristics

• Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF18313/18323)

- 2.3V to 5.5V (PIC16F18313/18323)

• Temperature Range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

eXtreme Low-Power (XLP) Features

• Sleep mode: 40 nA @ 1.8V, typical

• Watchdog Timer: 250 nA @ 1.8V, typical

• Secondary Oscillator: 300 nA @ 32 kHz

• Operating Current:

- 8 uA @ 32 kHz, 1.8V, typical

- 37 uA/MHz @ 1.8V, typical

Power-Saving Operating Modes

• IDLE: Ability to put the CPU core to Sleep while

internal peripherals continue operating from the

system clock

• DOZE: Ability to run the CPU core slower than the

system clock used by the internal peripherals

• SLEEP: Lowest Power Consumption

• Peripheral Module Disable (PMD): Peripheral

power disable hardware module to minimize

power consumption of unused peripherals

Digital Peripherals

• Configurable Logic Cell (CLC):

- Two CLCs

- Integrated combinational and sequential logic

• Complementary Waveform Generator (CWG):

- Rising and falling edge dead-band control

- Full-bridge, half-bridge, 1-channel drive

- Multiple signal sources

• Capture/Compare/PWM (CCP) modules:

- Two CCPs

- 16-bit resolution for Capture/Compare modes

- 10-bit resolution for PWM mode

• Pulse-Width Modulators:

-Two 10-bit PWMs

• Numerically Controlled Oscillator (NCO):

- Precision linear frequency generator(@50%

duty cycle) with 0.0001% step size of source

input clock

- Input Clock: 0 Hz < F

NCO

< 32 MHz

- Resolution: F

NCO

/2

20

• Serial Communications:

- EUSART

- RS-232, RS-485, LIN compatible

- Auto-baud detect, Auto-wake-up on start

- Master Synchronous Serial Port (MSSP)

- SPI

-I

2

C™, SMBus, PMBus™ compatible

• Data Signal Modulator (DSM):

- Modulates a carrier signal with digital data to

create custom carrier synchronized output

waveforms

Full-Featured, Low Pin Count Microcontrollers with XLP

PIC16(L)F18313/18323

DS40001799A-page 2 Preliminary 2015 Microchip Technology Inc.

• Up to 12 I/O Pins:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge select

- Input level selection control (ST or TTL)

- Digital Open-Drain enable

• Peripheral Pin Select (PPS):

- I/O pin remapping of digital peripherals

Timer Modules

•Timer0:

- 8/16-bit timer/counter

- Synchronous or asynchronous operation

- Programmable Prescaler/Postscaler

- Time base for Capture/Compare function

• Timer1 with Gate Control:

- 16-bit timer/counter

- Programmable internal or external clock

sources

- Multiple gate sources

- Multiple gate modes

- Time base for Capture/Compare function

•Timer2:

- 8-bit timer

- Programmable Prescaler/Postscaler

- Time base for PWM function

Analog Peripherals

• 10-bit Analog-to-Digital Converter (ADC):

- Up to 17 external channels

- Conversion available during Sleep

• Comparator:

- Up to two comparators

- Fixed Voltage Reference at non-inverting

input(s)

- Comparator outputs externally accessible

• 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and

comparators

• Voltage Reference:

- Fixed Voltage Reference with 1.024V, 2.048V

and 4.096V output levels

Flexible Oscillator Structure

• High-Precision Internal Oscillator:

- Software selectable frequency range up to 32

MHz

- ±1% at nominal 4 MHz calibration point

• 4xPLL with External Sources

• Low-Power Internal 31 kHz Oscillator

(LFINTOSC)

• External Low-Power 32 kHz Crystal Oscillator

(SOSC)

• External Oscillator Block with:

- Three Crystal/Resonator modes up to 20

MHz

- Three External Clock modes up to 20 MHz

- Fail-Safe Clock Monitor

- Allows for safe shutdown if peripheral clock

stops

- Oscillator Start-up Timer (OST)

- Ensures stability of crystal oscillator

resources

2015 Microchip Technology Inc. Preliminary DS40001799A-page 3

PIC16(L)F18313/18323

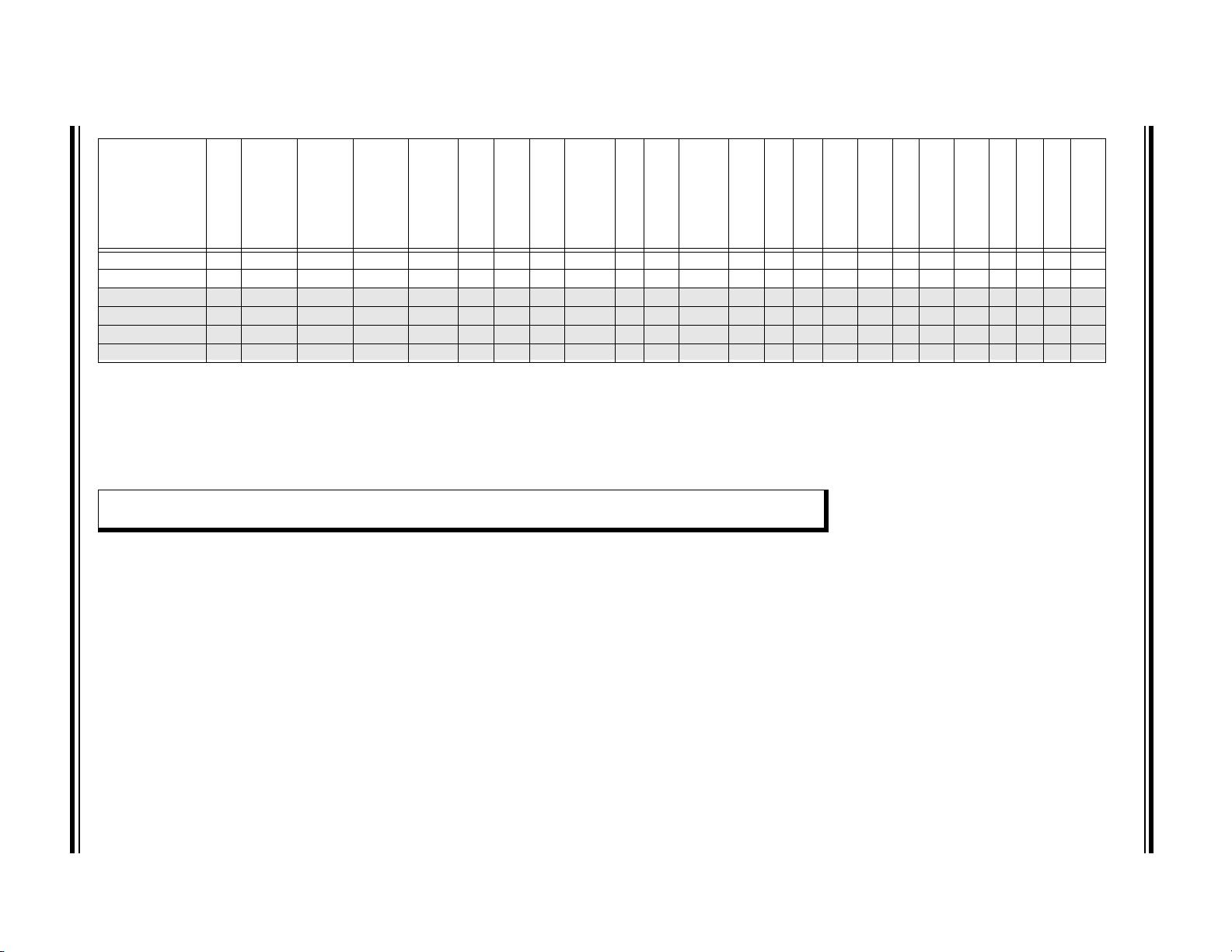

PIC16(L)F183XX Family Types

Device

Data Sheet Index

Program Flash

Memory (words)

Program Memory

Flash (K Bytes)

Data Memory

(bytes)

Data SRAM

(bytes)

I/Os

(2)

10-bit ADC (ch)

5-bit DAC

High-Speed/

Comparators

CWG

Clock Ref

Timers

(8/16-bit)

CCP

10-bit PWM

NCO

EUSART

MSSP (I

2

C™/SPI)

CLC

DSM

PPS

XLP

PMD

Idle & Doze

Debug

(1)

PIC16(L)F18313 (1) 2048 3.5 256 256 6 5 1 1 1 1 2/1 2 2 1 1 1 2 1 Y Y Y Y I

PIC16(L)F18323 (2) 2048 3.5 256 256 12 11 1 2 1 1 2/1 2 2 1 1 1 2 1 Y Y Y Y I

PIC16(L)F18324 (2) 4096 7 256 512 12 11 1 2 2 1 4/1 4 2 1 1 1 4 1 Y Y Y Y I

PIC16(L)F18325 (3) 8192 14 256 1024 12 11 1 2 2 1 4/3 4 2 1 1 2 4 1 Y Y Y Y I

PIC16(L)F18344 (2) 4096 7 256 512 18 17 1 2 2 1 4/3 4 2 1 1 1 4 1 Y Y Y Y I

PIC16(L)F18345 (3) 8192 14 256 1024 18 17 1 2 2 1 4/3 4 2 1 1 2 4 1 Y Y Y Y I

Note 1: Debugging Methods: (I) – Integrated on Chip

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS40001799 PIC16(L)F18313/18323 Data Sheet, Full-Featured, Low Pin Count Microcontrollers with XLP

2: DS40001800 PIC16(L)F18324/18344 Data Sheet, Full-Featured, Low Pin Count Microcontrollers with XLP

3: DS40001795 PIC16(L)F18325/18345 Data Sheet, Full-Featured, Low Pin Count Microcontrollers with XLP

Note: For other small form-factor package availability and marking information, please visit

http://www.microchip.com/packaging or contact your local sales office.

PIC16(L)F18313/18323

DS40001799A-page 4 Preliminary 2015 Microchip Technology Inc.

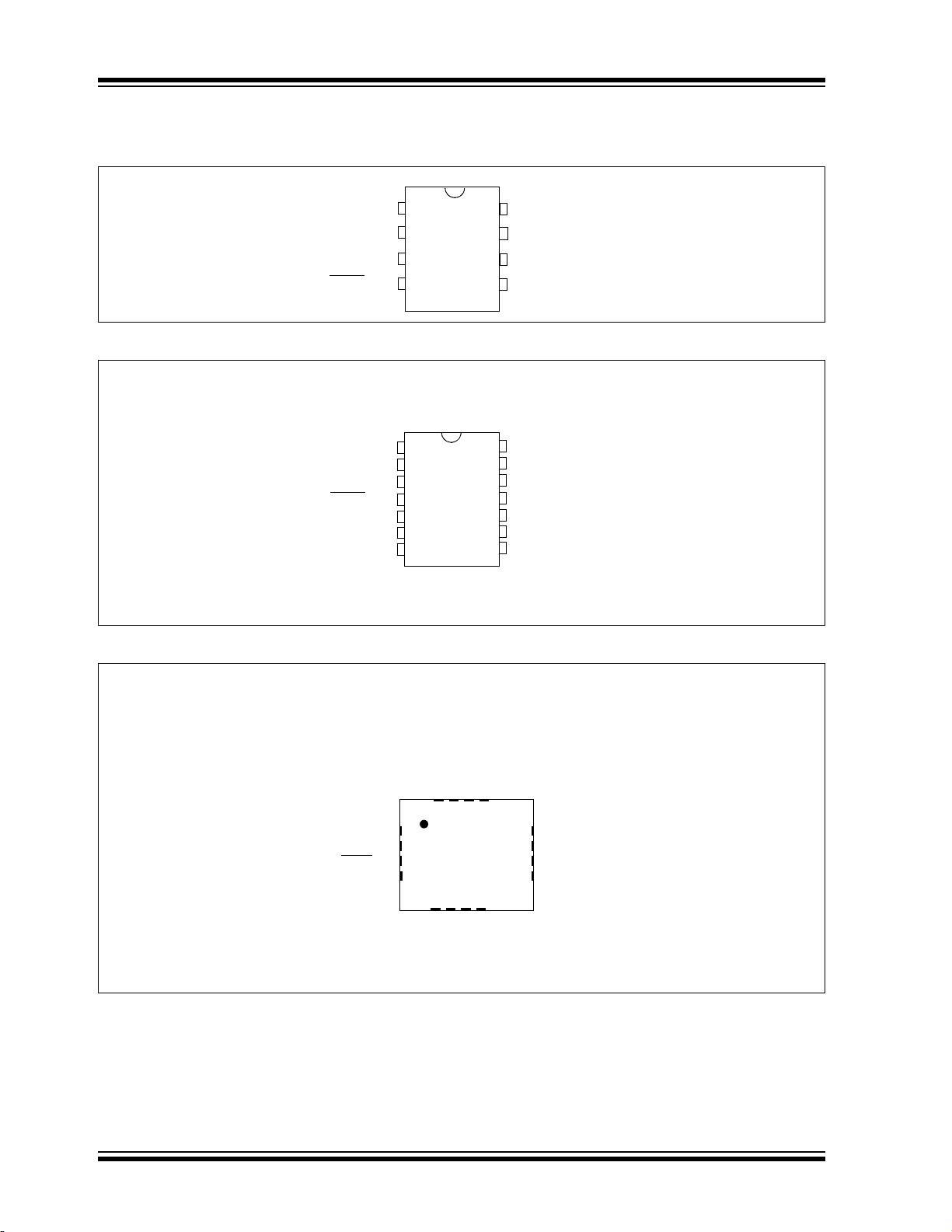

Pin Diagrams

FIGURE 1: 8-PIN PDIP, SOIC, UDFN

FIGURE 2: 14-PIN PDIP, SOIC, TSSOP

FIGURE 3: 16-PIN UQFN

1

2

3

4

VDD

RA5

RA4

V

PP/MCLR/RA3

RA0/ICSPDAT

RA1/ICSPCLK

RA2

V

SS

8

7

6

5

PIC16(L)F18313

1

2

3

4

5

6

7

VDD

RA5

RA4

V

PP/MCLR/RA3

RC5

RC4

RC3

RA0/ICSPDAT

RA1/ICSPCLK

RA2

RC0

RC1

RC2

14

13

12

11

10

9

8

V

SS

PIC16(L)F18323

2

3

1

9

10

11

12

RC4

4

VSS

RA0/ICSPDAT

RA1/ICSPCLK

RA2

RC0

NC

NC

V

DD

RA5

RA4

RA3/MCLR

/VPP

RC5

RC3

RC2

RC1

6

7

5

8

15

14

16

13

PIC16(L)F18323

Note 1: It is recommended that the exposed bottom pad be connected to VSS, but must not be the main VSS

connection to the device.

2015 Microchip Technology Inc. Preliminary DS40001799A-page 5

PIC16(L)F18313/18323

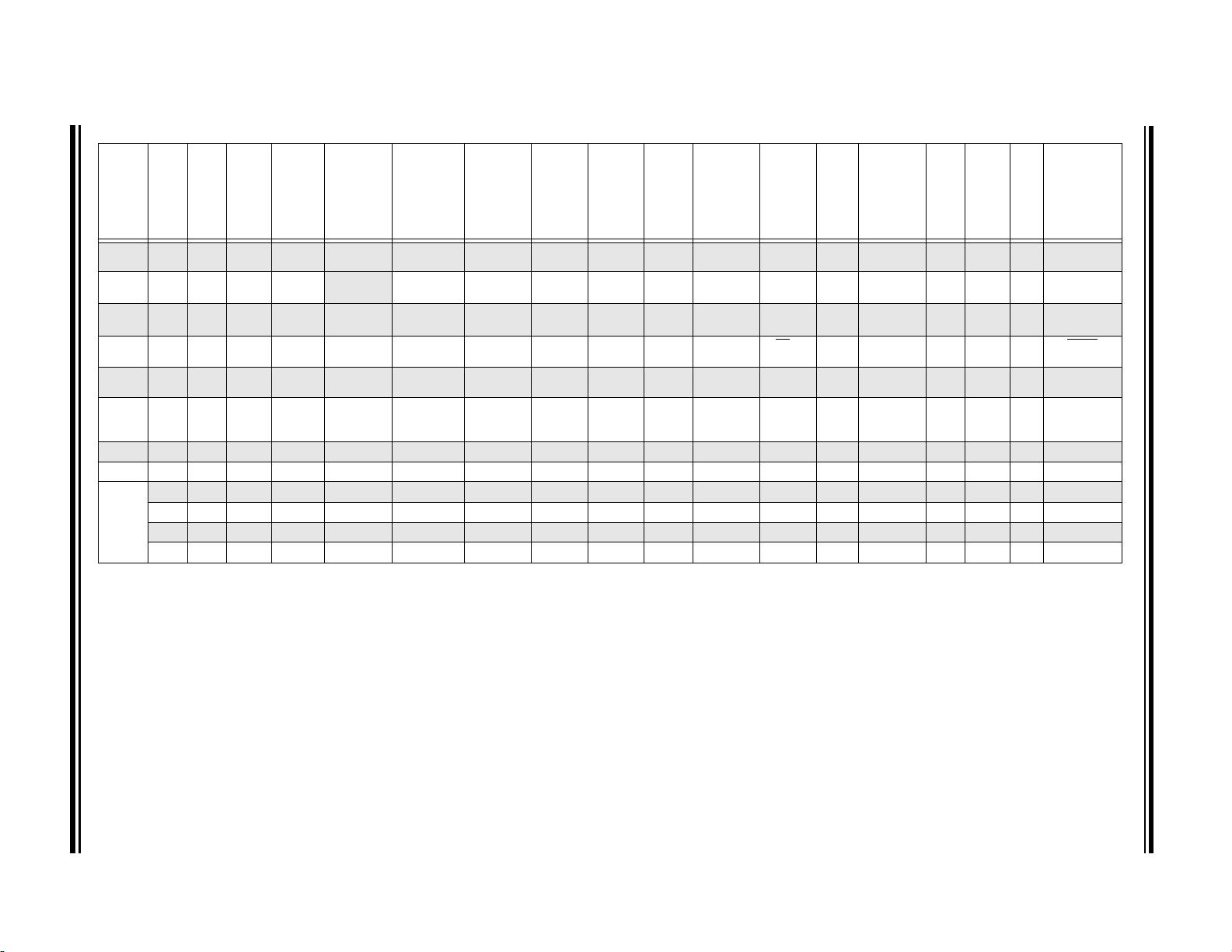

TABLE 1: 8-PIN ALLOCATION TABLE (PIC16(L)F18313)

I/O

(2)

PDIP/SOIC/UDFN

ADC

Reference

Comparator

NCO

DAC

DSM

Timers

CCP

PWM

CWG

MSSP

EUSART

CLC

CLKR

Interrupt

Pull-up

Basic

RA0 7 ANA0 — C1IN0+ — DAC1OUT MDCIN1

(1)

— — — — — — CLCIN3

(1)

— IOC Y ICDDAT/

ICSPDAT

RA1 ANA1 VREF+

C1IN0-

—

DAC1

REF+MDMIN

(1)

————

SCK

(1)

SCL

(1,3,4)

RX

(1))

DT

(1,3)

CLCIN2

(1)

—

IOC Y ICDCLK/

ICSPCLK

RA2 5 ANA2 VREF- — — DAC1REF- — T0CKI

(1)

— — CWG1IN

(1)

SDA

(1,3,4)

SDI

(1)

— — — INT

(1)

IOC

Y —

RA3 4

—— — — — — — — — —

SS

(1)

—

CLCIN0

(1)

—

IOC Y MCLR

VPP

RA4 3 ANA4

— C1IN1- — — —

T1G

(1)

SOSCO

— — — — — — —

IOC Y CLKOUT

OSC2

RA5 2 ANA5

—— — —

MDCIN2

(1)

T1CKI

(1)

SOSCIN

SOSCI

CCP1

(1)

CCP2

(1)

—— ——

CLCIN1

(1)

—

IOC Y CLKIN

OSC1

VDD 1

— — — — — — — — — — — — —

—

— —

VDD

VSS 8

—— — — — — — — — — — — — ———

VSS

OUT

(2)

— — — C1OUT NCO — DSM TMR0 CCP1 PWM5 CWG1A SDA

(3)

CK CLC1OUT CLKR — — —

—— — — — — — —

CCP2 PWM6 CWG1B SCL

(3)

DT

(3)

CLC2OUT

——— —

— — — — — — — — — — CWG1C SDO TX — — — — —

—— — — — — — — — —

CWG1D SCK

————— —

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 12-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-2.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I

2

C™ logic levels as described in Section 12.3 “Bidirectional Pins”; clock and data signals may be assigned to any of these pins. Assignments to the other pins (e.g.,

RA5) will operate, but logic levels will be standard TTL/ST as selected by the INLVL register.

剩余441页未读,继续阅读

资源评论

uestc_somnus2018-07-07很好的资源,多谢分享

uestc_somnus2018-07-07很好的资源,多谢分享 starling882016-07-07不错,只是有一点可惜的是,它是英文的。

starling882016-07-07不错,只是有一点可惜的是,它是英文的。

qq453046836

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功