16-Bit Digital Signal

Controllers (DSC)

freescale.com

56F802X and 56F803X

Peripheral Reference Manual

MC56F80XXRM

Rev. 3

02/2007

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2006. All rights reserved.

56F802x and 56F803x Peripheral Reference Manual, Rev. 3

Freescale Semiconductor iii

About This Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xlv

Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xlv

Manual Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xlv

Suggested Reading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xlvi

Manual Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xlvii

Pin Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xlviii

Chapter 1

Overview

1.1 Introduction to the 56800E Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1.1 DSP56800 Core Enhancements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1.2 DSP56800 Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.1.2.1 Address Buses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.1.2.2 Data Buses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.1.2.3 Data Arithmetic Logic Unit (Data ALU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.1.2.4 Address Generation Unit (AGU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.1.2.5 Program Controller and Hardware Looping Unit . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.1.2.6 Bit Manipulation Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.1.2.7 Enhanced On-Chip Emulation (EOnCE) Module . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.1.3 System Bus Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.1.4 Operation Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.2 Introduction to 56F80xx Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2.1 Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2.3 System Architecture and Peripheral Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2.4 IPBus Bridge (IPBB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.2.4.1 System Side Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.2.4.2 Peripheral Side Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.5 Peripheral Interrupts/Interrupt Controller Module . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.5.1 System Integration Module (SIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.6 56F80xx Peripheral Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.6.1 Analog-to-Digital Converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.6.2 Computer Operating Properly (COP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.2.6.3 Inter-Integrated Circuit Interface (I

2

C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.2.6.4 On-Chip Clock Synthesis (OCCS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.2.6.5 Flash Memory (FM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.2.6.6 General Purpose Input/Output (GPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

Contents

56F802x and 56F803x Peripheral Reference Manual, Rev. 3

iv Freescale Semiconductor

1.2.6.7 Pulse Width Modulator (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.2.6.8 Scalable Controller Area Network (MSCAN) . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.2.6.9 Joint Test Action Group Port (JTAG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.2.6.10 Power Supervisor (PS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.2.6.11 Queued Serial Communications Interface (QSCI) . . . . . . . . . . . . . . . . . . . . . 1-15

1.2.6.12 Queued Serial Peripheral Interface (QSPI) . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

1.2.6.13 Quad Timer (TMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

1.2.6.14 Voltage Regulator (V

REG

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

1.2.6.15 Programmable Interval Timer (PIT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

1.2.6.16 Digital-to-Analog Converter (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

1.2.6.17 Comparator (CMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

1.3 Energy Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

Chapter 2

Analog Digital Converter (ADC)

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

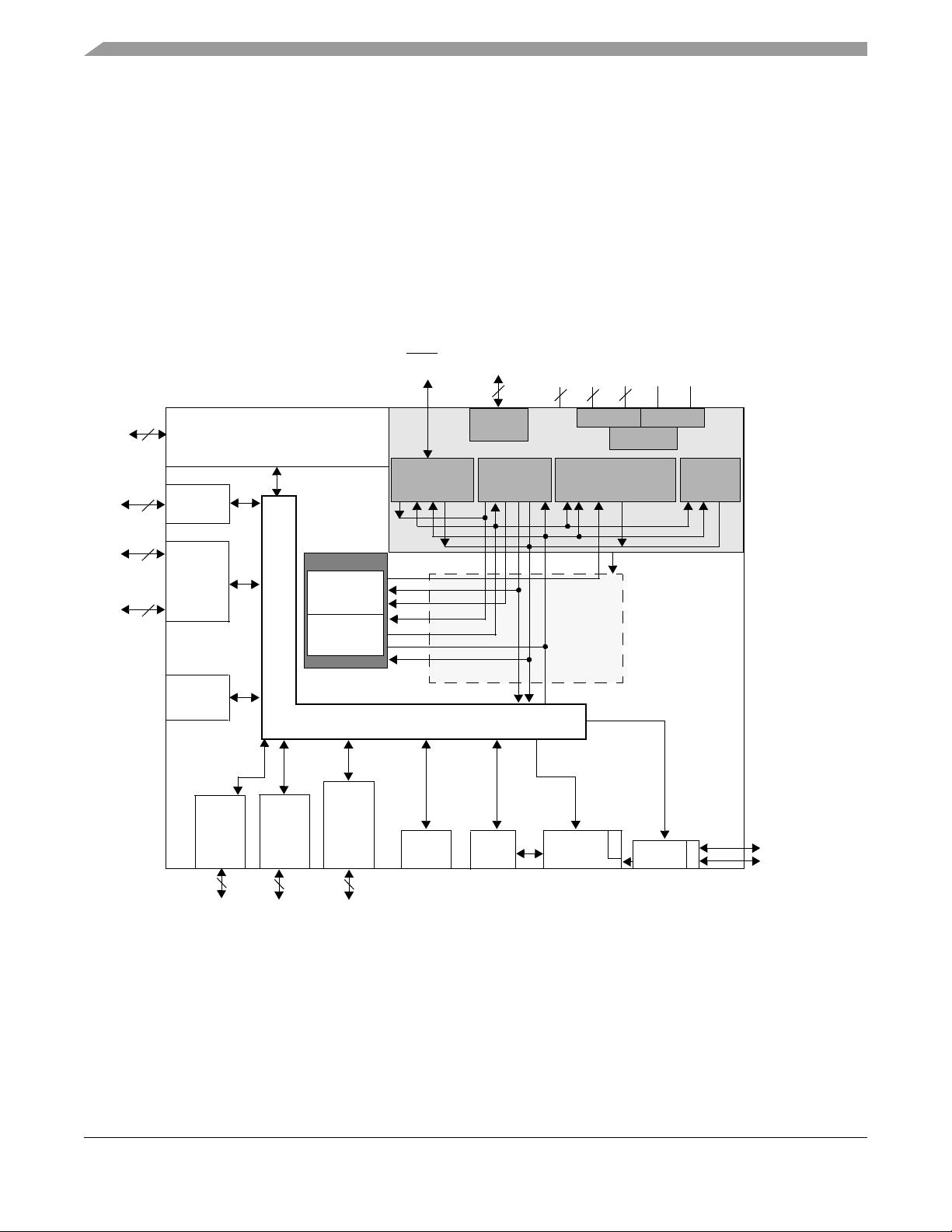

2.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.5 Input MUX Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.6 ADC Sample Conversion Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.6.1 Normal Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.6.1.1 Single-Ended Samples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.6.1.2 Differential Samples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.6.2 ADC Data Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.6.3 Sequential vs. Parallel Sampling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.6.4 Scan Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.6.5 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.6.5.1 Manual Power Down of Unused Converters . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.6.5.2 Power Management Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.6.6 Power Management Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.6.7 STOP Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.6.8 ADC Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.6.8.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.6.8.2 Description of Clock Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.6.8.3 ADC Clock Re-synchronization at Start of Scan . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.6.9 Voltage Reference Pins V

REFH

& V

REFLO

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2.6.10 Supply Pins V

DDA

and V

SSA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.7 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.7.1 Control 1 (CTRL1) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.7.1.1 Reserved—Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.7.1.2 Stop (STOP0)—Bit 14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.7.1.3 Start Conversion (START0)—Bit 13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

56F802x and 56F803x Peripheral Reference Manual, Rev. 3

Freescale Semiconductor v

2.7.1.4 SYNC0 Enable (SYNC0)—Bit 12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.7.1.5 End Of Scan Interrupt 0 Enable (EOSIE0)—Bit 11 . . . . . . . . . . . . . . . . . . . . . 2-22

2.7.1.6 Zero Crossing Interrupt Enable (ZCIE)—Bit 10 . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.7.1.7 Low Limit Interrupt Enable (LLMTIE)—Bit 9 . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.7.1.8 High Limit Interrupt Enable (HLMTIE)—Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.7.1.9 Channel Configure Low (CHNCFG_L)—Bits 7–4 . . . . . . . . . . . . . . . . . . . . . . 2-22

2.7.1.10 Scan Mode Control (SMODE)—Bits 2-0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.7.2 Control 2 (CTRL2) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.7.2.1 Reserved—Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.7.2.2 Stop 1 (STOP1)—Bit 14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.7.2.3 Start Conversion 1 (START1)—Bit 13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.7.2.4 SYNC1 Enable (SYNC1)—Bit 12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.7.2.5 End of Scan Interrupt 1 Enable (EOSIE1)—Bit 11 . . . . . . . . . . . . . . . . . . . . . 2-25

2.7.2.6 Reserved—Bit 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.7.2.7 Channel Configure High (CHNCFG_H)—Bits 9–6 . . . . . . . . . . . . . . . . . . . . . 2-25

2.7.2.8 Simultaneous Mode (SIMULT)—Bit 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

2.7.2.9 Clock Divisor Select (DIV)—Bits 4–0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

2.7.3 ADC Zero Crossing Control (ZXCTRL) Register. . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2.7.3.1 Zero Crossing Enable n (ZCEn)—Bits15–0 . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2.7.4 Channel List n (CLIST1-4) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2.7.5 Sample Disable (SDIS) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

2.7.5.1 Disable Sample (DS)—Bits 15–0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

2.7.6 Status (STAT) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

2.7.6.1 Conversion in Progress 0 (CIP0)—Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

2.7.6.2 Conversion in Progress 1 (CIP1)—Bit 14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.7.6.3 Reserved—Bit 13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.7.6.4 End of Scan Interrupt 1 (EOSI1)—Bit 12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.7.6.5 End of Scan Interrupt 0 (EOSI0)—Bit 11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.7.6.6 Zero Crossing Interrupt (ZCI)—Bit 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.7.6.7 Low Limit Interrupt (LLMTI)—Bit 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

2.7.6.8 High Limit Interrupt (HLMTI)—Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

2.7.6.9 Ready Sample 7–0 (RDY)—Bits 7–0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2.7.7 Conversion Ready (RDY) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2.7.7.1 Ready Sample 15–0 (RDY)—Bits 15–0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2.7.8 Limit Status (LIMSTAT) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2.7.9 Zero Crossing Status (ZXSTAT) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.7.9.1 Reserved—Bits 15–8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.7.9.2 Zero Crossing Status (ZCS)—Bits 7–0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.7.10 Result 0–7 (RSLT0–7) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.7.10.1 Sign Extend (SEXT)—Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2.7.10.2 Digital Result of the Conversion (RSLT)—Bits 14–3 . . . . . . . . . . . . . . . . . . . 2-34

2.7.10.3 Test Data (TEST_DATA)—Bits 14–3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2.7.10.4 Reserved—Bits 2–0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2.7.11 Result 8–15 (RSLT8–15) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34