集成电路的后端设计

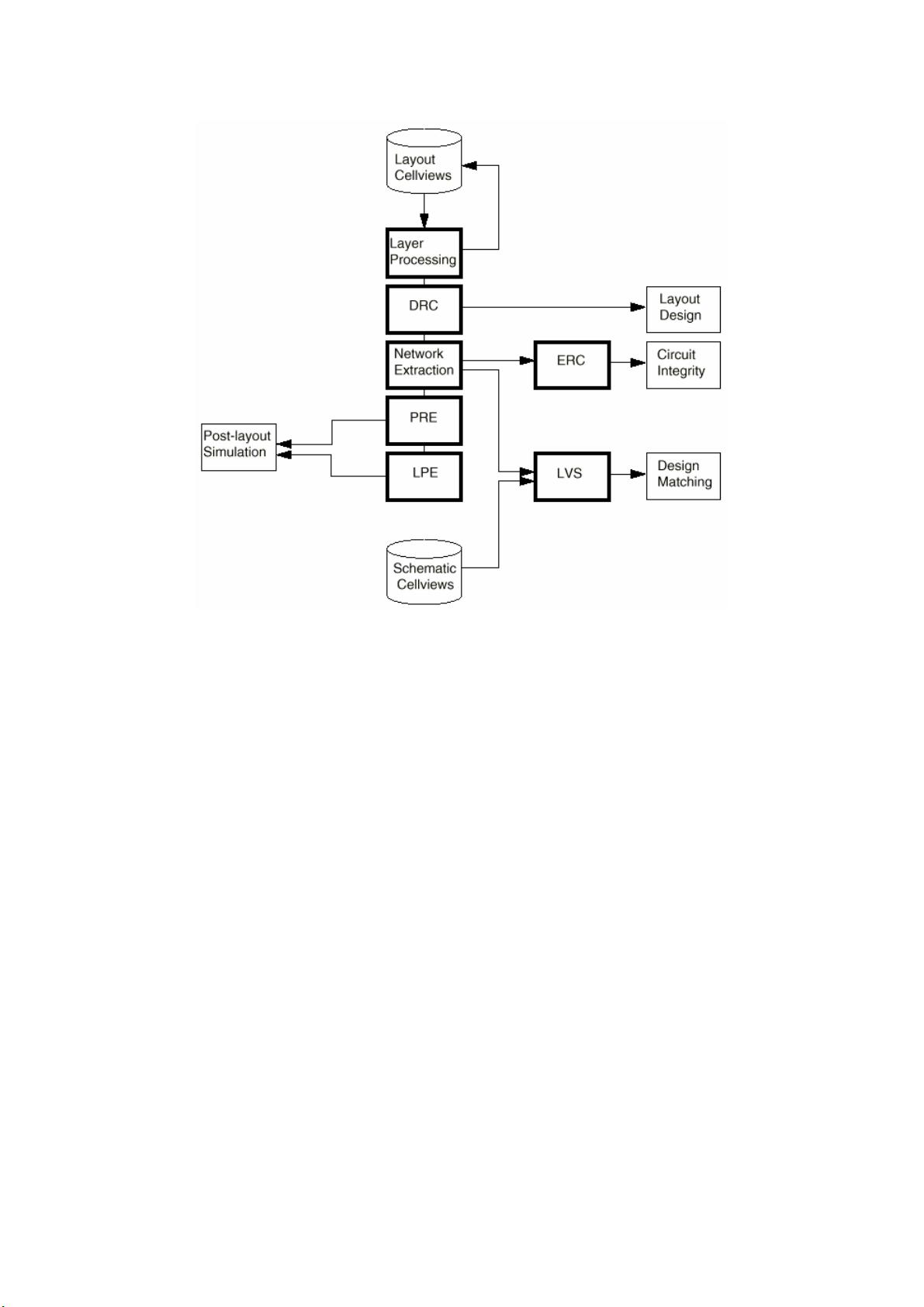

集成电路的后端设计包括版图设计和验证。我们采用Cadence的Virtuoso

Layout Editor的版图设计环境进行版图设计。利用Virtuoso Layout Editer的集成验

证工具

DIVA进行了验证。验证的整个的过程包括:设计规则检查(Design Rule

Checking 简称DRC )、电学规则检查(Electronics Rule Checking 简称ERC)、

电路图版图对照(Layout Versus Schematic 简称LVS)、以及版图寄生参数提取

(Layout Parameter Extraction 简称LPE)。

版图设计流程

1、整体设计:确定版图主要模块和焊盘的布局。这个布局图应该和功能框图或

电路图大体一致,然后根据模块的面积大小进行调整。布局设计的另一个重要的

任务是焊盘的布局。焊盘的安排要便于内部信号的连接,要尽量节省芯片面积以

减少制作成本。焊盘的布局还应该便于测试,特别是晶上测试。

2、分层设计:设计者按照电路功能划分整个电路,对每个功能块进行再划分,

每一个模块对应一个单元。从最小模块开始到完成整个电路的版图设计,设计者

需要建立多个单元。这一步就是自顶向下的设计 。这样做有很多好处,最为突

出的优点是当在整个电路多次出现的某一个模块需要修改时,直接在下一层次修

改该模块,上一层的所有同样单元就一并得到修改,结构严谨、层次清晰。

3、版图的检查:

①执行DRC程序,对每个单元版图进行设计规则检查,并修改错处。在画版图的

过程中要不时地进行设计规则检查。运行DRC,程序就按照Diva规则检查文件运

行,发现错误时,会在错误的地方做出标记(mark),并且做出解释(explain)。

设计者就可以根据提示来进行修改。需要注意的是,DRC要在画图过程中经常进

行,及时发现问题及时修改,不要等到版图基本完成后在做,这时再出现的错误

往往很难修改,因为各个器件的位置已经相对固定,对于电路一处的改动往往牵

连到多个相邻的器件,从而造成更多的问题。

②执行EXT程序,对版图进行包括电路拓扑结构、元件及其参数的提取。设计规

则检查只检验几何图形的正确与否。在电路方面的错误,要用到Cadence提供的

另外两种功能:Extract和LVS。Extract是系统根据版图和工艺文件提取版图的电

路特性,也就是“认出”版图代表什么电路器件,NMOS或是PMOS,还是其他。

电路提取后的版图作为单元的另外一种试图(Extracted)保存下来。

③执行LVS程序,将提取出的版图与电路图进行对照,并进行修改直到版图和电

路图完全一致。LVS就是把Extracted与单元的另外一种视图—schematic比较,

检查版图实现的电路是否有错。所以,在LVS之前应该把设计好的电路图做出来。