共

45

页产品名称

内部公开

2.1

密级产品版本文档编号

研究管理部文档中心

Synplify工具使用指南

(

征求意见稿 仅供内部使用

)

/ /

日期文档管理员

/ /

日期总

体

组

/ /

日期研

究

部

/ /

日期项

目

经

理

2001/ 03 /20

日期

文

档

作

者

版权所有

不得复制

修订记录

第三次修订2.102000/4/2

第二次修订2.002000/3/20

第一次修订1.102000/9/20

初稿完成1.002000/08/20

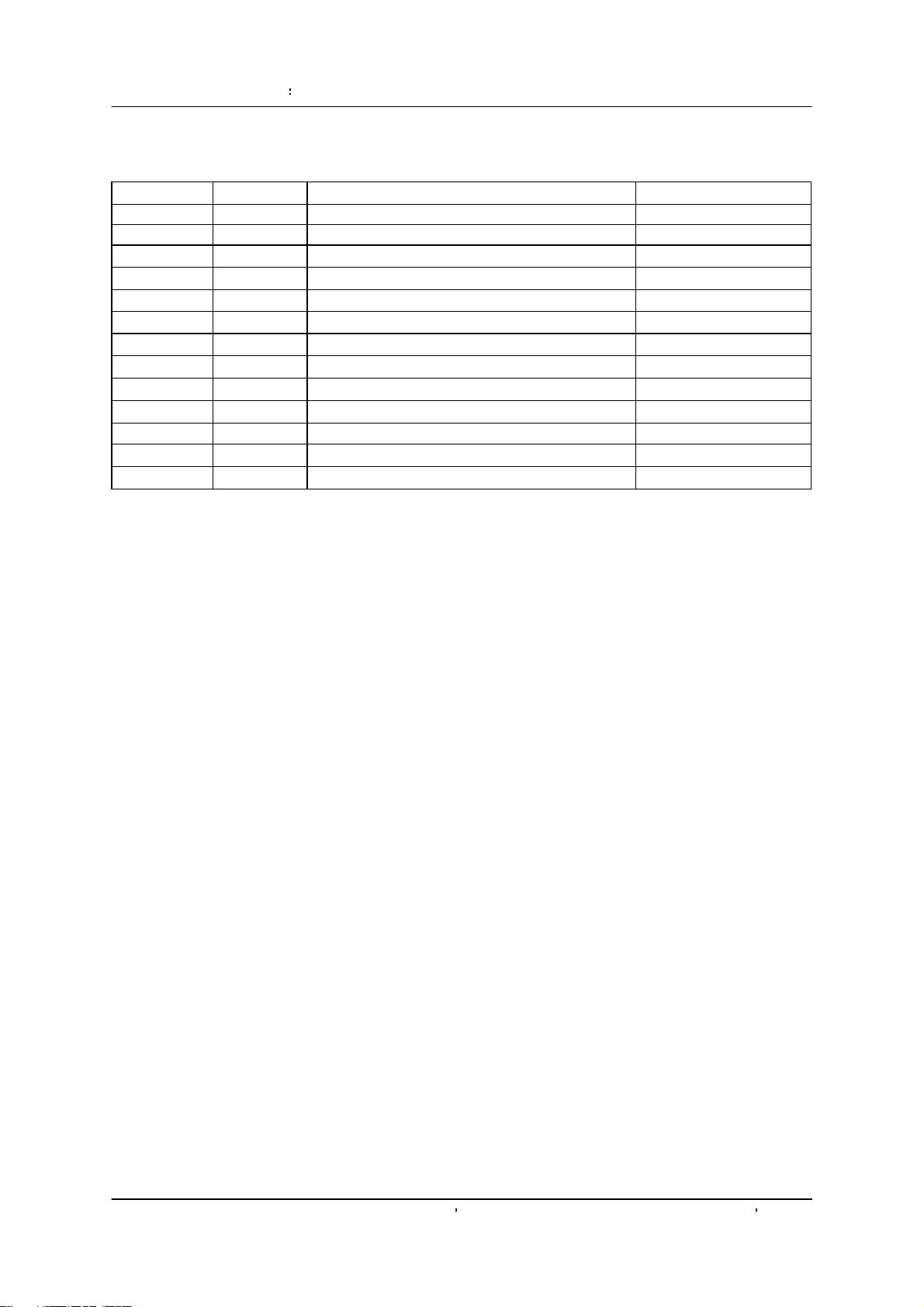

作者描述修订版本日期

内部公开

请输入文档编号请输入文档名称 Synplify工具使用指南

2001-04-09 版权所有 侵权必究 第2页 共45页

目 录

16

6怎样用Tcl语言执行批处理任务

..............................................

15

5使用Symbolic FSM compiler

................................................

14

4.2.4查看延迟信息

..................................................

14

4.2.3链接式选中目标

................................................

14

4.2.2状态条显示

....................................................

14

4.2.1POP_UP信息

...................................................

14

4.2HDL Analyst 的应用

..................................................

14

4.1HDL Analyst 简介

...................................................

14

4使用HDL Analyst分析和调试设计

............................................

13

3.3.2运行一个Tcl文件

................................................

13

3.3.1运行工程文件

..................................................

13

3.3批处理工作模式流程

.................................................

12

4.Net Buffering报告

.............................................

12

3.资源使用报告

................................................

12

2.时间报告 Timing Report

......................................

12

1.Log 文件

....................................................

12

3.2.4生成的报告和信息

..............................................

12

9.Other

.......................................................

11

8.Attribute

.....................................................

11

7.False Path

....................................................

11

6.Multicycle Paths

...............................................

11

5.Registers

....................................................

10

4.Input/Output

.................................................

10

3.Clock to Clock

................................................

9

2.Clock

........................................................

8

1.Insert Wizard

.................................................

8

3.2.3 SCOPE窗口

....................................................

7

2.用户界面的按钮

...............................................

7

1.工具条

......................................................

3.2.2UNIX版用户界面简介

...................................

............

7

3.2.1UNIX环境设置

.................................................

7

3.2UNIX环境下窗口界面工作流程

..........................................

7

3.1PC版基本工作流程

...................................................

6

3基本工作流程

............................................................

6

2.6属性包

.............................................................

6

2.5宏库

...............................................................

6

2.4约束文件

...........................................................

6

2.3Tcl 脚本

............................................................

6

2.2工程文件

...........................................................

6

2.1综合

...............................................................

6

2基本概念

...............................................................

5

1前言

...................................................................

内部公开

请输入文档编号请输入文档名称 Synplify工具使用指南

2001-04-09 版权所有 侵权必究 第3页 共45页

39

9.3.2扇出限制

......................................................

38

9.3.1时钟

.........................................................

38

9.3关于综合约束的建议

.................................................

38

9.2怎样处理关键路径上不满足速度要求的延迟

...............................

38

9.1一般性考虑

........................................................

38

9实现对速度的优化

.......................................................

35

8.2.1综合指示 Directives

...........................................

30

8.2.1Xilinx

........................................................

27

8.2.1Altera

........................................................

27

8.2厂家提供属性

......................................................

26

8.1简介

..............................................................

26

8综合属性 Attributes 和指示 Directives)

....................................

26

7.3.4特定厂家的时间约束文件

..........................................

26

7.3.2黑盒时间约束

...................................................

23

7.3.1通用时间约束

...................................................

23

7.3HDL源代码中的约束

.................................................

22

7.2Verilog对象表示语法

.................................................

22

7.1书写约束文件的一些规则

.............................................

22

7时间约束

..............................................................

22

6.4运行script文件

......................................................

21

6.3.4自底向上的综合示例

.............................................

19

6.3.3设置控制选项及约束示例

.........................................

19

6.3.2运行多个频率要求 并存为不同的log 文件

...........................

18

6.3.1运行一个script 文件针对多个目标器件进行综合

........................

18

6.3Tcl 格式的script文件示例

..............................................

18

6.2.4打开文件的命令

................................................

17

6.2.3控制命令

......................................................

17

6.2.2添加文件的命令

................................................

16

6.2.1工程命令

......................................................

16

6.2常用Tcl 命令说明

....................................................

16

6.1创建Tcl script 文件

...................................................

内部公开

请输入文档编号请输入文档名称 Synplify工具使用指南

2001-04-09 版权所有 侵权必究 第4页 共45页

Synplify

快速入门

关键词

Synplify synthesis 综合 Script 脚本 Tcl FPGA Verilog

摘要

本文的目的是为

Synplify

的使用提供帮助 包括三个主要内容 第一部分快速入门 介绍基

本的工作流程 第二部分

Tcl

使用指南 包括运用批处理工作文件提高工作效率 和怎样用

时间约束文件使综合结果更加成功 第三部分是一些通用的以及专门针对

Altera

和

Xilinx

器

件的综合策略

缩略语清单

SCOPE Synthesis Constrains Optimization Environmemt Tcl: Tool command language

FPGA: Field Programmable Gate Array RTL: Register Transfer Level

Online helpOct. 2000Synplicity co.Synplify User guide and

tutorial

Online helpOct. 2000Synplicity co.Synplify Reference Manual

查阅地点或渠道发布日期编号作者名称

参考资料清单

1

前言

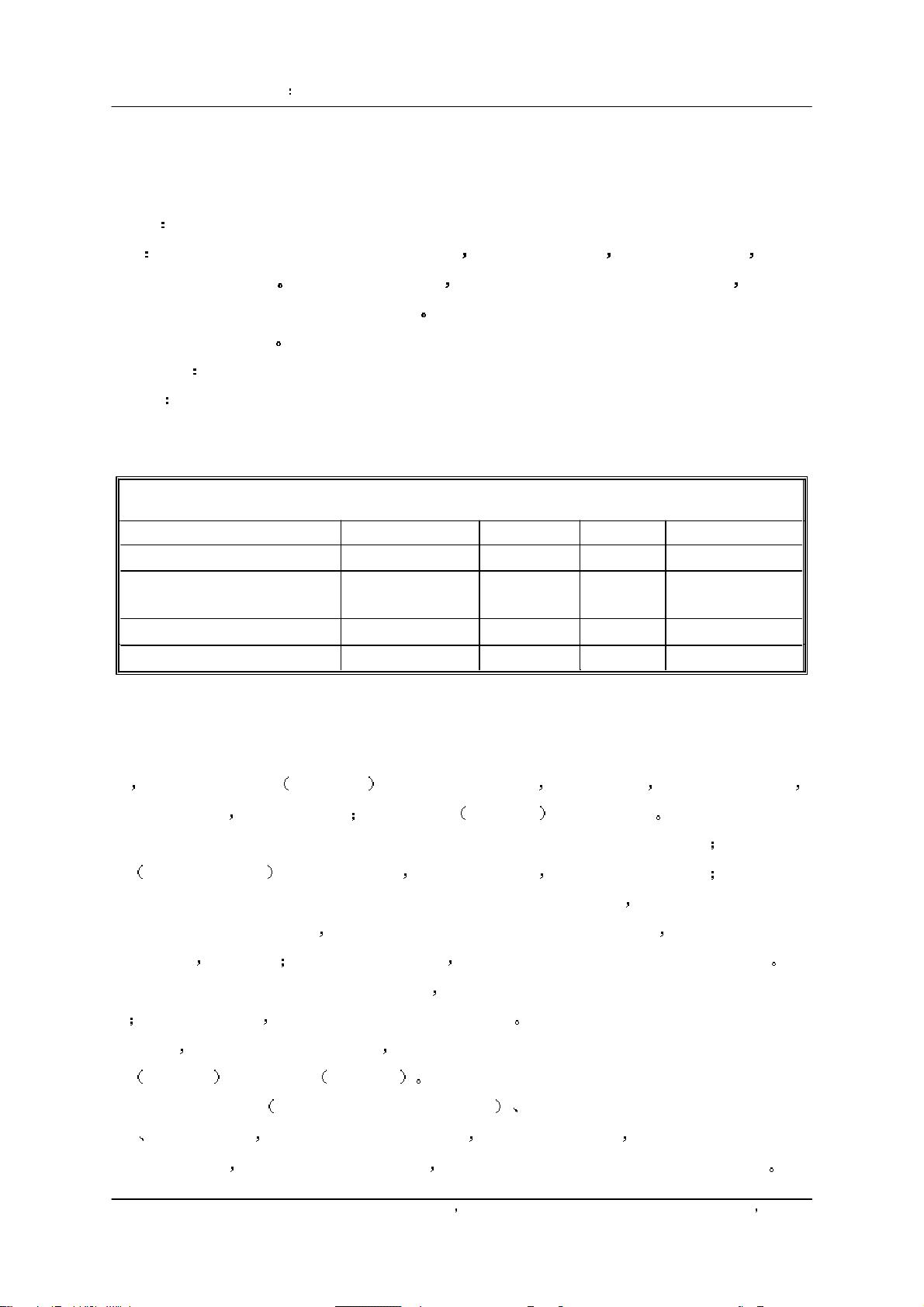

Synplify 和 Synplify Pro 是 Synplicity 公司提供的专门针对FPGA和CPLD实现的逻辑综合工

具 它支持VHDL93 IEEE1076 , 包括std_logic_1164 Numeric_std std_logic_Usigned

std_logic_Signed std_logic_Arith 和Verilog95 IEEE1364 的可综合子集

该软件提供的Symbolic FSM Compiler 是专门支持有效状态机优化的内嵌工具 SCOPE是管

理 包括输入和查看 设计约束与属性 提供活页式分类 非常友好的表格界面 用于文本输

入的HDL语法 敏感编辑窗口不仅提供了对综合错误的高亮显示 结合图形化的分析和

cross_probe工具HDL Analyst 可以把源代码与综合的结果有机地链接起来 帮助设计者迅速定

位关键路径 解决问题 其提供的命令行界面 可以通过使用Tcl脚本极大的提高工作效率

Synplify Pro还增加提供了FSM Explorer 可以在尝试不同的状态机优化方案后选定最佳结

果 以及FSM viewer 用于查看状态机的详细迁移状况

此外 为了获得最佳的综合效果 Synplify还针对具体的厂家器件提供了较为丰富的综合属

性 Attributes 和综合说明 Directives

Synplify支持PC WIN98/WIN2000/WIN NT 4.0 Sun (Sun OS 5.6 and 5.7/Solaris 2.6 and

2.7) HP-UX 10.20 后文内容中3.1节针对PC版 其余章节所述内容 因为PC版本与工作站版

本并无太大区别 因此均以工作站版本为例 如使用PC版本则可参照工作站版本相应部分

内部公开

请输入文档编号请输入文档名称 Synplify工具使用指南

2001-04-09 版权所有 侵权必究 第5页 共45页