没有合适的资源?快使用搜索试试~ 我知道了~

SAA7114数据手册

需积分: 10 0 下载量 57 浏览量

2018-11-27

15:49:05

上传

评论

收藏 583KB PDF 举报

温馨提示

试读

140页

SAA7114数据手册

资源推荐

资源详情

资源评论

DATA SHEET

Preliminary specification

File under Integrated Circuits, IC22

2000 Mar 15

INTEGRATED CIRCUITS

SAA7114H

PAL/NTSC/SECAM video decoder

with adaptive PAL/NTSC comb

filter, VBI-data slicer and high

performance scaler

2000 Mar 15 2

Philips Semiconductors Preliminary specification

PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC

comb filter, VBI-data slicer and high performance scaler

SAA7114H

CONTENTS

1 FEATURES

1.1 Video decoder

1.2 Video scaler

1.3 Vertical Blanking Interval (VBI) data decoder

and slicer

1.4 Audio clock generation

1.5 Digital I/O interfaces

1.6 Miscellaneous

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 QUICK REFERENCE DATA

5 ORDERING INFORMATION

6 BLOCK DIAGRAM

7 PINNING

8 FUNCTIONAL DESCRIPTION

8.1 Decoder

8.2 Decoder output formatter

8.3 Scaler

8.4 VBI-data decoder and capture

(subaddresses 40H to 7FH)

8.5 Image port output formatter

(subaddresses 84H to 87H)

8.6 Audio clock generation

(subaddresses 30H to 3FH)

9 INPUT/OUTPUT INTERFACES AND PORTS

9.1 Analog terminals

9.2 Audio clock signals

9.3 Clock and real-time synchronization signals

9.4 Video expansion port (X-port)

9.5 Image port (I-port)

9.6 Host port for 16-bit extension of video data I/O

(H-port)

9.7 Basic input and output timing diagrams I-port

and X-port

10 BOUNDARY SCAN TEST

10.1 Initialization of boundary scan circuit

10.2 Device identification codes

11 LIMITING VALUES

12 THERMAL CHARACTERISTICS

13 CHARACTERISTICS

14 APPLICATION INFORMATION

15 I

2

C-BUS DESCRIPTION

15.1 I

2

C-bus format

15.2 I

2

C-bus details

15.3 Programming register audio clock generation

15.4 Programming register VBI-data slicer

15.5 Programming register interfaces and scaler

part

16 PROGRAMMING START SET-UP

16.1 Decoder part

16.2 Audio clock generation part

16.3 Data slicer and data type control part

16.4 Scaler and interfaces

17 PACKAGE OUTLINE

18 SOLDERING

18.1 Introduction to soldering surface mount

packages

18.2 Reflow soldering

18.3 Wave soldering

18.4 Manual soldering

18.5 Suitability of surface mount IC packages for

wave and reflow soldering methods

19 DEFINITIONS

20 LIFE SUPPORT APPLICATIONS

21 PURCHASE OF PHILIPS I

2

C COMPONENTS

2000 Mar 15 3

Philips Semiconductors Preliminary specification

PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC

comb filter, VBI-data slicer and high performance scaler

SAA7114H

1 FEATURES

1.1 Video decoder

• Six analog inputs, internal analog source selectors, e.g.

6 × CVBS or (2 × Y/C and 2 × CVBS) or (1 × Y/C and

4 × CVBS)

• Two analog preprocessing channels in differential

CMOS style inclusive built-in analog anti-alias filters

• Fully programmable static gain or Automatic Gain

Control (AGC) for the selected CVBS or Y/C channel

• Automatic Clamp Control (ACC) for CVBS, Y and C

• Switchable white peak control

• Two 9-bit video CMOS Analog-to-Digital Converters

(ADCs), digitized CVBS or Y/C signals are available on

the expansion port

• On-chip line-locked clock generation according

“ITU 601”

• Digital PLL for synchronization and clock generation

from all standards and non-standard video sources e.g.

consumer grade VTR

• Requires only one crystal (32.11 or 24.576 MHz) for all

standards

• Horizontal and vertical sync detection

• Automatic detection of 50 and 60 Hz field frequency,

and automatic switching between PAL and NTSC

standards

• Luminance and chrominance signal processing for

PAL BGDHIN, combination PAL N, PAL M, NTSC M,

NTSC-Japan, NTSC 4.43 and SECAM

• Adaptive 2/4-line comb filter for two dimensional

chrominance/luminance separation

– Increased luminance and chrominance bandwidth for

all PAL and NTSC standards

– Reduced cross colour and cross luminance artefacts

• PAL delay line for correcting PAL phase errors

• Independent Brightness Contrast Saturation (BCS)

adjustment for decoder part

• User programmable sharpness control

• Independent gain and offset adjustment for raw data

path.

1.2 Video scaler

• Horizontal and vertical down-scaling and up-scaling to

randomly sized windows

• Horizontal and vertical scaling range: variable zoom to

1

⁄

64

(icon); it should be noted that the H and V zoom are

restricted by the transfer data rates

• Anti-alias and accumulating filter for horizontal scaling

• Vertical scaling with linear phase interpolation and

accumulating filter for anti-aliasing (6-bit phase

accuracy)

• Horizontal phase correct up and down scaling for

improved signal quality of scaled data, especially for

compression and video phone applications, with 6-bit

phase accuracy (1.2 ns step width)

• Two independent programming sets for scaler part, to

define two ‘ranges’ per field or sequences over frames

• Fieldwise switching between decoder part and

expansion port (X-port) input

• Brightness, contrast and saturation controls for scaled

outputs.

1.3 Vertical Blanking Interval (VBI) data decoder

and slicer

• Versatile VBI-data decoder, slicer, clock regeneration

and byte synchronization e.g. for World Standard

Teletext (WST), North-American Broadcast Text

System (NABTS), close caption, Wide Screen Signalling

(WSS) etc.

1.4 Audio clock generation

• Generation of a field locked audio master clock to

support a constant number of audio clocks per video

field

• Generation of an audio serial and left/right (channel)

clock signal.

2000 Mar 15 4

Philips Semiconductors Preliminary specification

PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC

comb filter, VBI-data slicer and high performance scaler

SAA7114H

1.5 Digital I/O interfaces

• Real-time signal port (R port), inclusive continuous

line-locked reference clock and real-time status

information supporting RTC level 3.1 (refer to external

document

“RTC Functional Specification”

for details)

• Bi-directional expansion port (X-port) with half duplex

functionality (D1), 8-bit YUV

– Output from decoder part, real-time and unscaled

– Input to scaler part, e.g. video from MPEG decoder

(extension to 16-bit possible)

• Video image port (I-port) configurable for 8-bit data

(extension to 16-bit possible) in master mode (own

clock), or slave mode (external clock), with auxiliary

timing and hand shake signals

• Discontinuous data streams supported

• 32-word × 4-byte FIFO register for video output data

• 28-word × 4-byte FIFO register for decoded VBI output

data

• Scaled 4:2:2, 4:1:1, 4:2:0, 4:1:0 YUV output

• Scaled 8-bit luminance only and raw CVBS data output

• Sliced, decoded VBI-data output.

1.6 Miscellaneous

• Power-on control

• 5 V tolerant digital inputs and I/O ports

• Software controlled power saving standby modes

supported

• Programming via serial I

2

C-bus, full read-back ability by

an external controller, bit rate up to 400 kbits/s

• Boundary scan test circuit complies with the

“IEEE Std.

1149.b1 - 1994”

.

2 APPLICATIONS

• Desktop video

• Multimedia

• Digital television

• Image processing

• Video phone applications.

3 GENERAL DESCRIPTION

The SAA7114H is a video capture device for applications

at the image port of VGA controllers.

The SAA7114H is a combination of a two-channel analog

preprocessing circuit including source selection,

anti-aliasing filter and ADC, an automatic clamp and gain

control, a Clock Generation Circuit (CGC), a digital

multi-standard decoder containing two-dimensional

chrominance/luminance separation by an adaptive comb

filter and a high performance scaler, including variable

horizontal and vertical up and down scaling and a

brightness, contrast and saturation control circuit.

It is a highly integrated circuit for desktop video

applications. The decoder is based on the principle of

line-locked clock decoding and is able to decode the colour

of PAL, SECAM and NTSC signals into ITU 601

compatible colour component values. The SAA7114H

accepts as analog inputs CVBS or S-video (Y/C) from

TV or VCR sources, including weak and distorted signals.

An expansion port (X-port) for digital video (bi-directional

half duplex, D1 compatible) is also supported to connect to

MPEG or video phone codec. At the so called image port

(I-port) the SAA7114H supports 8 or 16-bit wide output

data with auxiliary reference data for interfacing to VGA

controllers.

The target application for SAA7114H is to capture and

scale video images, to be provided as digital video stream

through the image port of a VGA controller, for display via

VGA’s frame buffer, or for capture to system memory.

In parallel SAA7114H incorporates also provisions for

capturing the serially coded data in the vertical blanking

interval (VBI-data). Two principal functions are available:

1. To capture raw video samples, after interpolation to

the required output data rate, via the scaler

2. A versatile data slicer (data recovery) unit.

SAA7114H incorporates also a field locked audio clock

generation. This function ensures that there is always the

same number of audio samples associated with a field, or

a set of fields. This prevents the loss of synchronization

between video and audio, during capture or playback.

The circuit is I

2

C-bus controlled (full write/read capability

for all programming registers, bit rate up to 400 kbits/s).

2000 Mar 15 5

Philips Semiconductors Preliminary specification

PAL/NTSC/SECAM video decoder with adaptive PAL/NTSC

comb filter, VBI-data slicer and high performance scaler

SAA7114H

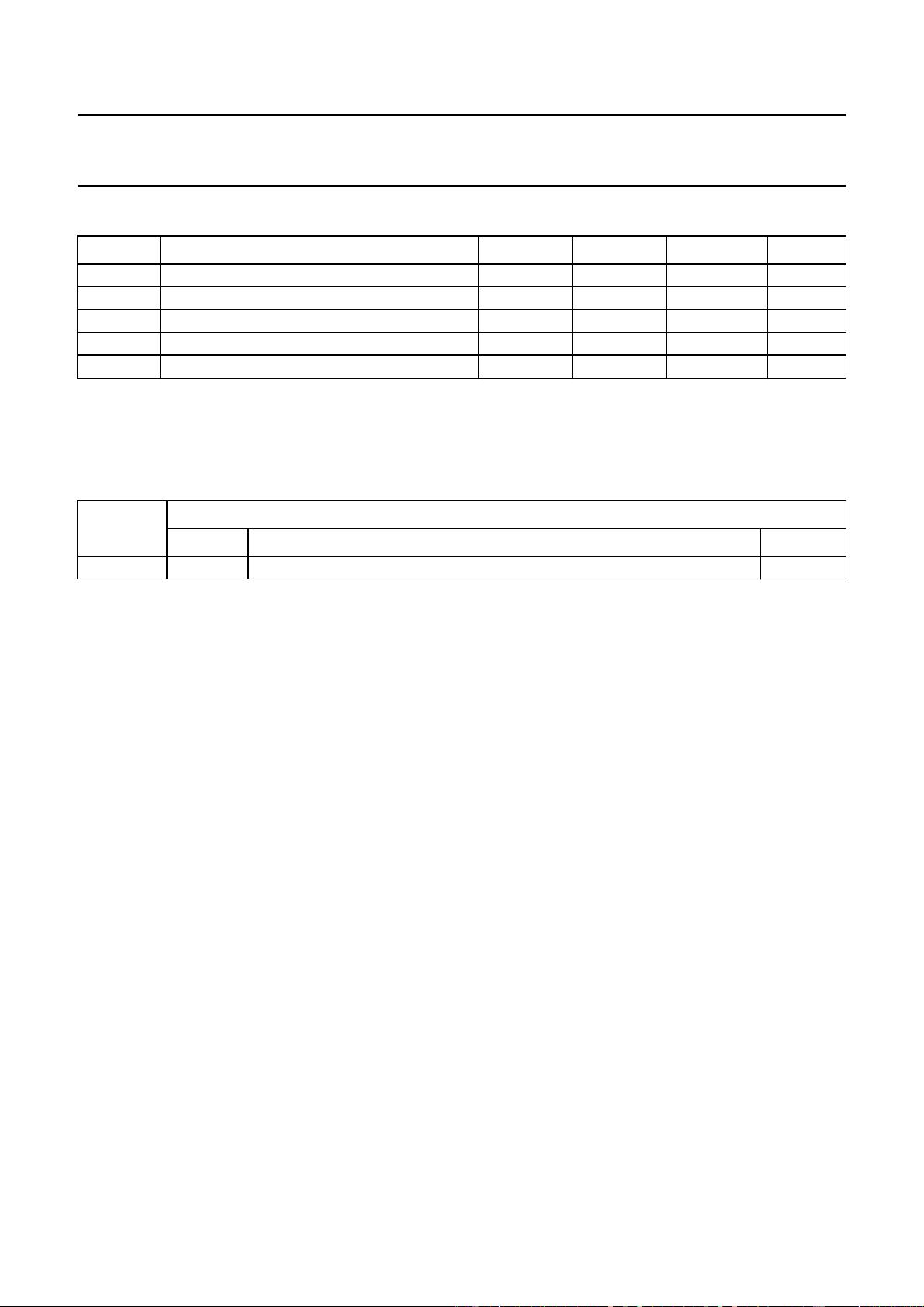

4 QUICK REFERENCE DATA

Note

1. Power dissipation is measured in CVBS input mode (only one ADC active) and 8-bit image port output mode,

expansion port is 3-stated.

5 ORDERING INFORMATION

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DDD

digital supply voltage 3.0 3.3 3.6 V

V

DDDC

digital core supply voltage 3.0 3.3 3.6 V

V

DDA

analog supply voltage 3.1 3.3 3.5 V

T

amb

operating ambient temperature 0 − 70 °C

P

A+D

analog and digital power dissipation; note 1 − 0.45 − W

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

SAA7114H LQFP100 plastic low profile quad flat package; 100 leads; body 14 × 14 × 1.4 mm SOT407-1

剩余139页未读,继续阅读

资源评论

长风飘雪

- 粉丝: 2

- 资源: 47

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功