INTEGRATED CIRCUITS

TDA10023HT

Single Chip DVB-C Channel Receiver

Product Specification 2004, November 25

th

Version 1.3

Philips Semiconductors Caen

Philips Semiconductors Caen Product specification

Single Chip DVB-C Channel Receiver TDA10023HT

2004, November 25

th

Page 1/67

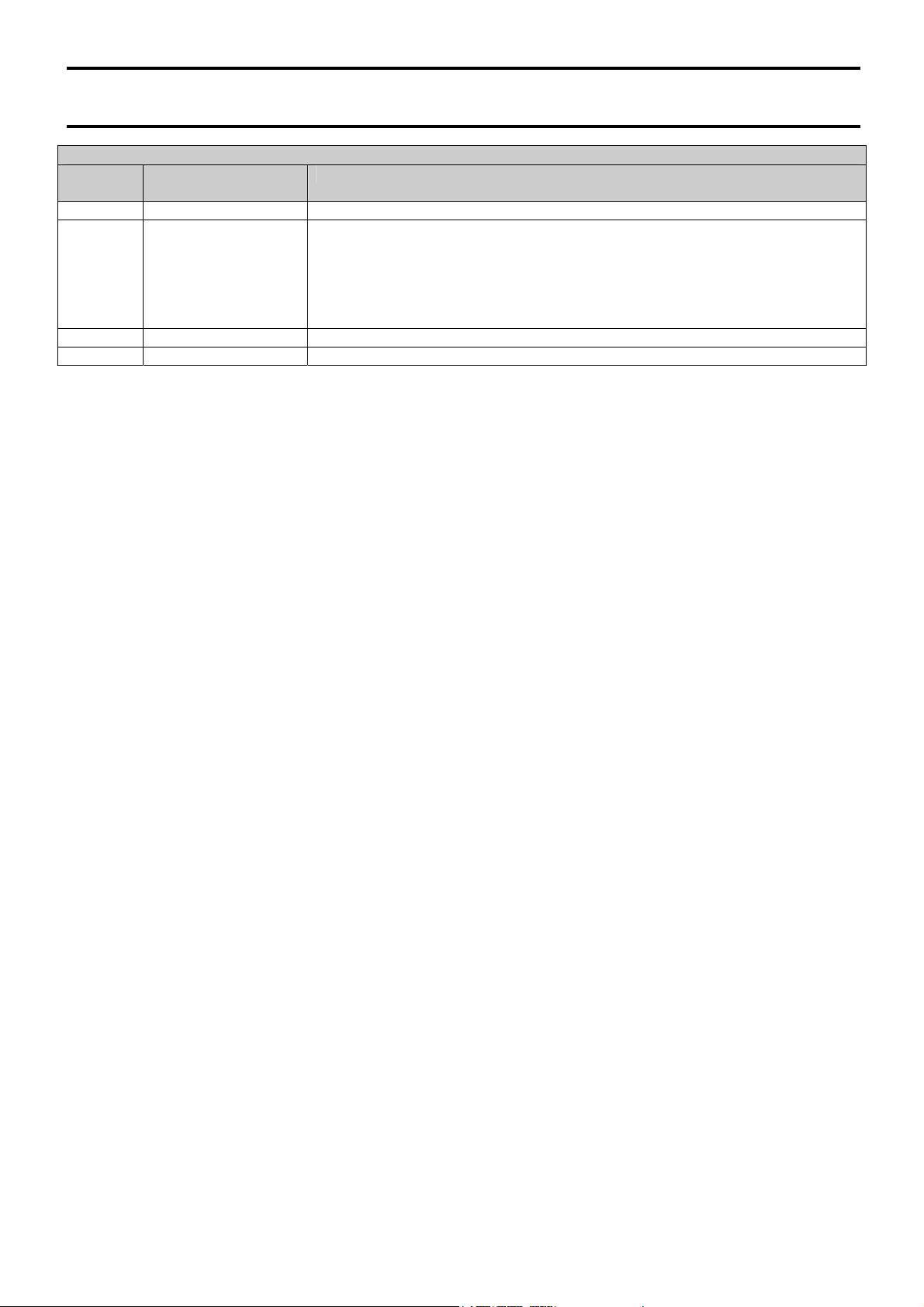

TDA10023 Data sheet revision history

Revision

number

Issued Date Observation

Rev 1.0 12 February 2003 Initial Version

Rev 1.1 6 August 2003 . The ErAgcNyq_Thd parameter has been increased by 8 to improve the

robustness of the Automatic Nyquist Gain (see p27).

. The OLDBYTECLK bit (index 1E, bit 7) has to be set to 1 (see p64).

. During the coarse timing clock recovery, the coarse symbol clock frequency

offset is available by reading the CKOFF_COARSE register (index FD) (see

p25).

Rev1.2 2004, July 1

st

Update for IC-V

Rev 1.3 2004, November 25

th

Update for IC-R

Philips Semiconductors Caen Product specification

Single Chip DVB-C Channel Receiver TDA10023HT

2004, November 25

th

Page 2/67

TABLE OF CONTENTS

1 FEATURES..............................................................................................................................................................3

2 APPLICATIONS.......................................................................................................................................................4

3 GENERAL DESCRIPTION ......................................................................................................................................5

4 QUICK REFERENCE DATA....................................................................................................................................6

5 ORDERING INFORMATION ...................................................................................................................................8

6 BLOCK DIAGRAM...................................................................................................................................................9

7 PINNING ................................................................................................................................................................10

7.1 PIN CONFIGURATION...................................................................................................................................10

7.2 INPUT – OUTPUT SIGNAL DESCRIPTION ..................................................................................................11

8 APPLICATION INFORMATION.............................................................................................................................14

8.1 GENERAL BLOCK DIAGRAM........................................................................................................................14

8.2 TYPICAL APPLICATION ................................................................................................................................15

8.3 XTAL OSCILLATOR .......................................................................................................................................16

8.4 EXTERNAL AGC CIRCUITRY........................................................................................................................16

8.5 EXTERNAL PLL AND ADC CONNECTIONS.................................................................................................17

9 FUNCTIONAL DESCRIPTION ..............................................................................................................................18

9.1 ADC.................................................................................................................................................................18

9.2 PLL ..................................................................................................................................................................19

9.3 DOWN CONVERTER .....................................................................................................................................20

9.4 DECIMATION AND ANTI-ALIASING FILTERS..............................................................................................22

9.5 INTERPOLATOR AND TIMING RECOVERY ................................................................................................24

9.6 HALF NYQUIST FILTER.................................................................................................................................25

9.7 EQUALIZER....................................................................................................................................................27

9.8 GAINS ADJUSTMENT....................................................................................................................................29

9.9 CARRIER RECOVERY...................................................................................................................................30

9.10 DOUBLE AUTOMATIC GAIN CONTROL ....................................................................................................33

9.11 GENERAL PURPOSE REGISTERS ............................................................................................................35

9.12 INTERRUPT LINE.........................................................................................................................................39

9.13 DVB FORWARD ERROR CORRECTION....................................................................................................40

9.13.1 DVB Frame Synchronization and De-Interleaver...................................................................................40

9.13.2 DVB Reed-Solomon Decoder ................................................................................................................42

9.13.3 DVB Descrambler...................................................................................................................................44

9.13.4 DVB MIB Counters .................................................................................................................................44

9.14 OUTPUT INTERFACE..................................................................................................................................46

9.14.1 DVB MODE : PARALLEL INTERFACE MODE A ..................................................................................47

9.14.2 DVB MODE : PARALLEL INTERFACE MODE B ..................................................................................47

9.14.3 DVB MODE : PARALLEL INTERFACE MODE C ..................................................................................48

9.14.4 DVB MODE : SERIAL INTERFACE .......................................................................................................48

10 I

2

C CONTROL.....................................................................................................................................................50

10.1 I

2

C SERIAL INTERFACE .............................................................................................................................50

10.2 I

2

C REGISTERS LIST ..................................................................................................................................51

10.3 I

2

C REGISTERS PAGE INDEX....................................................................................................................54

11 BOUNDARY SCAN TEST ...................................................................................................................................55

12 LIMITING VALUES ..............................................................................................................................................57

13 THERMAL CHARACTERISTICS ........................................................................................................................58

14 INTERNAL PIN CONFIGURATION.....................................................................................................................59

15 CHARACTERISTICS OF DIGITAL INPUTS AND OUTPUTS ............................................................................60

15.1 PROGRAMMABLE INTERFACE..................................................................................................................60

15.2 SERIAL INTERFACE ....................................................................................................................................61

16 PACKAGE OUTLINE...........................................................................................................................................62

17 SOLDERING INFORMATION .............................................................................................................................63

18 DEFINITIONS ......................................................................................................................................................64

19 LIFE SUPPORT APPLICATIONS .......................................................................................................................65

20 PURCHASE OF PHILIPS I

2

C COMPONENTS ..................................................................................................66

Philips Semiconductors Caen Product specification

Single Chip DVB-C Channel Receiver TDA10023HT

2004, November 25

th

Page 3/67

1 FEATURES

• 4/16/32/64/128/256 QAM demodulator (ITU-T J.83 annex A and C compatible).

• High performance for 256 QAM especially for direct IF applications.

• On chip 10-bit ADC.

• On chip PLL for crystal frequency multiplication (Typically 16MHz crystal).

• Digital down conversion.

• Half Nyquist filter (roll off = 0.15).

• Two PWM AGC outputs with programmable take over point (For Tuner and Downconverter Control).

• Clock timing recovery, with programmable second order loop filter.

• Variable symbol rate capability from SACLK/64 to SACLK/4 (with low sampling clock : SACLK max = 36

MHz) or from SACLK/128 to SACLK/8 (with high sampling clock : SACLK max = 72 MHz).

• Programmable anti-aliasing filters.

• Full digital carrier recovery loop.

• Carrier acquisition range up to 9% of symbol rate.

• Integrated adaptative equalizer (Linear Transversal Equalizer or Decision Feedback Equalizer).

• DVB compatible differential decoding and mapping.

•

On chip DVB-C full compliant FEC decoder (Deinterleaver, RS decoder, Descrambleur).

•

Multiple TS JQAM Filter.

• Parallel and Serial transport stream interface simultaneously.

• I

2

C bus interface, for easy control.

Philips Semiconductors Caen Product specification

Single Chip DVB-C Channel Receiver TDA10023HT

2004, November 25

th

Page 4/67

2 APPLICATIONS

• Cable Set-Top Boxes.

• Cable Modems.

• Cable NIMs.

• MMDS (ETS 300-749) Set-Top Boxes.

评论5

最新资源