收集整理自开源 IP 通吃岛 http://www.socvista.com/bbs

verilog 十大基本功

SOCvista 的版主 dancia 最近对国内的主要 EDA 论坛做了一项调查,耗时一个多月,经过仔细的总结,发现一个有趣的

现象:国内关于 HDL 提出问题的帖子,有 80%都集中在一小部分基本问题上。同样的一个问题,从 5 年前开始就有

人问起,一直问到今天,很可能还会持续到 N 年后。貌似新人们总也避不开这些说 难其实也不难的问题,而且实际的

调查还发现,就连好多工作多年的工程师们对这些问题也是稀里糊涂,似懂非懂。

为了帮助大家一劳永逸解决这些基本难题,从而迈向自由编程的康庄大道,我们特地开辟了这个版块,要把这些基本

功一一传授给大家。如果觉得我们的帖子还不过瘾,你可以回帖继续提问,务必把所有概念搞清搞懂。

另外所谓十项只是一个概述,请勿过分计较。

谢谢大家的关注和支持。

原帖见:dancia《高手也搞不清楚的十项基本功》

http://www.socvista.com/bbs/search.php?searchid=11&orderby=lastpost&ascdesc=desc&searchsubmit=yes

以下是大家讨论的一个总结:

1、阻塞赋值与非阻塞赋值

前言:阻塞与非阻塞赋值是 Verilog 语言中最基本的部分,也是让大部分 Verilog 新手最困惑的地方。

关于阻塞与非阻塞的著作文章可谓汗牛充栋,这些文章对阻塞与非阻塞赋值的原理进行了非常详细的讲

解,但新手读了之后依然有种似懂非懂的感觉,编码过程中一如既往的犯错。所以,本文的目的立足于

提供一种实用化的解决方案,用最简单的语言和形象的类比让新手能够一目了然的明白正确的编码方式

以及相应的电路行为逻辑,关于仿真细节的讲解不是本文重点,需要了解更多细节的朋友可以参考文后

列举的参考文献。

本文共分为三部分,第一部分是正确使用阻塞与非阻塞赋值的基本原则。第二部分是阻塞与非阻塞赋值

对应电路的行为逻辑。第三部分是阻塞与非阻塞赋值的原理简介。

Golden Rule

编码原则很多,就阻塞非阻塞赋值而言,新手最需要牢记的是其中三条:

1、时序逻辑一定用非阻塞赋值”<=”,一旦看到敏感列表有 posedge 就用”<=”。

2、组合逻辑一定用”=”,一旦敏感列表没有 posedge 就用”=”,一旦看到 assign 就用”=”。

3、时序逻辑和组合逻辑分成不同的模块,即一个 always 模块里面只能出现非阻塞赋值”<=”或者”=”。如

果发现两种赋值并存,一个字”改”,心存侥幸可能会给后续工作带来更多麻烦。

以上三条,对新手而言不必追求为什么,需要的就是条件反射的照章办事。最后说一句,新手可能记不

住哪个符号是阻塞赋值,哪个是非阻塞赋值,大家可以数数,”非阻塞赋值”一共 5 个字,“阻塞赋值“4

个字,所以非阻塞用的符号”<=”比阻塞赋值用的符号”=”长。

电路行为逻辑。

第一节给出了三条最基本的编码原则,有个朋友可能会想,按照这三条编码原则写出来的代码会按怎样

的逻辑工作呢?这一节就是回答这个问题。

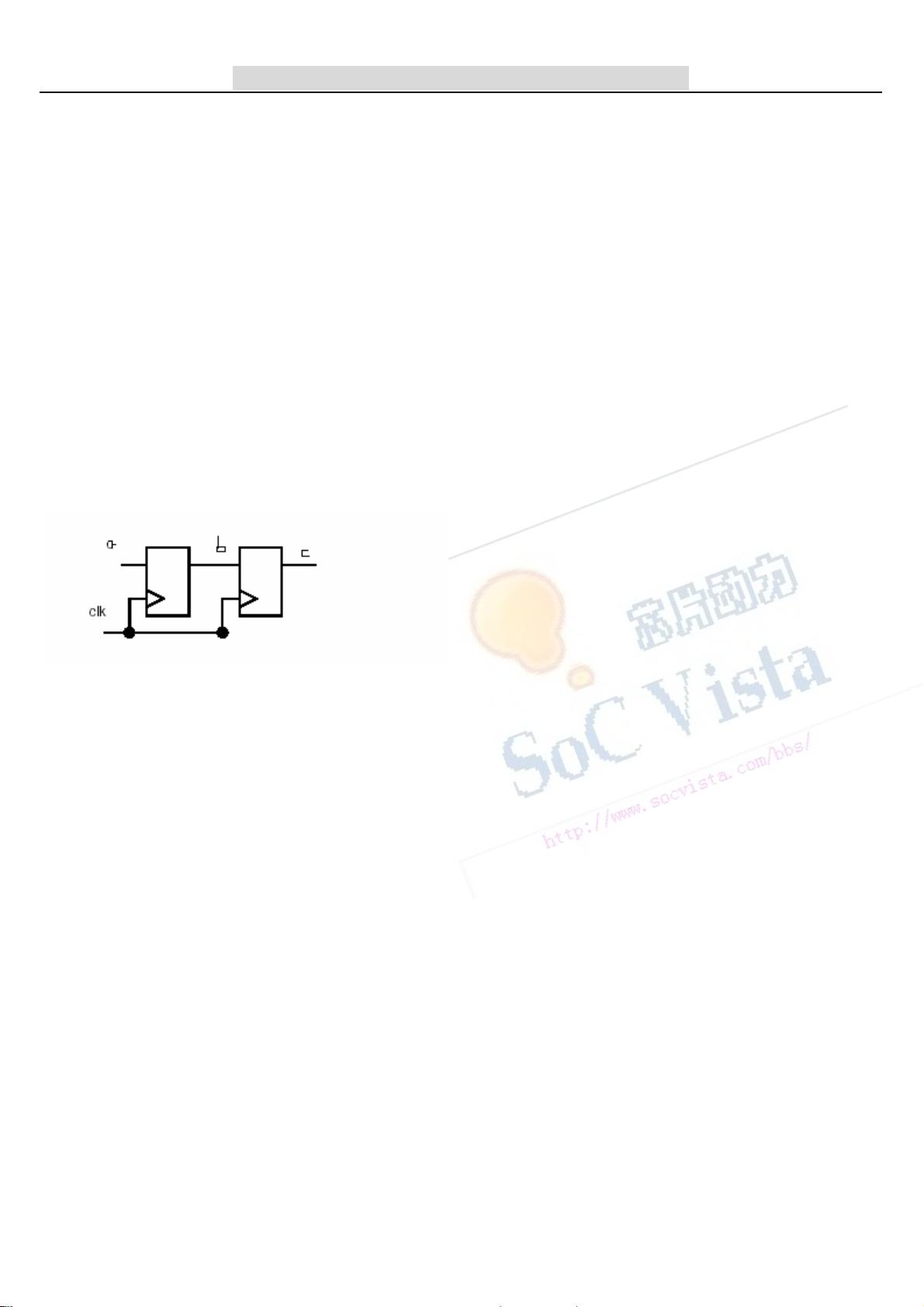

首先解释一下阻塞赋值与非阻塞赋值的含义。所谓的阻塞赋值”=”就是说,在这个语句没有执行完之前,

后面的语句是不执行的。这里执行的含义是指完成变量值的更新。非阻塞赋值”<=”是指,所有的语句可

以并发执行,而前面的值是否执行完毕不会影响后面的语句,换句话说,语句的顺序是无关紧要的。

SOC vista