没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Zynq-7000 All

Programmable SoC

Software Developers Guide

UG821 (v12.0) September 30, 2015

Zynq-7000 AP SoC SWDG www.xilinx.com 2

UG821 (v12.0) September 30, 2015

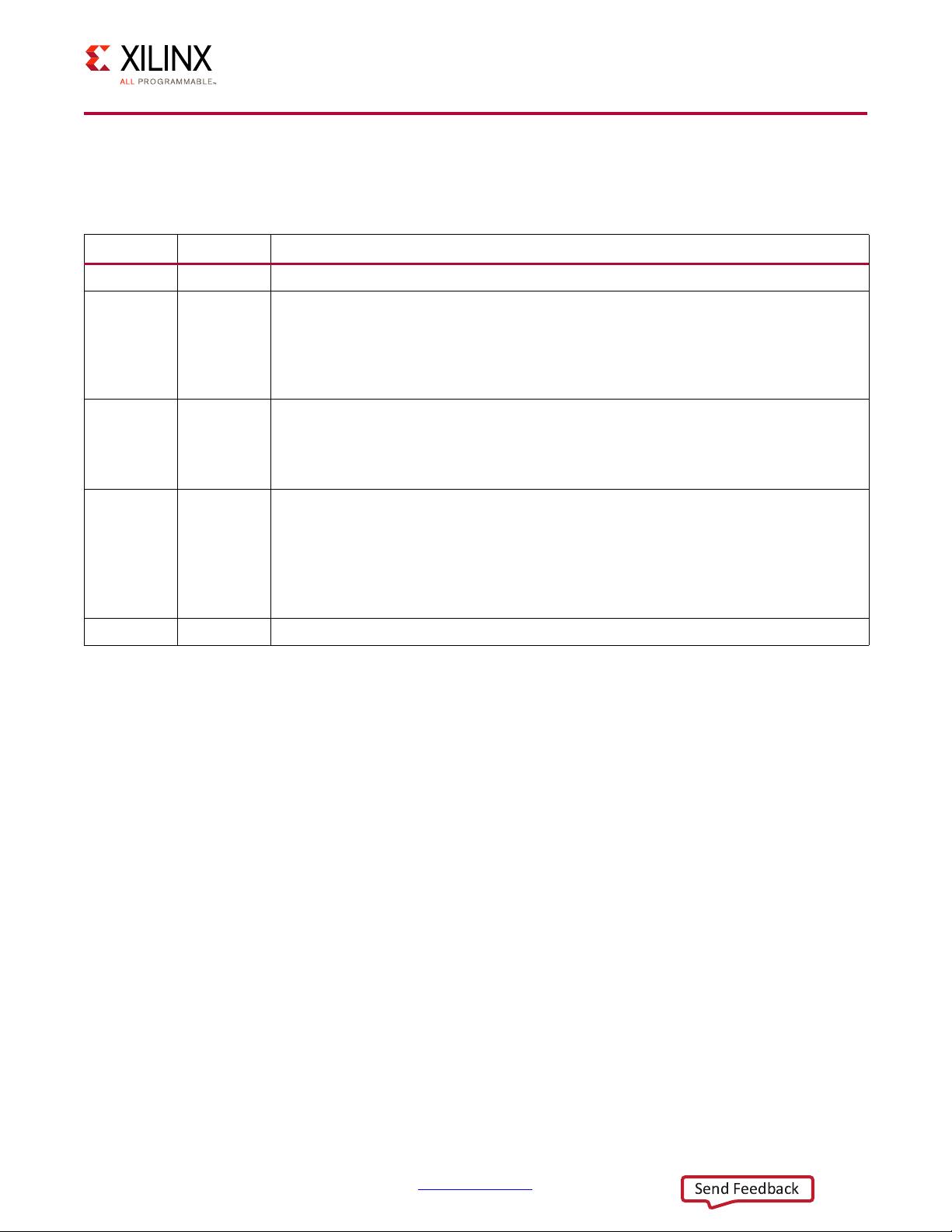

Revision History

The following table shows the revision history for this document.

Date Version Revision

09/30/2015 12.0

Removed LibXil SKey and LibXil RSA. Added references to the library locations.

06/24/2015 11.0

Updated Appendix B, LibXil SKey for Zynq-7000 AP SoC Devices (v2.1).

Changed Vivado Device Programmer to Vivado hardware manager.

Changed Platform Reference Manual reference to Generating Software Platforms

(UG1138)

Updated Bootgen options to match -h in Vivado Tcl Console in Table A-3.

04/01/2015 10.1

Added miscellaneous references throughout the document.

Updated BIF File Attributes.

Added Bootgen Command Options.

Updated Partition Attribute Bits.

06/04/2014 9.0

Updated Bootgen to remove the -i option in Bootgen Command Options.

Throughout document, added cross-references and updated links in Appendix D,

Additional Resources and Legal Notices.

Added definitions for RSA and SHA-2.

Removed reference to UG652.

Changed AP to PS on page 23.

04/02/2014 8.0

Initial release for 2014.1.

Send Feedback

Zynq-7000 AP SoC SWDG www.xilinx.com 3

UG821 (v12.0) September 30, 2015

Table of Contents

Chapter 1: Introduction to Programming with Zynq-7000 AP SoC Devices

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Architectural Decisions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Operating System (OS) Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 2: Software Application Development Flows

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Software Tools Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Bare-Metal Device Driver Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Bare-Metal Application Development . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Linux Application Development . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Additional Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Chapter 3: Boot and Configuration

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Boot Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Boot Stages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Boot Image Creation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

BootROM Header Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Chapter 4: Linux

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Git Server and Gitk Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Linux BSP Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

U-Boot. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Appendix A: Using Bootgen

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

BIF File Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Initialization Pairs and the INT File Attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Encryption Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Authentication Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Send Feedback

Zynq-7000 AP SoC SWDG www.xilinx.com 4

UG821 (v12.0) September 30, 2015

Bootgen Command Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Image Header Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Partition Header Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Partition Attribute Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Image Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Appendix B: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Send Feedback

Zynq-7000 AP SoC SWDG www.xilinx.com 5

UG821 (v12.0) September 30, 2015

Chapter 1

Introduction to Programming with

Zynq-7000 AP SoC Devices

Overview

This document summarizes the software-centric information required for designing with

Xilinx

®

Zynq

®

-7000 All Programmable SoC devices. It assumes that you are:

• Experienced with embedded software design

• Familiar with ARM

®

development tools

• Familiar with Xilinx FPGA devices, intellectual property (IP cores), development tools,

and tool environments.

Introduction

The addition of extensibility of the SoC for both hardware and software programmability

imposes new requirements on design flows for both hardware and software.

Certain hardware features are unique to Xilinx, such as hardware co-simulation and

co-debug functionality that make it possible to verify custom logic implemented on

Zynq-7000 AP SoC devices or in a logic simulation environment while applications execute

on a Zynq-7000 AP SoC processor on a physical board or an emulator.

For a step-by-step explanation on designing a Zynq-based embedded system, see the

following documents:

• Vivado Design Suite Tutorial: Embedded Processor Hardware Design (UG940) [Ref 6]

• Vivado Design Suite User Guide: Embedded Processor Hardware Design (UG898) [Ref 5]

• Vivado Design Suite Tutorial: Zynq-7000 All Programmable SoC Embedded Design

(UG1165)

[Ref 16]

VIDEO: See Enabling Smarter Systems for quick-take videos on the Zynq-7000 AP SoC devices.

Send Feedback

剩余67页未读,继续阅读

资源评论

hazhanggavin

- 粉丝: 28

- 资源: 19

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- predict.ipynb

- 软件开发:C++技术实现KTV点歌系统设计与交互体验

- PCF8591T芯片DA实验_单片机C语言实例(纯C语言源代码).zip

- [学校班级]FI同学录ficlass 1.1.2_ficlass112.rar

- [信息办公]BugFree1.0正式版_bugfree10.rar

- 软件消抖的独立式键盘输入实验_单片机C语言实例(纯C语言源代码).zip

- 基于DIT的FFT的实现-课程设计.doc

- UCI常用数据集,UCI常用数据集,UCI常用数据集

- [主机域名]Sofee米表程序_sofeedomainnameportfolio_v101.rar

- [Android实例] Android 竖着的SeekBar.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功