计算机原理讲义

半导体存储器

第五章 半导体存储器

计算机原理讲义

存储器基本知识

第 4.1 节 存储器基本知识

存储器是存储信息的部件,正因为有了存储器,计算机才有信息记忆功能

一 . 存储器按位置分类

1. 内部存储器 —— 通常与系统总线相连, CPU 可直接访问,简称内存

1 )内部 CACHE :在 CPU 内作为一个高速的指令或数据缓冲区

2 )外部 CACHE :通常在主板上,介于内部 CACHE 和主存之间的缓冲区

3 )主存储器:内存主要使用的空间

内存速度快,通常由半导体存储器组成,工艺采用双极性 TTL 或 MOS 技

术

内存包括 RAM 和 ROM 两部分, RAM 占主要,通常说内存主要指 RAM ,

而 ROM 主要用于存放 BIOS

2. 外部存储器——通常是通过专用驱动设备才能访问,简称外存

速度比内存慢,容量大、掉电信息不丢,如磁盘(软盘、硬盘)、光盘

计算机原理讲义

存储器基本知识

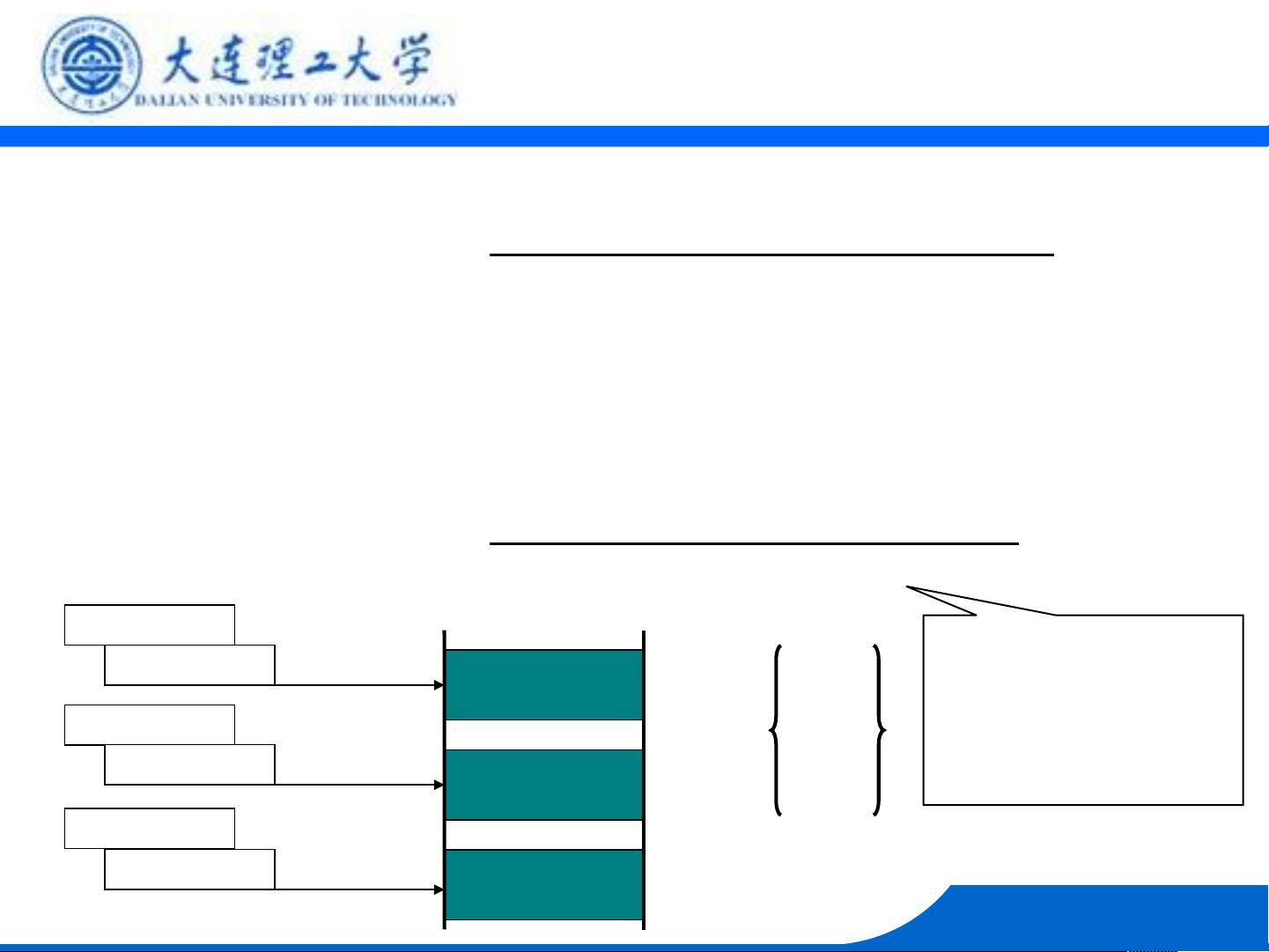

二 . 内存的行列结构

为区分不同存储单元,每个单元都对应一个地址,读写访问

时,应给出相应地址,经过译码后,选中具体存储单元。为简化译码电

路,内存中存储单元按照多行多列的矩阵形式来排列。

例:组成 1KB 的内存

1 )若不按矩阵形式排列,而是一字排开,则需要 1024 根译码线

2 )若按 32×32 的矩阵形式排列,则只需要 5 根行选择线和 5 根列选

择线

0-0

31-3131-0

0-31

…

…

…

…

行

译

码

列译码和 I/O 控制

X0

X31

…

Y0

Y31

A0

A1

A2

A3

A4

A5

A6 A7 A8 A9

…

R / W

/CE

数据输入

数据输出

A4~A0 行地址信号 用 RAS 表

示

(Row Address Signal)

A9~A5 列地址信号 用 CAS 表

示

(Column Address Signal)

X31~X0 行选择信号

Y31~Y0 列选择信号

计算机原理讲义

存储器基本知识

三 . 随机读写存储器—— RAM (Random Access Memory)

RAM 既可读又可写,掉电信息丢失,按结构又可分为 SRAM 和 DRAM

1. 静态 RAM —— SRAM ( static RAM )

使用双稳态触发器存储信息,速度快,不需要刷新,但容量低、功耗

大

计算机中 CACHE 常使用 SDRAM 如: 6264 8k * 8 62256 64

K * 8

D0

D0

Yi

Xi

Vcc

T3

T4

T5

T6

T1

T2

T7

T8

① T1,T2 为开关管, T3,T4 为负载管,导通

电阻 r3,r4>>r1,r2 。 T1T3 和 T2T4 构成

两个反向器按正反馈连接,构成触发器

② Xi 高电平, T5,T6 及其他与 Xi 相联的开

关管导通,每一单元与数据线相连。 Yi

为高电平, T7,T8 导通,此时仅有 XiYi

单元与外部数据线连通,可对该单元进行

读写

计算机原理讲义

存储器基本知识

2. 动态 RAM —— DRAM ( dynamic RAM )

使用电容存储信息,充电状态和放电状态分别表示 1 和 0 ,因

电容有漏电,因此需要对动态 RAM 进行定时刷新。计算机中的主存条

多以 DRAM 为主。

※

DRAM 的刷新

DRAM 的一次刷新过程就是对存储器进行一次读取、放大和再写入,

通常按行进行刷新,具体执行时,让行地址信号 /RAS 有效,将该行所

有存储单元分别读出,与放大电路接通,再写回。然后再给出下一行的 /

RAS 信号,重复操作。

通常每一行的刷新时间间隔不应超过 2ms ,实际应用时,由

专用的 DRAM 控制器( Intel 8203 、 8207 、 8209 )或 DRAM 本身自

带的的片内刷新电路完成动态 RAM 的刷新。

评论0