© Copyright 2012 WIZnet Co., Inc. 版权所有. 版本. 1.0 1

文档历史信息

版本 时间 描述

V1.0 08 Oct

,

2013

© Copyright 2012 WIZnet Co., Inc. 版权所有. 版本. 1.0 1

1

简介

W5500 Evaluation Board 简称 W5500-EVB,是为了方便广大用户更好的了解、使用 W5500 这

款网络芯片所开发的评估板。该板采用了 STM32F103RCT6+W5500 的设计,基于 ARM 的 Cortex-M3

平台。

W5500 延续了之前 WIZnet 系列产品的 ToE 技术,使用硬件逻辑门电路实现 TCP/IP 协议栈的传

输层及网络层(如:TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE 等协议),并集成了数据链路层,物理

层,以及 32K 字节片上 RAM 作为数据收发缓存。从而把网络数据流量的处理工作全部转移到 W5500

集成硬件中进行。使得上位机主控芯片(此板为 STM32F103RCT6),只需承担 TCP/IP 应用层控制信

息的处理任务。从而大大节省了上位机对于数据复制、协议处理和中断处理等方面的工作量,提升了

系统利用率及可靠性。

在操作过程中,用户可以近似的将 W5500 作为 STM32F103RCT6 的一个外设 RAM 来使用,非常

简易。另外,W5500 还提供网络唤醒及掉电模式供客户选用,从而降低系统能耗。W5500 对外接口

为通用的 80MHz 高速 SPI,供不同平台拓展高速以太网方案选用。

2

特点

- 支持硬件 TCP/IP 协议:TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- 支持 8 个独立端口(Socket)同时通讯

- 支持掉电模式

- 支持网络唤醒

- 支持高速串行外设接口(SPI 模式 0,3)

- 内部 32K 字节收发缓存

- 内嵌 10BaseT/100BaseTX 以太网物理层(PHY)

- 支持自动协商(10/100-Based 全双工/半双工)

- 不支持 IP 分片

- 3.3V 工作电压,I/O 信号口 5V 耐压;

- LED 状态显示(全双工/半双工,网络连接,网络速度,活动状态)

- 48 引脚 LQFP 无铅封装(7x7mm, 0.5mm 间距)

3

规格

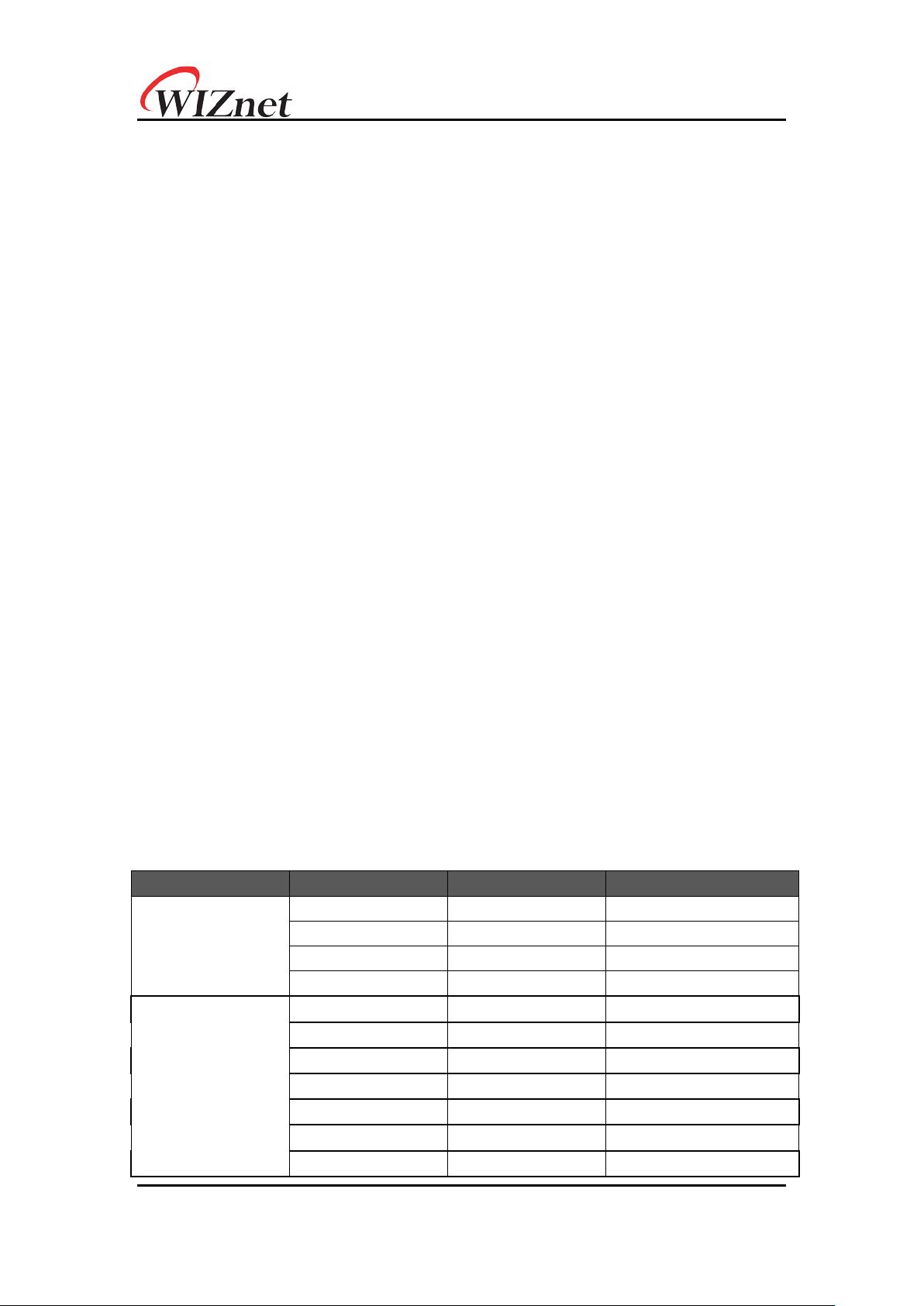

表格 1 规格

模块

器件

描述

备注

核心板

以太网核心芯片

W5500 全硬件 TCP/IP 协议栈

MCU STM32F103RCT6

EEPROM AT24C16 4K 电可擦除只读存储器

J1, J2 排针

外接引脚

2.54mm 12*2

接口板

网络变压器

B-TRC1188NLE

RJ-45

不带变压器及灯

电压转换芯片

LM1117-3.3

USB 转 RS232 芯片 FT232RL

LED 指示灯 Link,ACT,Speed

J3,J4 排针

外接引脚

2.54mm 12*2

P3 排针 J-Tag 接口 2.54mm 10*2

© Copyright 2012 WIZnet Co., Inc. 版权所有. 版本. 1.0 2

按键 直插上位按键

6 个

4

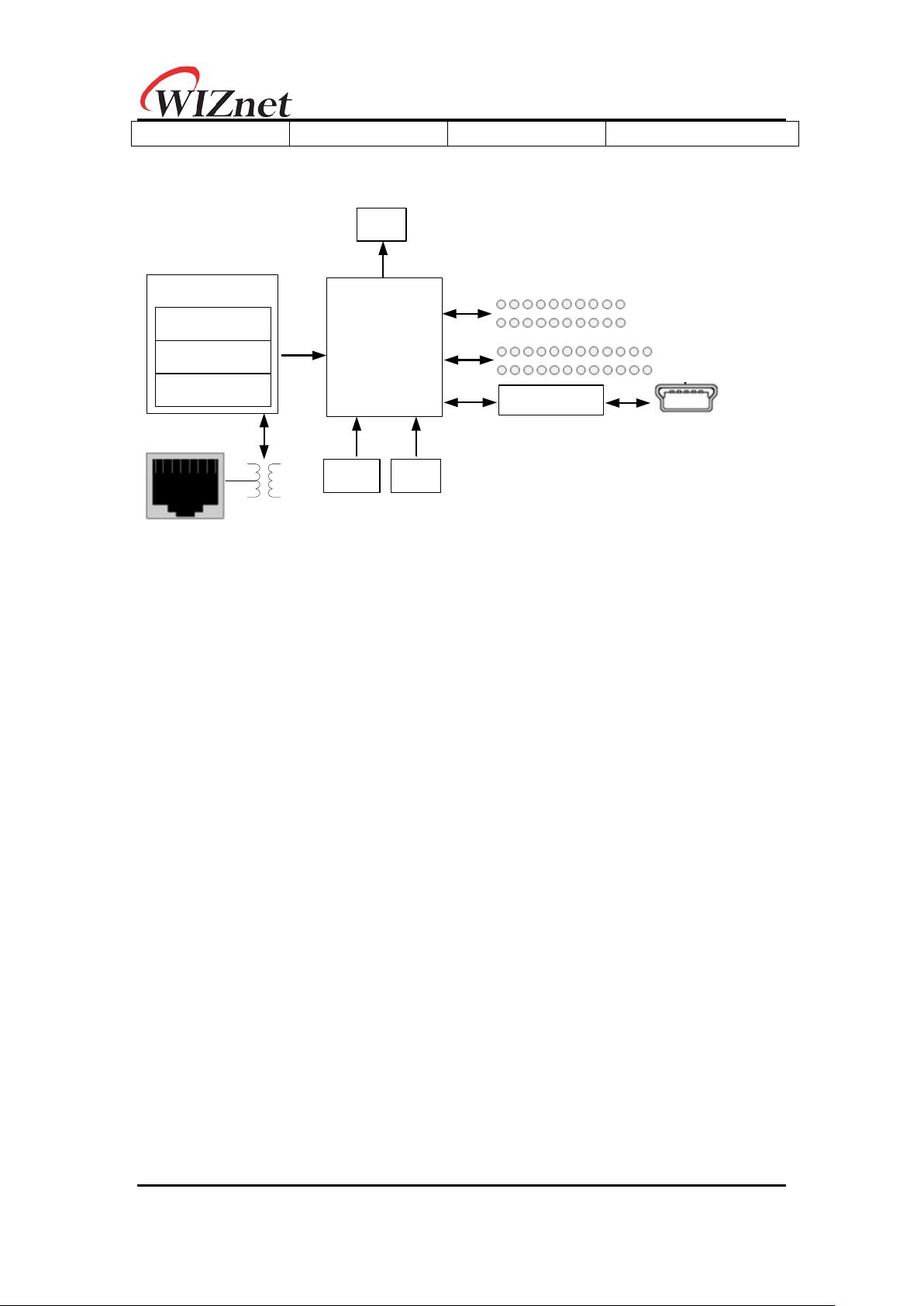

方框图

Cortex-M3

USB-to-UART

接口芯片

RESET

按键

LED

指示灯

外接引脚

RJ-45

TCP/IP Core

MAC

PHY

W5500

GPIO

UART

Mini-USB B type

(供电,数据传输,编程)

SPI

网络变压器

Boot

按键

J-Tag

调试接口

GPIO

图 1 方框图

5

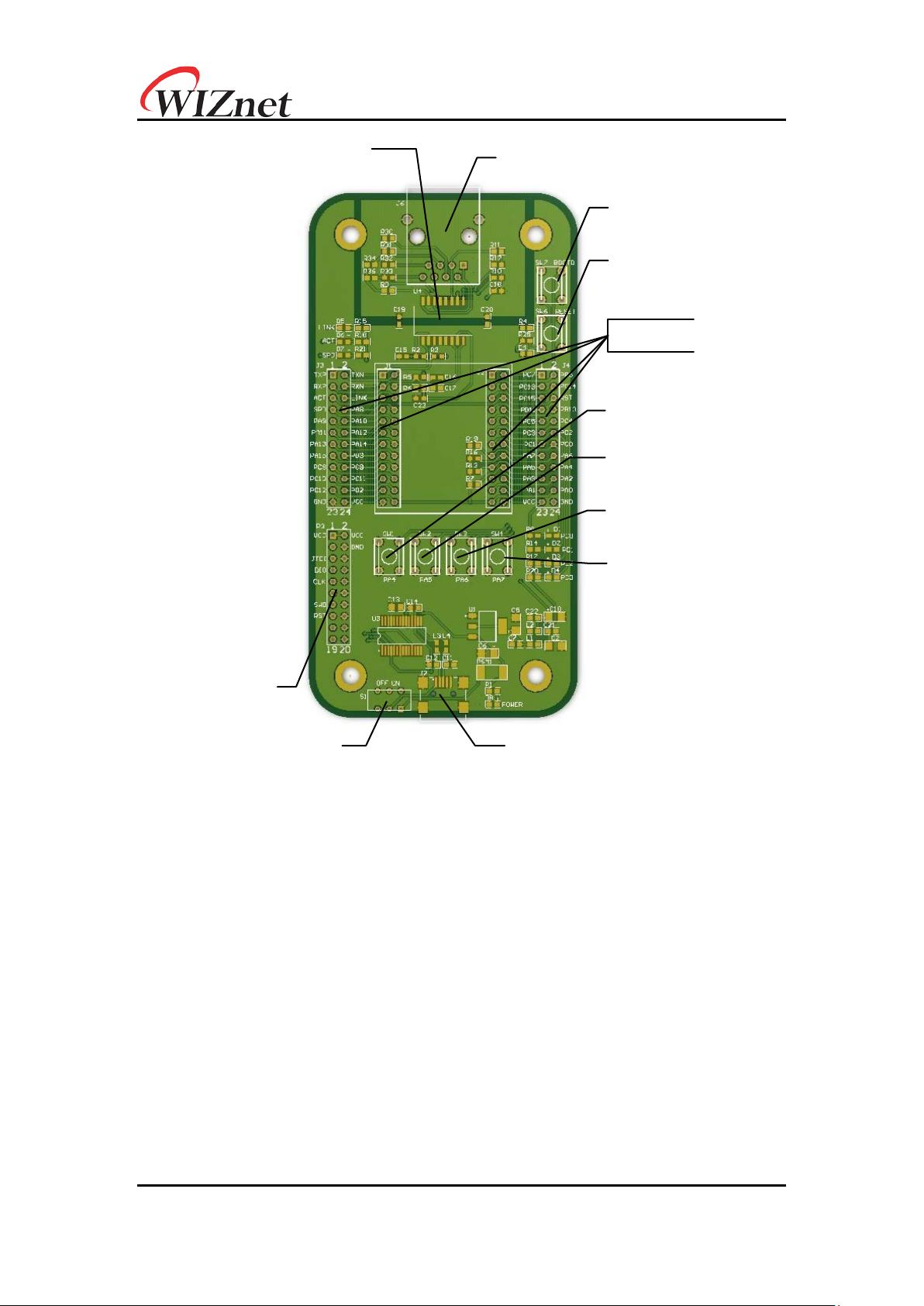

硬件布局

© Copyright 2012 WIZnet Co., Inc. 版权所有. 版本. 1.0 3

RJ-45

Boot

按键

Reset

按键

网络变压器

J-Tag

电源开关

Mini USB

外接引脚

PA4

数字输入/出

PA5

数字输入/出

PA6

数字输入/出

PA7

数字输入/出

图 2 底板布局(正面)