没有合适的资源?快使用搜索试试~ 我知道了~

单周期CPU设计实验精选报告.pdf

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 167 浏览量

2022-07-03

04:13:18

上传

评论

收藏 2.75MB PDF 举报

温馨提示

试读

16页

单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf单周期CPU设计实验精选报告.pdf

资源推荐

资源详情

资源评论

单周期 CPU 设计实验精选报告

《计算机构成原理与接口技术实验》

学 院 名 称

学 生 姓 名

学 号

专业(班级)

合 作 者

时 间

实验报告

:

:

:

:

:

: 2016 年 4 月 25 日

单周期 CPU 设计实验精选报告

成 绩 :

实 验 二 :

一. 实验目的

1.

2.

3.

4.

掌握单周期 CPU 数据通路图的构成、原理及其设计方法;

掌握单周期 CPU 的实现方法,代码实现方法;

认识和掌握指令与 CPU 的关系;

掌握测试单周期 CPU 的方法。

二.

实验内容

设计一个单周期 CPU ,该

CPU 起码能实现以下指令功能操作。

需设计的指令与格式以下:

==> 算术运算指令

( 1)add rd , rs, rt

000000

(

说明:以助记符表示,是汇编指令;

rt(5 位 ) rd(5 位 )

以代码表示,是机器指令

)

rs(5 位 )

reserved

0”。

功能: rd ← rs + rt 。 reserved 为预留部分,即未用,一般填“

( 2) addi rt , rs ,

000001

immediate

rs(5 位 ) rt(5 位) immediate (16 位 )

功能: rt ← rs + (sign-extend)

( 3) sub rd , rs , rt

000010 rs(5 位 )

immediate ; immediate

符号扩展再参加“加”运算。

rt(5 位 ) rd(5 位 )

reserved

达成功能: rd ←rs - rt

==> 逻辑运算指令

( 4) ori rt , rs ,

010000

immediate

rs(5 位 ) rt(5 位) immediate (16 位 )

功能: rt ← rs | (zero-extend)

( 5) and rd , rs , rt

010001 rs(5 位 )

immediate ; immediate

做“ 0”扩展再参加“或”运算。

rt(5 位) rd(5 位 )

reserved

功能: rd ← rs & rt

;逻辑与运算。

( 6) or rd , rs , rt

010010

==> 传递指令

( 7) move rd , rs

100000 rs(5 位 ) 00000 rd(5 位 )

reserved

rs(5 位 ) rt(5 位) rd(5 位 )

reserved

功能: rd ← rs | rt ;逻辑或运算。

功能: rd ← rs + $0

; $0=$zero=0 。

==> 储存器读 / 写指令

( 8) sw rt , immediate( rs) 写储存器

100110 rs(5 位 ) rt(5 位) immediate (16 位 )

功能: memory[rs+ (sign-extend) immediate ] ←rt ; immediate 符号扩展再相加。

单周期 CPU 设计实验精选报告

( 9) lw rt ,

100111

==> 分支指令

( 10 ) beq rs,rt,

110000

immediate (rs)

rs(5 位 )

读储存器

rt(5 位) immediate (16 位 )

immediate ] ;immediate

符号扩展再相加。

功能: rt ← memory[rs + (sign-extend)

immediate

rs(5 位 ) rt(5 位) immediate ( 位移量, 16 位 )

immediate <<2;

指令之间指令条数

。

immediate

功能: if(rs=rt) pc

特别说明: immediate

符号扩展以后左移

← pc + 4 + (sign-extend)

是从 PC+4 地址开始和转移到的

2 位再相加。为何要左移 2 位?因为跳转到的指令地址一定是 4 的倍数

(每条指令占 4 个字节),最低两位是“ 00 ”,所以将 immediate 放进指令码中的时候,是右移

了 2 位的,也就是以上说的“指令之间指令条数”。

==> 停机指令

( 11)halt

111111

功能:停机;不改变

三.

实验原理

00000000000000000000000000(26 位 )

PC 的值, PC 保持不变。

单周期 CPU 指的是一条指令的履行在一个时钟周期内达成,

而后开始下一条指令的

两个相

假如晶振的

履行, 即一条指令用一个时钟周期达成。

输出没有经过分频就直接作为

电平从低到高变化的瞬时称为时钟上涨沿,

邻时钟上涨沿之间的时间间隔称为一个时钟周期。时钟周期一般也称振荡周期(

)

CPU 的工作时钟,则时钟周期就等于振荡周期。若振荡周期经二分频后形成

时钟脉冲信号作为 CPU 的工作时钟,这样,时钟周期就是振荡周期的两倍。

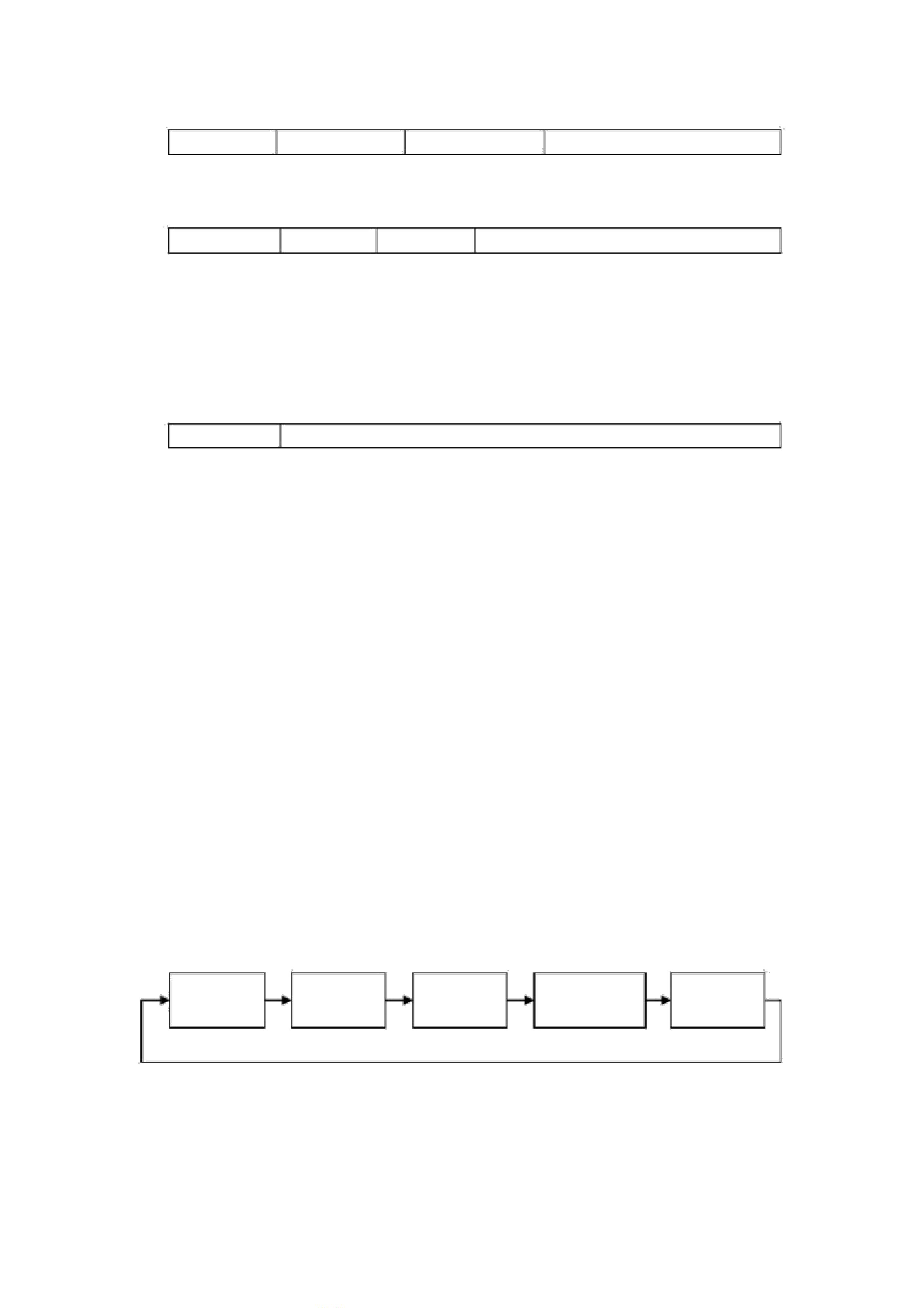

CPU 在办理指令时,一般需要经过以下几个步骤:

(1) 取指令 ( IF ) :依据程序计数器 PC 中的指令地址, 从储存器中拿出一条指令, 同时,

PC ,自然获得的“地址”需要做些变换才送入

PC 。

PC 依据指令字长度自动递加产生下一条指令所需要的指令地址,但碰到“地址转移”指令

时,则控制器把“转移地址”送入

(2) 指令译码 ( ID ) :对取指令操作中获得的指令进行剖析并译码, 确立这条指令需要达成

的操作,进而产生相应的操作控制信号,用于驱动履行状态中的各样操作。

(3) 指令履行 ( EXE) :依据指令译码获得的操作控制信号,详细地履行指令动作,而后

转移到结果写回状态。

(4) 储存器接见 ( MEM) :所有需要接见储存器的操作都将在这个步骤中履行,该步骤

给出储存器的数据地址, 把数据写入到储存器中数据地址所指定的储存单元或许从储存器中

获得数据地址单元中的数据。

(5)

器中。

单周期 CPU ,是在一个时钟周期内达成这五个阶段的办理。

取指令

IF

指令译码

ID

指令履行

EXE

储存器接见

MEM

结果写回

WB

结果写回 ( WB) :指令履行的结果或许接见储存器中获得的数据写回相应的目的存放

图 1 单周期 CPU 指令办理过程

单周期 CPU 设计实验精选报告

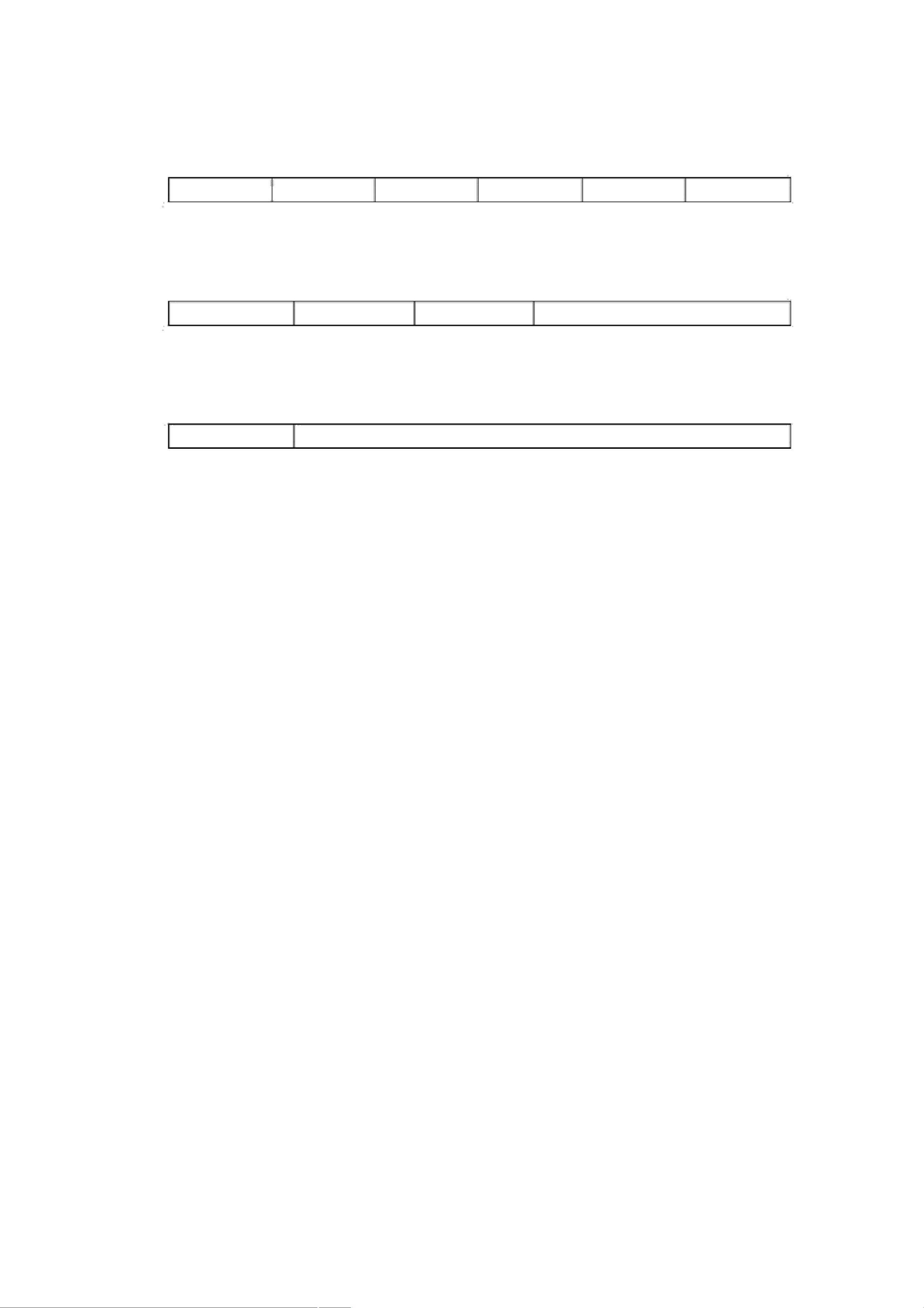

MIPS32 的指令的三种格式:

R 种类:

31 26 25 21 20 16 15 11 10 6 5 0

op

6 位

I 种类:

rs

5

位 5

rt

位

rd

5 位

sa

5 位

func

6 位

31 26 25 21 20 16 15 0

op

6 位 5

rs

位

rt

5 位

immediate

位

16

J 种类:

31 26 25

op

6 位

0

address

26

位

此中,

op :为操作码;

rs :为第 1 个源操作数存放器,存放器地址(编号)是

rd :为目的操作数存放器,存放器地址(同上)

sa :为位移量( shift amt

func :为功能码,在存放器种类指令中(

;

00000~11111 , 00~1F ;

rt :为第 2 个源操作数存放器,或目的操作数存放器,存放器地址(同上)

),移位指令用于指定移多少位;

;

R 种类)用来指定指令的功能;

有符号的算术操作数、

immediate :为 16 位立刻数, 用作无符号的逻辑操作数、

的有符号偏移量;

数据加

载( Laod )/ 数据保留( Store )指令的数据地址字节偏移量和分支指令中相对程序计数器

( PC )

address

:为地址。

剩余15页未读,继续阅读

资源评论

xxpr_ybgg

- 粉丝: 6425

- 资源: 3万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功